www.ti.com

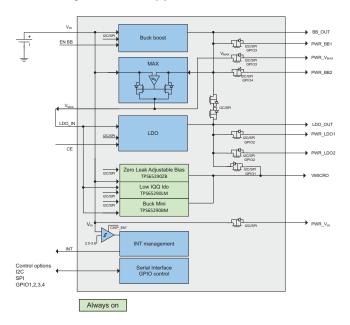

# LOW QUIESCENT CURRENT, MULTI-MODE PMIC FOR BATTERY POWERED, ENERGY HARVESTING APPLICATIONS

Check for Samples: TPS65290

#### **FEATURES**

- Operating Input Voltage Range: 2.2 V to 5 V

- 500-mA Buck-Boost Converter, Stand-Alone Operation or Serial Bus Controlled

- PFM/PWM Operation With Forced PWM Option

- 150 mA LDO

- Stand-Alone or Serial Bus (SPI or I2C)

Controlled

- Two Power Distribution Switches Powered from Buck-Boost Output

- One Power Distribution Switch Powered from the Maximum of Buck Boost or Battery Input

- Two Power Distribution Switches Powered from LDO Output

- One Power Switch Powered from Battery Input

- One Power Switch to Connect BB Output to LDO Output and Improve System Efficiency

- Automatic Power Max Function Between Battery Supply and Buck-Boost With Smart Capabilities to Maximize System Energy Management

- Low Power Always-On Bias Supply for Microcontroller Sleep Mode With Three Factory Selectable Options:

- 10-mA, 100-nA IDDQ Deep Sleep Zero Leakage Current Bias Controller With Pre-Set Voltage

- 10-mA, 400-nA IDDQ LDO<sub>MINI</sub>

- 30-mA, 300-nA IDQQ Buck<sub>MINI</sub>

- Input Voltage Recovery Comparator With Selectable Threshold

- Factory Selectable SPI/I2C Interface

- -40°C to 85°C Ambient Temperature Range

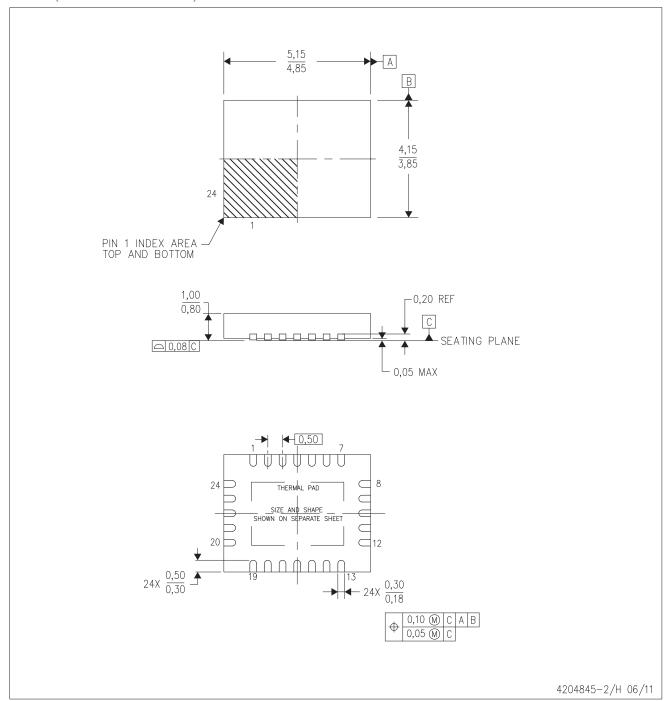

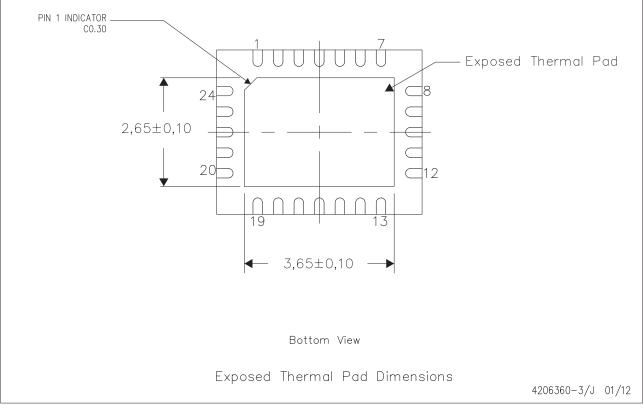

- 24-Pin RHF (QFN) Package

#### **APPLICATIONS**

- Low Power, Energy Harvesting Systems

- Battery Powered Applications

#### DESCRIPTION

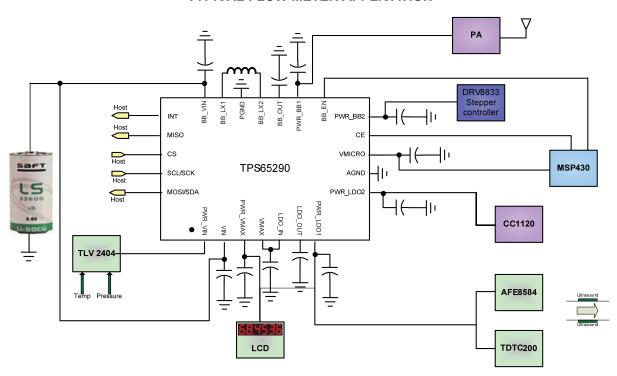

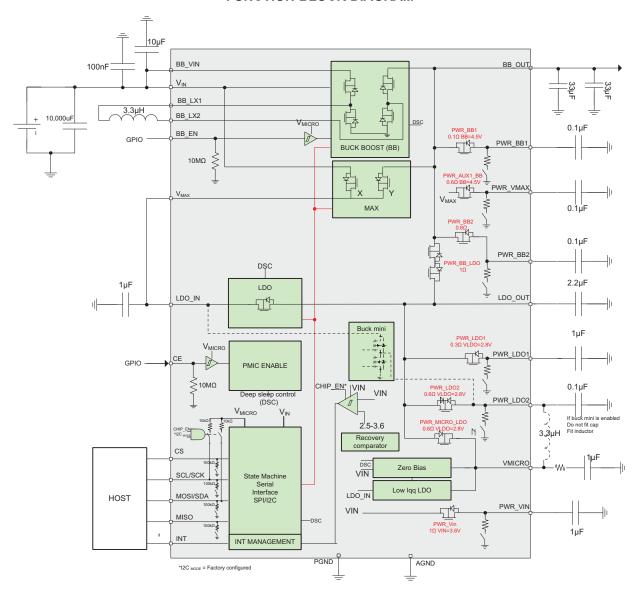

TPS65290 is a PMIC designed to operate in applications dependent on efficient power management over a wide range of system load conditions ranging from fractions of a microamp to a few hundred miliamps. The device operates over a wide 2.2-V to 5-V input-voltage range and incorporates a very low quiescent current always-on power supply, a 500-mA buck/boost converter, a 150-mA low dropout regulator and 8 power distribution switches. The always-on supply features three different factory selectable options: 30mA buck converter with 300-nA quiescent current. 10-mA LDO with 400-nA quiescent current and 10-mA Zero IDDQ drop with 100-nA quiescent current. The buck-boost converter employs PFM/PWM operation with forced PWM option, for maximum overall efficiency. The switches can be used to support different configurations for the various loads supported by the TPS65290. For energy harvesting applications, a programmable input voltage monitor is integrated to allow for connection and disconnection of the different power blocks and switches without the intervention of the master processor.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

# **DESCRIPTION (CONTINUED)**

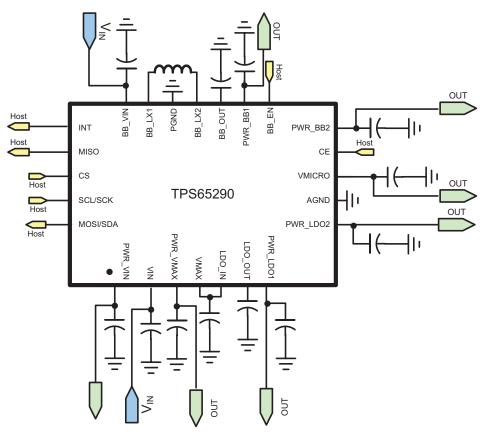

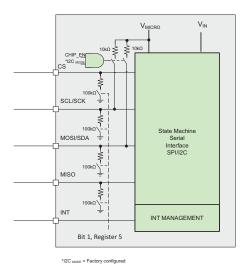

To maximize control flexibility, the TPS65290 includes a factory-selectable choice between SPI and  $I^2C$  interfaces. To minimize PC board footprint and reduce bill of materials (BOM) components and cost, the PMIC internally includes resistive dividers (boost/buck, LDO,  $V_{IN}$  monitor);  $I^2C$  pull-up resistors; SPI pull-down resistors; boost/buck compensation; and interrupt pull-up resistor. Only low-cost ceramic capacitors and power inductors are needed to complete a comprehensive multi-rail solution for efficient flow meter, handheld industrial, fitness and other long-term data-acquisition systems.

# **ORDERING INFORMATION**

| DEVICE                    |            | FEATURES     |                     |                      |     |     |      |                |              |

|---------------------------|------------|--------------|---------------------|----------------------|-----|-----|------|----------------|--------------|

| TPS65290                  | MARKING    | ZERO<br>LEAK | LDO <sub>MINI</sub> | BUCK <sub>MINI</sub> | SPI | I2C | GPIO | PART NUMBE     | ĒR           |

| with zero bias            | TPS65290ZB | V            |                     |                      | 2   |     |      | TPS65290ZBRHFR | reel of 3000 |

| IDQQ                      | 1F3032902B | •            |                     |                      | ٧   |     |      | TPS65290ZBRHFT | reel of 250  |

| with LDO                  | TPS65290LM |              |                     | 1                    |     |     |      | TPS65290LMRHFR | reel of 3000 |

| with LDO <sub>MINI</sub>  | 1F305290LW |              | v                   |                      | V   |     |      | TPS65290LMRHFT | reel of 250  |

| with heal                 | TDCCEOODM  |              |                     | ا                    | 2   |     |      | TPS65290BMRHFR | reel of 3000 |

| with buck <sub>MINI</sub> | TPS65290BM |              | ٧                   | ٧                    | V   |     |      | TPS65290BMRHFT | reel of 250  |

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

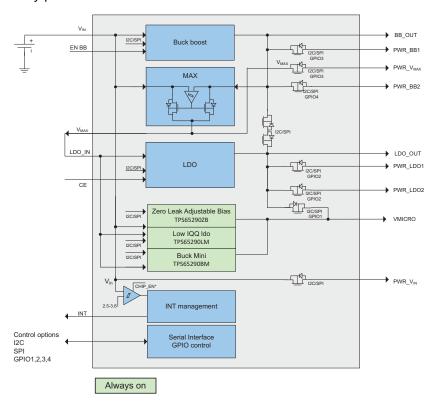

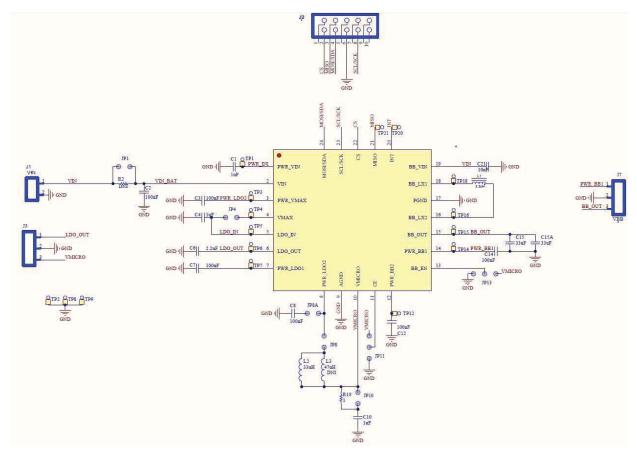

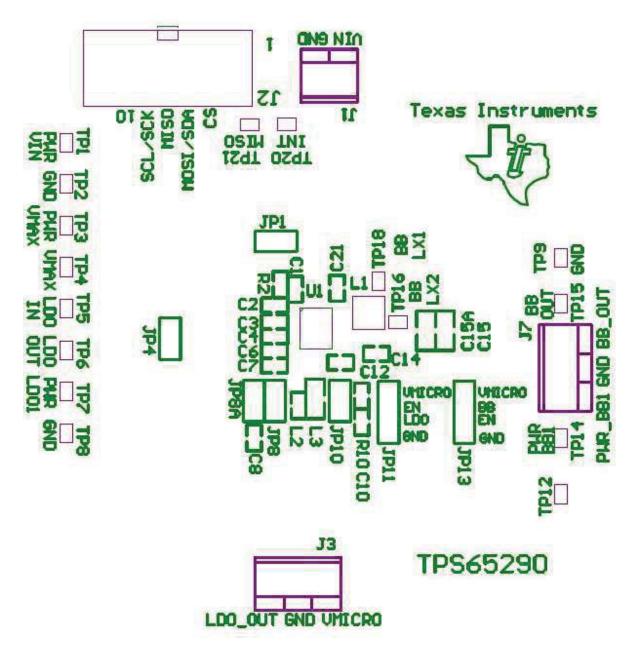

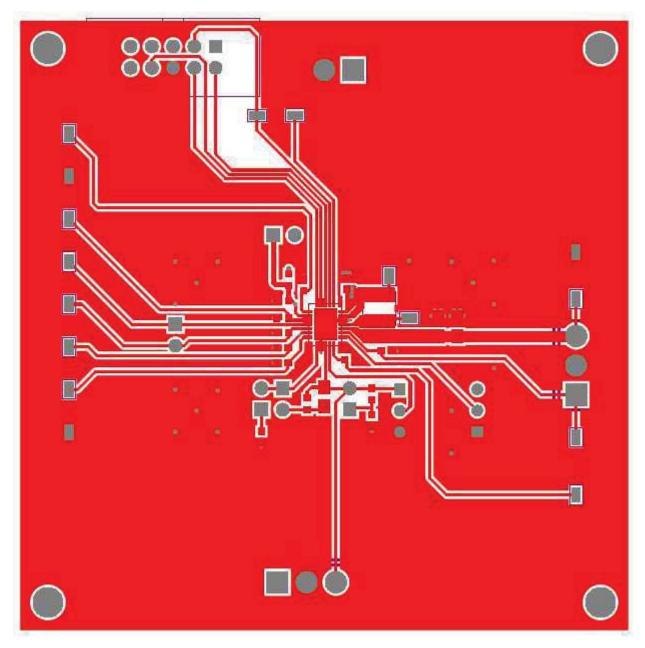

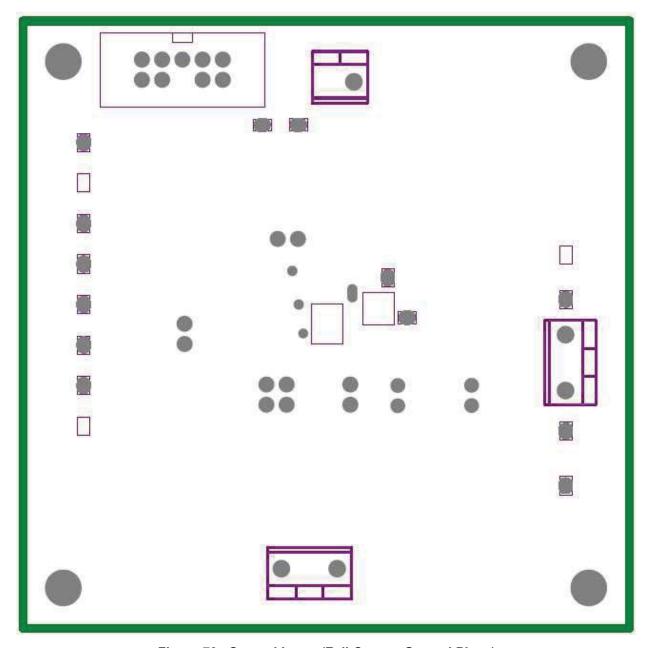

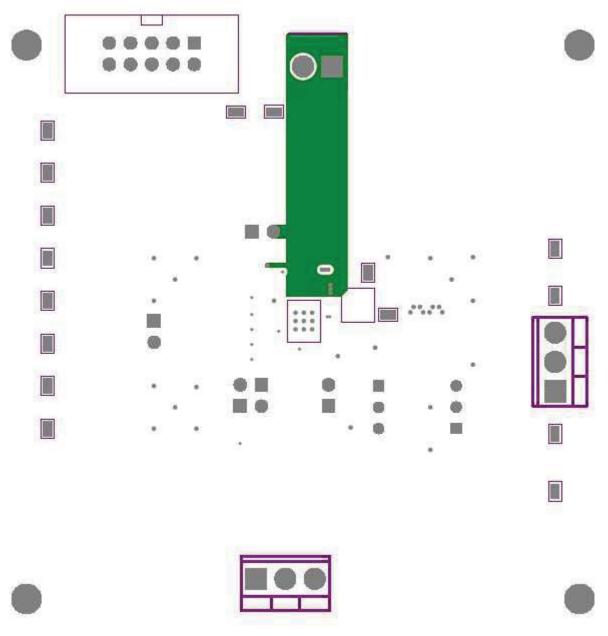

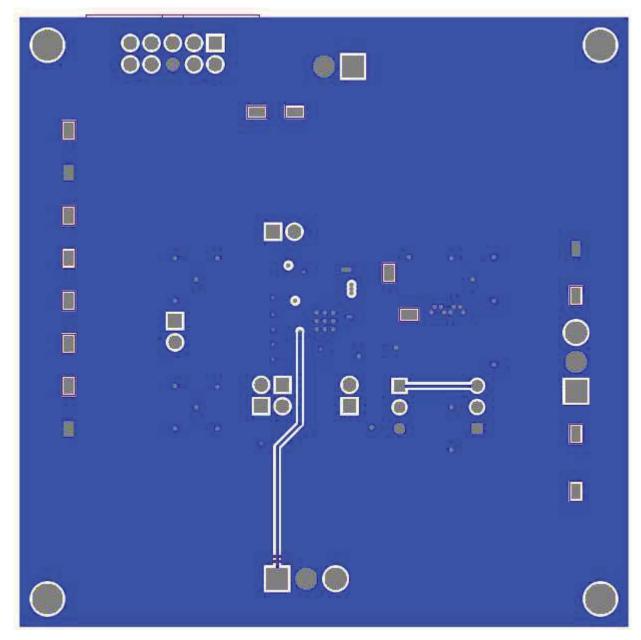

#### **TYPICAL APPLICATION**

# **TYPICAL FLOW METER APPLICATION**

#### **FUNCTION BLOCK DIAGRAM**

| BLOCK                                                    | FUNCTIONALITY                            |     |                                                                                                                                                                          | POWER SAVING OPTIONS                               |                                                                    |       |

|----------------------------------------------------------|------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------|-------|

| BLUCK                                                    |                                          | Reg | Bit                                                                                                                                                                      |                                                    | Reg                                                                | Bit   |

|                                                          | Enable                                   | [0] | [0]                                                                                                                                                                      | PFM/PWM mode                                       | [3]                                                                | [6]   |

| Buck boost                                               | Set voltage                              | [3] | [0,5]                                                                                                                                                                    |                                                    |                                                                    |       |

|                                                          | UVLO disable                             | [3] | [5]                                                                                                                                                                      |                                                    | [2] [5, [6] [6] [6] [7] [6] [7] [7] [7] [7] [7] [7] [7] [7] [7] [7 |       |

| LDO                                                      | Enable                                   | [0] | [1]                                                                                                                                                                      |                                                    |                                                                    |       |

| LDO                                                      | Set voltage                              | [4] | [0,4]                                                                                                                                                                    |                                                    |                                                                    |       |

| Zero drop, LDO <sub>MINI</sub> ,<br>BUCK <sub>MINI</sub> | Set voltage                              | [2] | [0,3]                                                                                                                                                                    |                                                    |                                                                    |       |

| BUCK <sub>MINI</sub> low and high current mode           | Operation Mode                           | [2] | [5,4]                                                                                                                                                                    | Low current mode (for standby operation)           | [2]                                                                | [5,4] |

| MAX                                                      | Latch on turn-off                        | [3] | [7]                                                                                                                                                                      | Coo V entine costion                               |                                                                    |       |

| IVIAA                                                    | Turn-on options                          | [6] | [6,7]                                                                                                                                                                    | See V <sub>MAX</sub> options section               |                                                                    |       |

| December comporator                                      | Set falling voltage                      | [6] | [5,3]                                                                                                                                                                    | Enable/Disable                                     | [8]                                                                | [0]   |

| Recovery comparator                                      | Set rising voltage                       | [6] | [0] [0] P [3] [0,5] [3] [5,5] [0] [1] [4] [0,4] [2] [0,3] [2] [5,4] Low current n [3] [7] See N [6] [6,7] [6] [5,3] [6] [0,2] [7] [1] F [7] [0] [7] [2,7] Power switches | Enable/Disable                                     |                                                                    |       |

|                                                          | Frable (DD LDC DAT V                     | [0] | [2,7]                                                                                                                                                                    | Enable/disable pull-down                           | [5]                                                                | [1,7] |

| Power switches                                           | Enable (BB, LDO, BAT, V <sub>MAX</sub> ) | [7] | [1]                                                                                                                                                                      | Fast/slow turn-on                                  | [5]                                                                | [0]   |

|                                                          | Enable (PWR_BB_LDO)                      | [7] | [0]                                                                                                                                                                      |                                                    |                                                                    |       |

| Interruption management (INT)                            | INT status and masking                   | [7] | [2,7]                                                                                                                                                                    | Power switches automatic disable when INT asserted | [8]                                                                | [1,7] |

| Bandgap                                                  |                                          |     |                                                                                                                                                                          | Enable/disable                                     | [4]                                                                | [5]   |

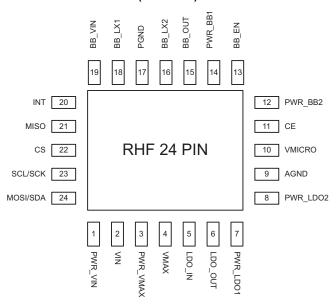

#### **PIN OUT**

# RGE PACKAGE (TOP VIEW)

# **TERMINAL FUNCTIONS**

| NAME     | NO. | I/O | DESCRIPTION                                                                                                                                                                                                                                                         |

|----------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PWR_VIN  | 1   | 0   | Power for system output from Vin                                                                                                                                                                                                                                    |

| VIN      | 2   | I   | Battery supply                                                                                                                                                                                                                                                      |

| PWR_VMAX | 3   | 0   | Switch Controlled supply connected to VMAX. Decouple with a ceramic capacitor                                                                                                                                                                                       |

| VMAX     | 4   | 0   | This pin shows the maximum of VBAT or VBB. Decouple with a 1µF ceramic capacitor                                                                                                                                                                                    |

| LDO_IN   | 5   | I   | LDO input. Decouple this pin with a 2.2µF ceramic capacitor                                                                                                                                                                                                         |

| LDO_OUT  | 6   | 0   | LDO output. Decouple this pin with a 2µF ceramic capacitor                                                                                                                                                                                                          |

| PWR_LDO1 | 7   | 0   | Switch Controlled supply connected to LDO output. Decouple with a ceramic capacitor.                                                                                                                                                                                |

| PWR_LDO2 | 8   | 0   | Switch Controlled supply connected to LDO output. Decouple with a ceramic capacitor.                                                                                                                                                                                |

| AGND     | 9   |     | Analog ground connection. Connect to PGND and power Pad.                                                                                                                                                                                                            |

| VMICRO   | 10  | 0   | Microcontroller supply                                                                                                                                                                                                                                              |

| CE       | 11  | I   | When low the PMIC is in deep sleep and BIAS supply to the micro is enabled. The Interrupt output is disabled with a pull down termination. When high, the I2C/SPI is active; the internal switches can be operated, along with the interrupt logic, and Boost/Buck. |

| PWR_BB2  | 12  | 0   | Switch Controlled supply connected to BB output. Decouple with a 1µF ceramic capacitor.                                                                                                                                                                             |

| BB_EN    | 13  | ı   | Buck-Boost converter enable pin                                                                                                                                                                                                                                     |

| PWR_BB1  | 14  | 0   | Switch Controlled supply connected to BB output. Decouple with a 1µF ceramic capacitor.                                                                                                                                                                             |

| BB_OUT   | 15  | 0   | Buck-Boost converter output                                                                                                                                                                                                                                         |

| BB_LX2   | 16  | 0   | Buck-boost Boost converter switching node                                                                                                                                                                                                                           |

| PGND     | 17  |     | Power ground connection. Connect to AGND and power pad.                                                                                                                                                                                                             |

| BB_LX1   | 18  | 0   | Buck-boost Boost converter switching node                                                                                                                                                                                                                           |

| BB_VIN   | 19  | I   | Input pin to Buck-Boost converter                                                                                                                                                                                                                                   |

| INT      | 20  | 0   | Push-pull output, asserted when low                                                                                                                                                                                                                                 |

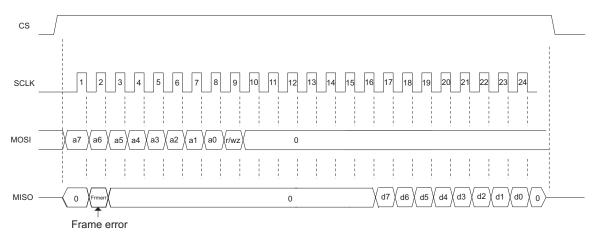

| MISO     | 21  | 0   | Serial Data Transmit interface (Master Input Slave Output)                                                                                                                                                                                                          |

| CS       | 22  | I   | SPI bus Chip Select (active high) when SPI enabled                                                                                                                                                                                                                  |

| SCL/ SCK | 23  | I   | Serial Data Clock (SPI and I2C)                                                                                                                                                                                                                                     |

| MOSI/SDA | 24  | I   | Serial Data Receive interface (Master Output Slave Input) for SPI and I2C                                                                                                                                                                                           |

# **TERMINAL FUNCTIONS (continued)**

| NAME      | NO. | I/O | DESCRIPTION                                                                                        |

|-----------|-----|-----|----------------------------------------------------------------------------------------------------|

| POWER PAD |     |     | Connect the pad to AGND, PGND and PCB GND. Thermal pad does not have electrical connections to IC. |

#### **OUTPUTS AND OPERATIONAL RANGE**

| TYPE                                        | V <sub>OUT</sub> (V)                                             | DEFAULT                               | I <sub>O</sub> MAX<br>(mA) | SET ACCURACY   | FEATURES                                        |

|---------------------------------------------|------------------------------------------------------------------|---------------------------------------|----------------------------|----------------|-------------------------------------------------|

| Buck Boost                                  | 1.0-5V, ~200mV steps                                             | 4.06V                                 | 500                        | 3%             |                                                 |

| LDO                                         | 0.8V for external divider 1.0-4.0V,~ 100mV steps                 | 2.8V                                  | 150                        | 4%             |                                                 |

|                                             | 0.6-2.0V Selective drop from battery voltage, 8 steps adjustment | Vin-1.4                               | 10                         | 10% at 25°C    | No IDQQ                                         |

| Low bias supply                             | 1.8-3.3 V 200mV steps                                            | 2.2V                                  | 10                         | 5%             | Low Iqq LDO                                     |

|                                             | 1.8-3.3V 200mV steps                                             | 2.2V                                  | 30                         | 5%             | Low Iqq Buck                                    |

| Power switches powered                      | PWR_BB1                                                          | Disabled                              | 800                        | 100 mΩ switch  | 1kΩ pull-down Single P                          |

| from BB output                              | PWR_BB2                                                          | Disabled                              | 350                        | 600 mΩ switch, | mosfet                                          |

| Power switches powered from VMAX            | PWR_VMAX                                                         | Disabled                              | 250                        | 600 mΩ switch, | 1kΩ pull-down Single P mosfet                   |

|                                             | PWR_LDO2                                                         | Disabled                              | 250                        | 600 mΩ switch. | 1kΩ pull-down Single P                          |

| Power switches powered                      | PWR_MICRO_LDO                                                    | Disabled                              | NA                         | 600 mg switch, | mosfet                                          |

| from LDO output                             | PWR_LDO1                                                         | Disabled                              | 250                        | 300 mΩ         | 1kΩ pull-down Single P mosfet                   |

| Power switch connecting output of BB to LDO | PWR_BB_LDO                                                       | Disabled                              | 250                        | 1.0 Ω          | 1kΩ pull-down Back to back P mosfets            |

| Power switch powered from battery           | PWR_Vin                                                          | Disabled                              | 100                        | 1.0 Ω          | 1kΩ pull-down Single P mosfet                   |

| Danis and a second                          | 1.7-2.4V 100mV steps falling edge                                | 2.0V                                  | NIA                        | 3%             |                                                 |

| Recovery comparator                         | 2.4-3.1V 100mV steps rising edge                                 | 2.4V                                  | NA                         | 3%             |                                                 |

| MAX (Analog multiplexer)                    | Highest of BB and LDO                                            | NA                                    | 150                        | NA             | Configurable for turn-on and turn-off operation |

| INT (maskable)                              |                                                                  | All switches disabled by interruption |                            |                |                                                 |

# **ABSOLUTE MAXIMUM RATINGS (1)**

over operating free-air temperature range (unless otherwise noted)

|                  | BB_VIN, BB_OUT, BB_FB, LDO_IN, PWR_BB2. PWR_VMAX | -0.3 to 7   | V  |

|------------------|--------------------------------------------------|-------------|----|

|                  | BB_LX1, BB_LX2                                   | –1 to 7     | V  |

|                  | Any other pin                                    | -0.3 to 5.5 | V  |

|                  | AGND, PGND                                       | -0.3 to 0.3 | V  |

| $T_{J}$          | Operating junction temperature range             | -40 to 125  | °C |

| T <sub>STG</sub> | Storage temperature range                        | -55 to 150  | °C |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute—maximum—rated conditions for extended periods may affect device reliability.

# RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|                 |                                                       | MIN | NOM | MAX | UNIT |

|-----------------|-------------------------------------------------------|-----|-----|-----|------|

| BB_VIN,<br>VBAT | Input operating voltage BOOST CONVERTER               | 1.8 | 3.6 | 5   | V    |

| LDO_VIN         | Input operating voltage LDO (V <sub>OUT</sub> = 2.8V) | 3   |     | 5   | V    |

| T <sub>A</sub>  | Ambient temperature                                   | -40 |     | 125 | °C   |

# ELECTROSTATIC DISCHARGE (ESD) PROTECTION(1)

|                           | MIN  | MAX | UNIT |

|---------------------------|------|-----|------|

| Human body model (HBM)    | 2000 |     | V    |

| Charge device model (CDM) | 500  |     | V    |

(1) SW\_OUT1/2 pins' human body model (HBM) ESD protection rating 4 kV, and machine model (MM) rating 200V.

# **DISSIPATION RATINGS**

| PACKAGE | θ <sub>JC</sub> (°C/W) | θ <sub>JA</sub> (°C/W) | T <sub>A</sub> = 25°C<br>Power Rating (W) | T <sub>A</sub> = 85°C<br>Power Rating (W) |

|---------|------------------------|------------------------|-------------------------------------------|-------------------------------------------|

| RHF     | 29                     | 30.6                   | 3.26                                      | 1.30                                      |

# **ELECTRICAL CHARACTERISTICS**

$T_J$  = -40°C to 125°C,  $V_{BAT}$  = 3.6 V (unless otherwise noted)

|                                       | PARAMETER                                                                                             | TEST CONDITIONS                                                                | MIN | TYP  | MAX | UNIT |

|---------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-----|------|-----|------|

| INPUT SUPPLY UV                       | LO AND INTERNAL SUPPLY                                                                                |                                                                                |     |      |     |      |

| $V_{BAT}$                             | Input voltage range for all blocks to be operational                                                  |                                                                                | 2.2 |      | 5   | V    |

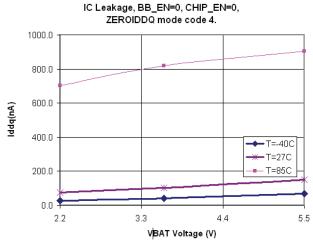

|                                       |                                                                                                       | Zero bias mode                                                                 |     | 100  |     |      |

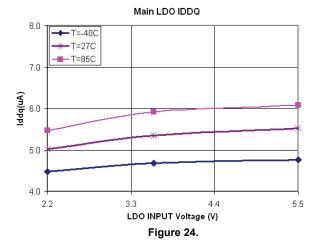

|                                       |                                                                                                       | LDO <sub>MINI</sub> mode                                                       |     | 400  |     |      |

| IDDo                                  | Quiescent current always on blocks<br>Factory configured                                              | BUCK <sub>MINI</sub> mode                                                      |     | 300  |     | nA   |

| u                                     | CHIP_EN=0                                                                                             | V <sub>IN</sub> = 3.6V LDO enabled                                             |     | 5    |     |      |

|                                       |                                                                                                       | $V_{\rm IN}$ = 3.6V, BB enabled $V_{\rm BB\_OUT}$ = 4.5V PFM mode              |     | 40   |     |      |

| RECOVERY VOLTA                        | AGE COMPARATOR                                                                                        |                                                                                |     |      |     |      |

| COMP                                  | Threshold voltage serial interface                                                                    | Rising V <sub>IN</sub> 8 steps 0.1V threshold                                  | 2.4 |      | 3.1 | V    |

| COMP <sub>RVLEVEL</sub>               | selectable                                                                                            | Falling V <sub>IN</sub> 8 steps 0.1V threshold                                 | 1.7 |      | 2.4 | v    |

| COMP <sub>RVACCURACY</sub>            | Comparator accuracy                                                                                   |                                                                                |     | 3    |     | %    |

| IQQ <sub>COMPRV</sub>                 |                                                                                                       | Buck boost enabled                                                             |     | 10   |     | μA   |

| IQQCOMPRV                             |                                                                                                       | Buck boost disabled                                                            |     | 10   |     | μА   |

| <b>ENABLE PINS (CE</b>                | , BB_EN)                                                                                              |                                                                                |     |      |     |      |

| V <sub>H</sub>                        | Enable high                                                                                           | V <sub>MICRO</sub> = 2.2 TO 2.8V                                               | 1.2 |      |     | V    |

| $V_L$                                 | Enable Low                                                                                            | V <sub>MICRO</sub> = 2.2 TO 2.8V                                               |     |      | 0.4 | V    |

| BUCK-BOOST (BB                        | )                                                                                                     |                                                                                |     |      |     |      |

| V <sub>IN</sub>                       | Input voltage range                                                                                   |                                                                                | 1.8 |      | 5   | V    |

| MINI                                  | Start-up voltage, no load VBB<4.5                                                                     | -40°C ≤ T <sub>A</sub> ≤ 85°C                                                  | 1.8 |      |     | V    |

| VIN <sub>START_UP</sub>               | Start-up voltage, no load VBB>4.5                                                                     | -40°C ≤ T <sub>A</sub> ≤ 85°C                                                  |     | 2.5  |     | V    |

| VIN <sub>SUSTAIN</sub> <sup>(1)</sup> | The minimum input voltage in which the buck-boost converter sustains it's operation after starting up | -40°C ≤ T <sub>A</sub> ≤ 85°C                                                  |     | 1.8  |     | V    |

|                                       | DC output accuracy (PWM mode)                                                                         | T <sub>J</sub> = 25°C                                                          | -3  |      | 3   |      |

| VBB                                   | Maximum line regulation                                                                               | V <sub>IN</sub> = 3 to 3.6V I <sub>OUT</sub> = 300mA                           |     | 0.5  |     | %    |

|                                       | Maximum load regulation                                                                               | I <sub>O</sub> = 100 to 500mA                                                  |     | 0.5  |     |      |

| VBB <sub>OUTRANGE</sub>               |                                                                                                       | 29 steps 0.1V from 1 to 5V                                                     | 1   |      | 5   | V    |

| f                                     | Oscillator frequency                                                                                  |                                                                                |     | 1600 |     | kHz  |

| DUTY <sub>BUCK_MIN</sub>              | Minimum duty cycle in buck mode                                                                       |                                                                                |     | 25   | 30  | %    |

|                                       | Average high side switch current limit                                                                | V <sub>IN</sub> = 3.6 V, T <sub>A</sub> = 25°C                                 |     | 2400 |     | mA   |

| $I_{SW}$                              | High side switch on resistance                                                                        | V <sub>IN</sub> = 3.6 V, T <sub>A</sub> = 25°C                                 |     | 120  |     | mΩ   |

|                                       | Low side switch on resistance                                                                         | V <sub>IN</sub> = 3.6 V, T <sub>A</sub> = 25°C                                 |     | 120  |     | mΩ   |

| t <sub>STR_BB</sub>                   | Startup time                                                                                          | I <sub>OUT</sub> = 150mA, C <sub>OUT</sub> = 2X 4.7μF, V <sub>OUT</sub> = 4.0V |     | 500  |     | μs   |

| LDO                                   |                                                                                                       |                                                                                |     |      |     |      |

| V <sub>LDO_IN</sub>                   | Input voltage range                                                                                   | Full load operation                                                            | 2.2 |      | 5   | V    |

| V <sub>LDO_OUT_RANGE</sub>            |                                                                                                       | 32 steps 0.1V from 1 to 4V                                                     | 1   |      | 4   | V    |

#### (1) Specified by design.

# **ELECTRICAL CHARACTERISTICS (continued)**

$T_J = -40^{\circ}\text{C}$  to 125°C,  $V_{BAT} = 3.6 \text{ V}$  (unless otherwise noted)

|                                    | PARAMETER                                                                        | TEST CONDITIONS                                                                                                                                                                                                                                                                                       | MIN | TYP | MAX | UNIT |

|------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| V <sub>LDO_OUT_ACCURACY</sub>      | DC output accuracy                                                               | $V_{IN}$ = 3.6V, $V_{OUT}$ = 2.8V, $T_J$ = -40°C to 125°C $I_{Load}$ = 5mA                                                                                                                                                                                                                            | -4  |     | 4   | %    |

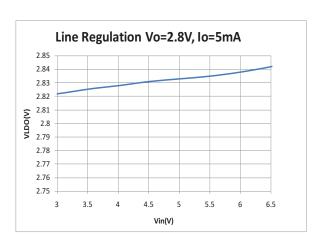

| LDO <sub>LINE_REG</sub>            | Line regulation                                                                  | $3.3V \le V_{IN} \le 6V$ , $V_{OUT} = 2.8V$ , $I_{OUT} = 5mA$                                                                                                                                                                                                                                         | -1  |     | 1   | %    |

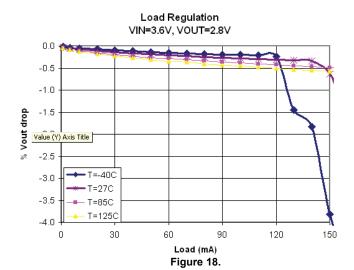

| LDO <sub>LOAD_REG</sub>            | Load regulation                                                                  | V <sub>IN</sub> = 2.2~5V, 0 ≤ I <sub>OUT</sub> ≤ 110mA                                                                                                                                                                                                                                                | -2  |     | 2   | %    |

| V <sub>DROOP</sub>                 | Dropout voltage- allow for 5% output voltage droop                               | V <sub>IN</sub> = 3.6~6V, 0 ≤ I <sub>OUT</sub> ≤ 150mA                                                                                                                                                                                                                                                |     |     | 300 | mV   |

| ICL                                | Output current limit                                                             | V <sub>LDO_OUT</sub> = 2.8V, output voltage shorted                                                                                                                                                                                                                                                   | ·   | 300 |     | mA   |

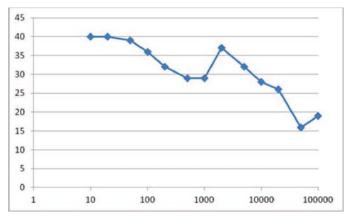

| PSRR                               | Power-supply rejection ratio 10 kHz                                              | V <sub>LDO_OUT</sub> = 2.8V, V <sub>IN</sub> = 3.1V, 150mA loading                                                                                                                                                                                                                                    |     | 28  |     | dB   |

| t <sub>STRLDO</sub>                | Startup time, bandgap already enabled                                            | $C_{OUT}$ = 2.2 $\mu$ F, $V_{OUT}$ = 2.8V, no load                                                                                                                                                                                                                                                    | ·   | 200 |     | μS   |

| MICRO BIAS CIRCL                   | JIT (Different options)                                                          |                                                                                                                                                                                                                                                                                                       |     |     |     |      |

| Zero Leak Adjustab                 | le Bias (TPS65290ZB)                                                             |                                                                                                                                                                                                                                                                                                       |     |     |     |      |

| V <sub>IN</sub>                    | Input voltage range                                                              |                                                                                                                                                                                                                                                                                                       | 2.2 |     | 5   | V    |

| V <sub>MICRO_MIN</sub>             | Minimum output voltage                                                           |                                                                                                                                                                                                                                                                                                       |     | 1.3 |     | V    |

| V <sub>BIAS_DROP</sub>             | Voltage difference between VBAT (pin#4) and Vmicro                               | 9 200mV drop steps from 0.6 to 2V                                                                                                                                                                                                                                                                     | 0.6 |     | 2.0 | V    |

| V <sub>OUT</sub>                   | DC output accuracy measured by V <sub>BIAS_DROP</sub> .                          | T <sub>J</sub> = +25°C, IOUT = 1μA, BAT=3.6V                                                                                                                                                                                                                                                          | -10 |     | 10  | %    |

| ZERO <sub>LOAD_REG</sub>           | Load regulation                                                                  | I <sub>OUT</sub> = 100nA-10mA , T <sub>J</sub> = +25°C, BAT = 3.6V,<br>VMICRO[3:0] = 0000                                                                                                                                                                                                             |     |     | 15  | %    |

| Low IDDQ LDO, aka                  | a LDO <sub>MINI</sub> (TPS65290LM)                                               |                                                                                                                                                                                                                                                                                                       |     |     |     |      |

| V <sub>IN</sub>                    | Input voltage range                                                              |                                                                                                                                                                                                                                                                                                       | 2.2 |     | 5   | V    |

| V <sub>LDO_RANGE</sub>             |                                                                                  | 16 steps 0.2V from 1.8 to 3.3V                                                                                                                                                                                                                                                                        | 1.8 |     | 3.3 | V    |

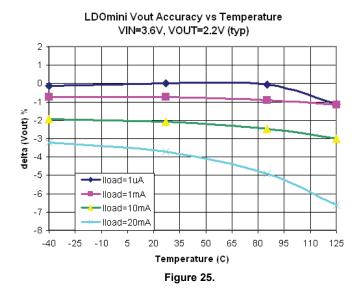

| V <sub>OUT</sub>                   | DC output accuracy                                                               | $T_J = +25^{\circ}C$ , $V_{IN} = 3.6V$ , $I_{OUT} = 1\mu A$                                                                                                                                                                                                                                           | -5  |     | 5   | %    |

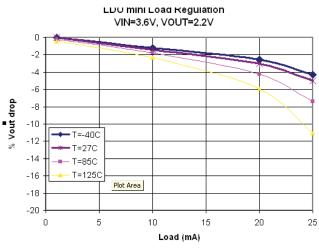

| LDO <sub>LOAD_REG</sub>            | Load regulation                                                                  | 1μA ≤ I <sub>OUT</sub> ≤ 10mA                                                                                                                                                                                                                                                                         | -5  |     | 5   | %    |

| V <sub>DROOP</sub>                 | Dropout voltage– allow for 5% output voltage drop at V <sub>DROOP</sub> .        | V <sub>OUT</sub> = 2.2V, I <sub>OUT</sub> = 10mA                                                                                                                                                                                                                                                      |     |     | 300 | mV   |

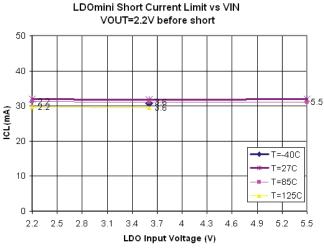

| ICL                                | Output current limit                                                             | V <sub>LDO_OUT</sub> = 2.8V                                                                                                                                                                                                                                                                           | 20  |     | 50  | mA   |

| BUCK <sub>MINI</sub> Internal C    | onverter Hysteretic (TPS65290BM)                                                 |                                                                                                                                                                                                                                                                                                       |     |     | · · |      |

| V <sub>IN BM</sub>                 | Input voltage range                                                              |                                                                                                                                                                                                                                                                                                       | 2.2 |     | 5   | V    |

| I <sub>Load_BM</sub>               | Output load range                                                                |                                                                                                                                                                                                                                                                                                       | 0   |     | 30  | mA   |

| F <sub>SW_BM</sub> (2)             | Buck <sub>MINI</sub> switching frequency                                         | $L_{BM}$ = 33 $\mu$ H, $C_{BM}$ = 1 $\mu$ F, ESR_ $C_{BM}$ = 1 $\Omega$ , No load                                                                                                                                                                                                                     |     | 5   |     | Hz   |

| I <sub>PK_IND</sub> <sup>(2)</sup> | Peak inductor current                                                            | $\begin{split} T_J = +25^{\circ}\text{C} \text{ , } L_{\text{BM}} = 33 \mu\text{H, } C_{\text{BM}} = 1 \mu\text{F,} \\ \text{ESR\_C}_{\text{BM}} = 1\Omega \text{, } V_{\text{IN}} = 3.6 \text{V, } V_{\text{OUT}} = 2.5 \text{V,} \\ I_{\text{OUT}} = 30 \text{mA with high-power mode} \end{split}$ |     | 80  |     | mA   |

| I <sub>PK_IND_STARTUP</sub> (2)    | Peak inductor current during start up                                            | $\begin{split} T_J &= +25^{\circ}C \text{ , } L_{BM} = 33 \mu\text{H, } C_{BM} = 1 \mu\text{F,} \\ &\text{ESR\_C}_{BM} = 1 \Omega,  V_{IN} = 3.6 \text{V, } V_{OUT} = 2.5 \text{V,} \\ I_{OUT} &= 30 \text{mA with high-power mode} \end{split}$                                                      |     | 140 |     | mA   |

| V <sub>BM_RIPPLE</sub> (2)         | Ripple voltage                                                                   | $T_J$ = +25°C , $V_{IN}$ = 3.6V, $V_{OUT}$ = 2.5V), $L_{BM}$ = 33 $\mu$ H, $C_{BM}$ = 1 $\mu$ F, ESR_C <sub>BM</sub> = 1 $\Omega$ ,                                                                                                                                                                   |     | 5   |     | %    |

| POWER SWITCHES                     |                                                                                  |                                                                                                                                                                                                                                                                                                       |     |     |     |      |

| PWR_BB1                            | Distribution switch on resistance from BB_OUT to pin PWR_BB1 (Single P Mosfet)   | V <sub>IN</sub> = 3.6 V, V <sub>BB</sub> = 4.5 V, T <sub>A</sub> = 25°C                                                                                                                                                                                                                               |     | 100 |     | mΩ   |

| PWR_VMAX_<br>V <sub>MAX</sub>      | Distribution switch on resistance from VMAX to pin PWR_VMAX (Single P Mosfet)    | V <sub>IN</sub> = 3.6 V, V <sub>BB</sub> = 4.5 V, T <sub>A</sub> = 25°C                                                                                                                                                                                                                               |     | 600 |     | mΩ   |

| PWR_BB2                            | Distribution switch on resistance from BB_OUT to pin PWR_BB2 (Single P Mosfet)   | V <sub>IN</sub> = 3.6 V, V <sub>BB</sub> = 4.5 V, T <sub>A</sub> = 25°C                                                                                                                                                                                                                               |     | 600 |     | mΩ   |

| PWR_LDO1                           | Distribution switch on resistance from LDO_OUT to pin PWR_LDO1 (Single P Mosfet) | V <sub>IN</sub> = 3.6 V, V <sub>LDO</sub> = 2.8 V, T <sub>A</sub> = 25°C                                                                                                                                                                                                                              |     | 300 |     | mΩ   |

| PWR_LDO2                           | Distribution switch on resistance from LDO_OUT to pin PWR_LDO2 (Single P Mosfet) | V <sub>IN</sub> = 3.6 V, V <sub>LDO</sub> = 2.8 V, T <sub>A</sub> = 25°C                                                                                                                                                                                                                              |     | 600 |     | mΩ   |

#### (2) Specified by design.

# **ELECTRICAL CHARACTERISTICS (continued)**

$T_{\perp}$  = -40°C to 125°C,  $V_{RAT}$  = 3.6 V (unless otherwise noted)

|                       | PARAMETER                                                                                                | TEST CONDITIONS                                                          | MIN                          | TYP MAX                      | UNIT |

|-----------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------|------------------------------|------|

| PWR_MICRO_<br>LDO     | Distribution switch on resistance from LDO_OUT to pin VMICRO (Single P Mosfet)                           | V <sub>IN</sub> = 3.6 V, V <sub>LDO</sub> = 2.8 V, T <sub>A</sub> = 25°C |                              | 600                          | mΩ   |

| PWR_VIN               | Distribution switch on resistance from VIN to pin PWR_VIN (Single P Mosfet)                              | V <sub>IN</sub> = 3.6 V, T <sub>A</sub> = 25°C                           |                              | 1000                         | mΩ   |

| PWR_BB_LDO            | Distribution switch on resistance (internal use only) from BB_OUT to LDO_OUT pin (Back to back P Mosfet) | V <sub>IN</sub> = 3.6 V, V <sub>BB</sub> = 4.5 V, T <sub>A</sub> = 25°C  |                              | 1000                         | mΩ   |

| R <sub>PULLDOWN</sub> | Pull-down resistance (Connection selectable by EEPROM bit)                                               |                                                                          |                              | 1.2                          | kΩ   |

| LOGIC LEVEL O         | JTPUTS (INT, MISO)                                                                                       |                                                                          |                              |                              |      |

| V <sub>OL</sub>       | Output level low                                                                                         | V <sub>MICRO</sub> = 2.2 to 2.8V , I <sub>load</sub> = 1mA               |                              | 0.4                          | V    |

| V <sub>OH</sub>       | Output level high                                                                                        | V <sub>MICRO</sub> =2.2 to 2.8V , I <sub>load</sub> = 1mA                | V <sub>MICRO</sub> - 0.4     |                              | V    |

| LOGIC LEVEL IN        | PUT (CS, MOSI, CLK, SDA SCK )                                                                            |                                                                          |                              |                              |      |

| V <sub>H</sub>        | Input high level                                                                                         | V <sub>MICRO</sub> = 2.2 to 2.8V                                         | 0.67 *<br>V <sub>MICRO</sub> |                              | V    |

| V <sub>L</sub>        | Input low level                                                                                          | V <sub>MICRO</sub> = 2.2 to 2.8V                                         |                              | 0.33 *<br>V <sub>MICRO</sub> | V    |

| V <sub>HYS</sub>      | Input hysteresis                                                                                         |                                                                          | 10                           |                              | mV   |

| R <sub>PULLUP</sub>   | Pull-up resistor to VMICRO<br>When I2C mode enabled                                                      |                                                                          |                              | 10                           | kΩ   |

| R <sub>PULLDOWN</sub> | Pull-down resistor to GND<br>When SPI mode enabled                                                       |                                                                          |                              | 100                          | kΩ   |

| THERMAL SHUT-         | DOWN FOR BUCK BOOST CIRCUIT                                                                              |                                                                          |                              |                              |      |

| T <sub>TRIP_BB</sub>  |                                                                                                          |                                                                          |                              | 141                          | °C   |

| T <sub>HYST_BB</sub>  |                                                                                                          |                                                                          |                              | 12                           | °C   |

| CENTRAL THER          | MAL SHUTDOWN                                                                                             |                                                                          |                              |                              |      |

| T <sub>TRIP_IC</sub>  | Thermal protection trip point                                                                            | Rising temperature                                                       |                              | 160                          | °C   |

| T <sub>HYST IC</sub>  | Thermal protection hysteresis                                                                            |                                                                          |                              | 20                           | °C   |

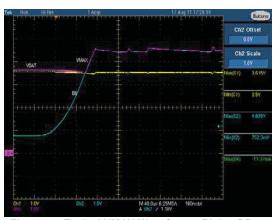

# TYPICAL CHARACTERISTICS (BUCK BOOST)

$T_J = 25^{\circ}C$  (unless otherwise noted)

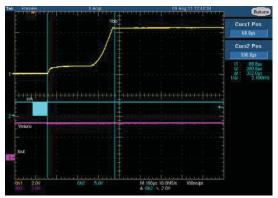

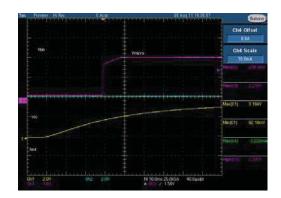

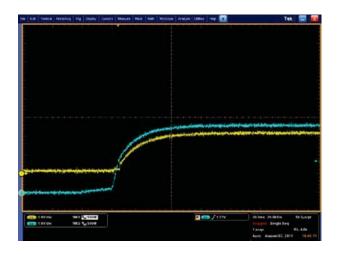

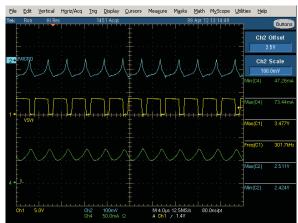

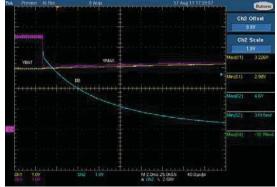

Figure 1. Buck Boost Startup Waveform with I2C Command Ch1: BB output. Ch2: I2C SCLK turns on buck-boost, Ch3: VMICRO. Startup time is 330µs. Buck Boost L and C are per application circuit.

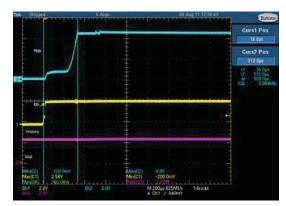

Figure 2. Buck Boost Startup Waveform with BB\_EN Pin Command

Ch2: BB output. Ch1: BB\_EN signal. Ch3: VMICRO. Startup time is 330µs. Buck Boost L and C are per application circuit.

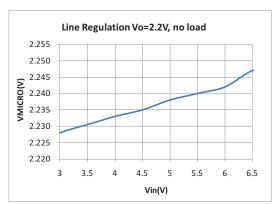

Figure 3. Buck Boost Line Regulation, Boost Mode

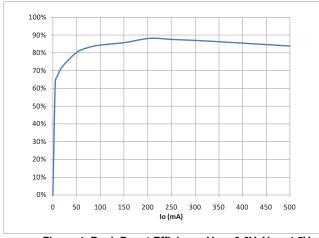

Figure 4. Buck Boost Efficiency  $V_{IN} = 3.6V$ ,  $V_{O} = 4.5V$

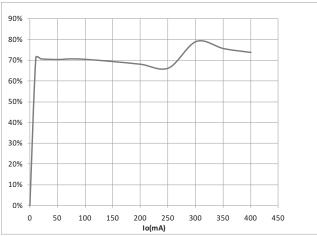

Figure 5. Buck Boost Efficiency V<sub>IN</sub> = 2.5V, V<sub>O</sub> = 4.5V

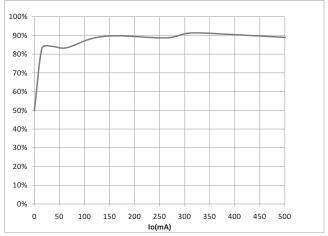

Figure 6. Buck Boost Efficiency  $V_{IN} = 3.6V$ ,  $V_O = 2.8V$

# TYPICAL CHARACTERISTICS (BUCK BOOST) (continued)

#### $T_J = 25^{\circ}C$ (unless otherwise noted)

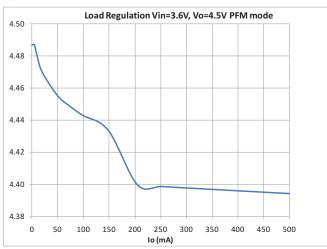

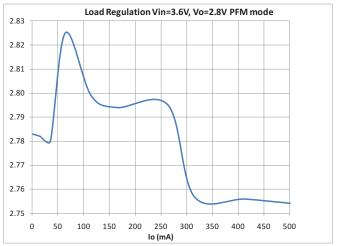

Figure 7. Buck Boost Load Regulation

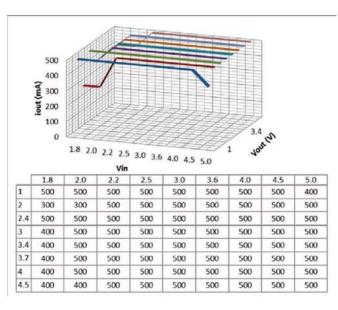

Figure 8. Buck Boost Load Regulation Buck Boost Loading 85°C Ambient V<sub>BB</sub> < 4.5V

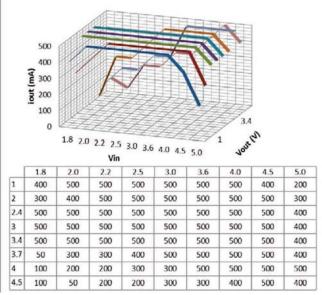

Figure 9. Buck Boost Loading 25°C Ambient V<sub>BB</sub> < 4.5V

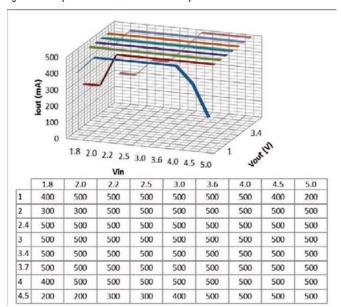

Figure 10. Buck Boost Loading -40°C Ambient V<sub>BB</sub> < 4.5V

# TYPICAL CHARACTERISTICS (BUCK BOOST) (continued)

#### $T_J = 25^{\circ}C$ (unless otherwise noted)

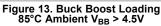

Figure 11. Buck Boost Loading -10°C Ambient V<sub>BB</sub> < 4.5V

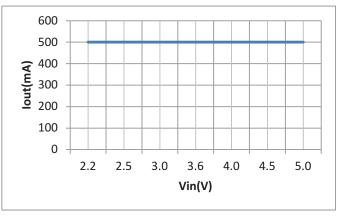

Figure 12. Buck Boost Loading 25°C Ambient V<sub>BB</sub> > 4.5V

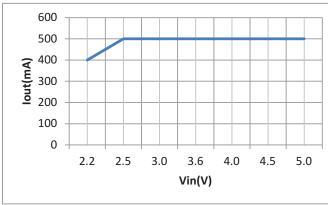

Figure 14. Buck Boost Loading -10°C Ambient V<sub>BB</sub> > 4.5V

Figure 15. Buck Boost Loading -40°C Ambient V<sub>BB</sub> > 4.5V

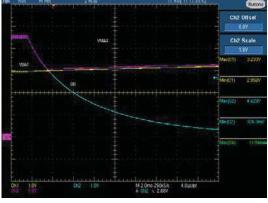

# **TYPICAL CHARACTERISTICS (LDO)**

$T_J = 25^{\circ}C$  (unless otherwise noted)

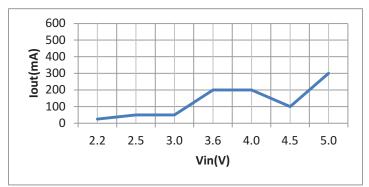

Figure 16.

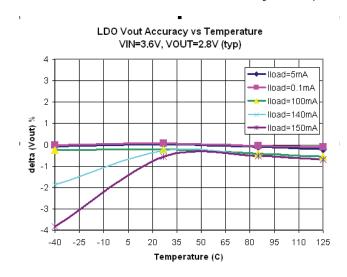

Figure 17.

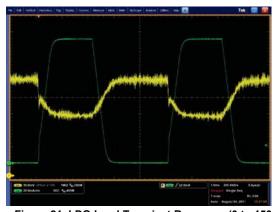

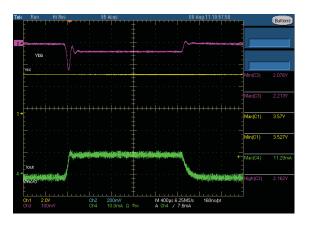

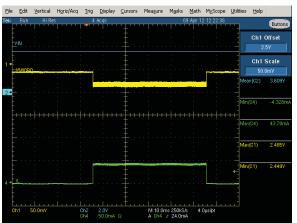

Figure 20. LDO Startup Waveform with I2C Command Ch1: LDO output. Ch 2: I2C SCLK, Ch3: VMICRO, Ch4: VIN current. Startup time is about 200µs.

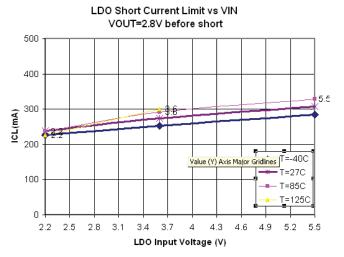

Figure 19.

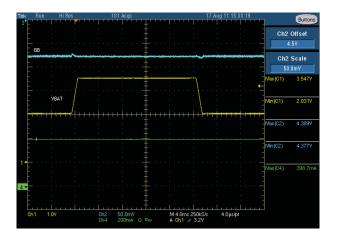

Figure 21. LDO Load Transient Response (0 to 150mA) Ch1: LDO output (10mV/div). Ch4 Load current (20mA/div).

# TYPICAL CHARACTERISTICS (LDO) (continued)

#### $T_J = 25^{\circ}C$ (unless otherwise noted)

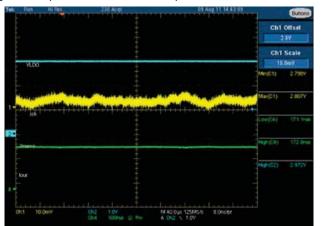

Figure 22. LDO Input to Output Voltage Ch1: LDO output. Ch 2: LDO input, Ch3: Ch4: LDO current

Figure 23. LDO PSRR(dB), 10 to 100kHz LDO output = 2.8V, LDO input = 3.1V, 150mA loading.

# TYPICAL CHARACTERISTICS (LDO<sub>MINI</sub>)

$T_J = 25$ °C (unless otherwise noted)

Figure 26.

# TYPICAL CHARACTERISTICS (LDO<sub>MINI</sub>) (continued)

# $T_J = 25^{\circ}C$ (unless otherwise noted)

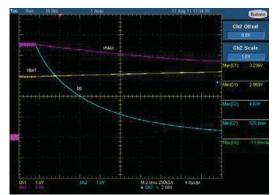

Figure 29. LDO MINI Startup Waveform with VIN Rising Input battery connected to  $27\Omega$  resistor and  $1000\mu F$  capacitor Ch1: VBAT rising. Ch 3: VMICRO (LDO MINI output)

Figure 28. LDO<sub>MINI</sub> Load Transient Response (0 to 10mA) Ch1: VBAT, Ch3: VMICRO (LDO<sub>MINI</sub> output) (100mV/div). Ch4 Load current (10mA/div).

Figure 30.

# TYPICAL CHARACTERISTICS (ZERO IDQQ)

$T_J = 25^{\circ}C$  (unless otherwise noted)

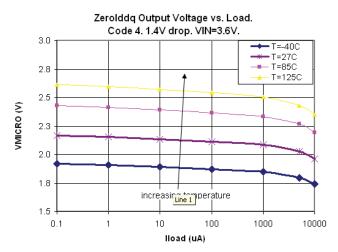

Figure 31.

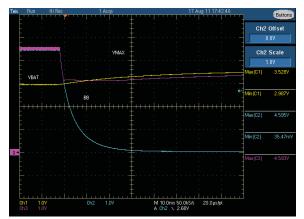

Figure 33. ZEROiddq Startup Waveform with VIN Rising Code 4, 1.4V drop Ch2: VBAT rising. Ch 3: VMICRO (ZEROIDDQ output)

Figure 32. ZEROiddq Load Transient Response (0 to 10mA) Code 4, 1.4V drop. Ch1: VBAT, Ch3: VMICRO (LDO<sub>MINI</sub> output) (100mV/div). Ch4 Load current (10mA/div).

Figure 34.

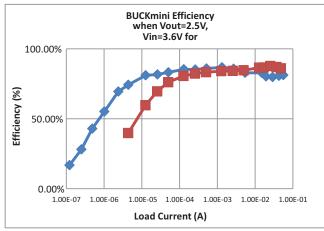

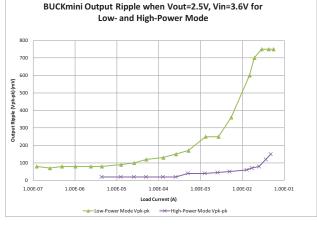

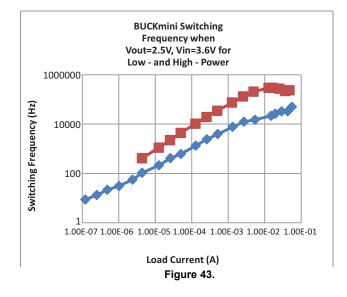

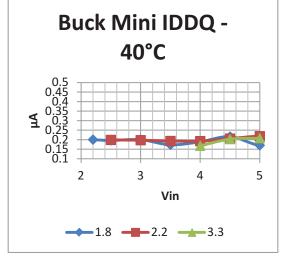

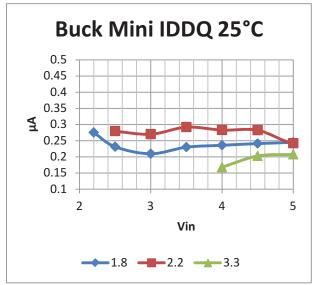

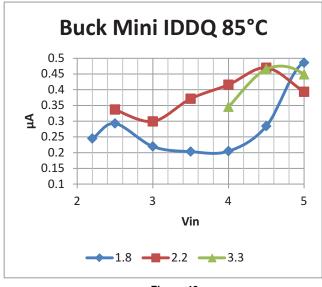

# TYPICAL CHARACTERISTICS (BUCK<sub>MINI</sub>)

$T_J = 25^{\circ}C$  (unless otherwise noted)

Figure 35. BUCK MINI Efficiency  $C_O = 1\mu F$ , ESR =  $1\Omega$ , L =  $33\mu F$  Automatic Mode

Figure 37. BUCK<sub>MINI</sub> Transient Response V<sub>IN</sub> = 3.6V, V<sub>O</sub> = 2.5V 0-50mA Step

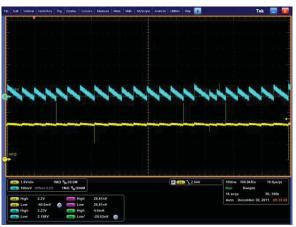

Figure 39. BUCK  $_{\rm MINI}$  Output Ripple  $\rm V_{\rm IN}$  = 3.6V,  $\rm V_{\rm O}$  = 2.5V,  $\rm I_{\rm O}$  = 50mA

Figure 36. BUCK<sub>MINI</sub> Efficiency  $C_O = 100 \mu F$ , L = 33 $\mu F$  Automatic Mode

Figure 38. BUCK<sub>MINI</sub> Output Ripple  $V_{IN} = 3.6V$ ,  $V_{O} = 2.5V$ ,  $I_{O} = 50mA$

Figure 40. BUCK<sub>MINI</sub> Output Ripple  $V_{IN}$  = 3.6V,  $V_{O}$  = 2.5V,  $I_{O}$  = 50mA

# TYPICAL CHARACTERISTICS (BUCK<sub>MINI</sub>) (continued)

# $T_J = 25^{\circ}C$ (unless otherwise noted)

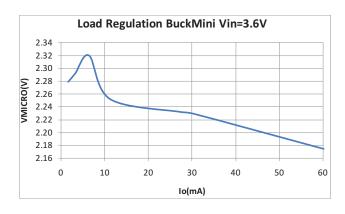

Figure 41.

Figure 42.

Figure 44.

# TYPICAL CHARACTERISTICS (BUCK<sub>MINI</sub>) (continued)

$T_J = 25^{\circ}C$  (unless otherwise noted)

Figure 45.

Figure 46.

# **TYPICAL CHARACTERISTICS (VMAX)**

$T_J = 25^{\circ}C$  (unless otherwise noted)

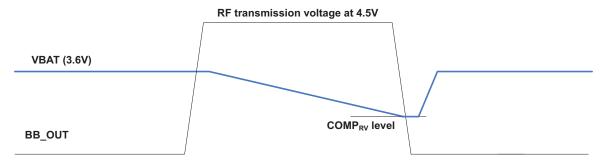

Figure 47. Typical VMAX Waveforms. Rising BB output.

Figure 48. VMAX waveform. Falling BB output. Switch configured for VMAX = MAX(VBAT,VBBout) when BB output is disabled.

Figure 49. VMAX waveform. Falling BB output. Switch configured for VMAX = VBAT when BB output is disabled.

Figure 50. VMAX waveform. Falling BB output. Switch configured for VMAX = MAX(VBAT,VBBout)-diode when BB output is disabled. Note: VMAX is not loaded.

Copyright © 2013, Texas Instruments Incorporated

# TYPICAL CHARACTERISTICS (VMAX) (continued)

$T_J = 25^{\circ}C$  (unless otherwise noted)

Figure 51. VMAX waveform. Falling BB output. Switch is configured for VMAX = MAX(VBAT,BBout). The VMAX comparator turns off automatically when BBout falls below VBAT at BB turn off.

#### **CHOICE OF TPS65290 VERSION AND SERIAL INTERFACE**

Once a voltage higher than 2.2V is applied to the VIN the always on supply will start as per the factory default setting. This will be the only block available within the device and will always stay on as long as the input supply does not drop beyond 2.2V.

There are 3 possible choices of always on supply. The main parameter for choice is the "efficiency" of the supply during sleep mode, mostly processor current.

Figure 52.

## Zero Bias set to V<sub>IN</sub>-1.4

- Takes the least amount of guiescent current

- Provides voltage drops from 0.6 to 2V in 200mV steps

- · Is not a regulated output

- Can be programmed to zero drop or to open circuit

- 10mA max

#### LDO<sub>MINI</sub> set to 2.2V

- · Provides a regulated output

- Can be programmed from 1.8 to 3.3V in 100mV steps

- 10mA max

## BUCK<sub>MINI</sub> set to 2.2V

- Provides a regulated output

- Can be programmed from 1.8 to 3.3V in 100mV steps

- 30mA max

- Output has a ripple content

- Requires additional inductor (0603) and resistor (0402) PWR\_AUX2 switch is disabled (pin becomes switching node)

The chosen serial interface for the part is SPI as I2C lines are open drain lines with internal  $20k\Omega$  pull-up resistors that guarantees 400kHz operation, but also create power losses when any of the bus lines are low. It is expected that operation with SPI will produce less average current consumption when compared to I2C. For I2C/GPIO operation please check with the factory.

#### **FACTORY PROGRAMMED SETTINGS**

The following blocks are programmed in the factory.

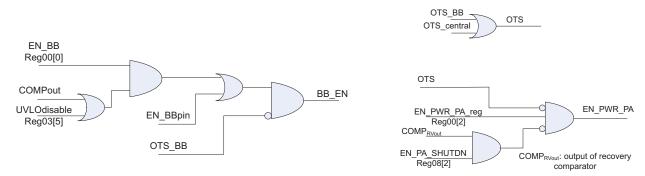

#### **Buck boost**

- Can be enabled or disabled when IC is enabled (can also be enabled with pin 15 high)

- Voltage can be set to

- 1.0 to 3.4V, 200mV steps

- 3.5 to 4.7V, 100mVsteps

- 4.9V, 5.0V

- Forced PWM or PFM (low power mode)

- Input UVLO comparator enabled/disabled. If disabled BB will try to operate with any input voltage higher than 1.8V LDO

- · Can be disabled or enabled when IC is enabled

- Output voltage can be set to 1 to 4.0V, 100mV steps

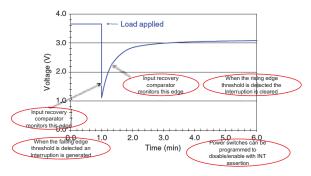

#### Recovery comparator

- · Can be enabled or disabled when IC is enabled

- Falling edge can be set to 1.7 to 2.4V, 100mV. An interruption is generated.

- Rising edge can be set to 2.4 to 3.1V, 100mV. The interruption is released.

#### Power switches

- Can be enabled or disabled when IC is enabled

- Pull-down resistance can be connected or disconnected when IC is enabled

- Power switches can be disabled when an Interruption is generated

- Switches can be turned on at slow or fast speed

#### **USING THE TPS65290**

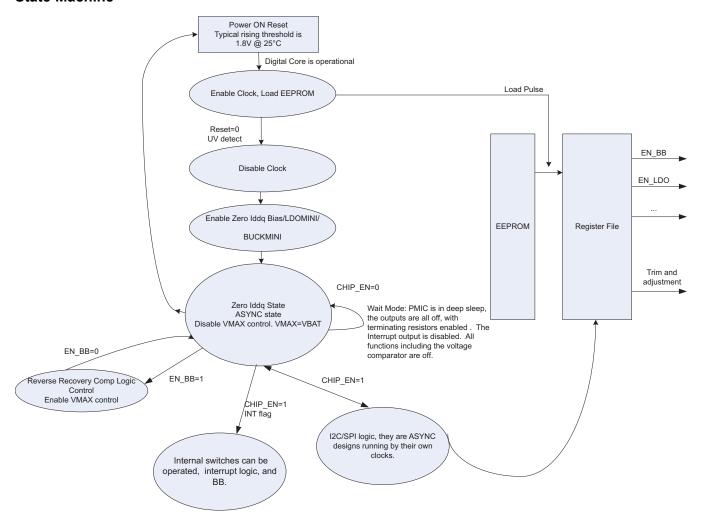

## Power UP and Enabling the IC

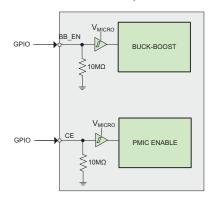

There are two ways of enabling the PMIC by setting the CE or BB\_EN pins. If CE IS disabled only the always on blocks (as per default) and pull-down resistors are enabled by default.

Figure 53. Power UP and Enabling the IC

When CE and BB\_EN are low the PMIC is in deep sleep and bias supply to the micro is enabled. When high, the I2C/SPI is active; the internal switches can be operated, along with the interrupt logic, and Boost/Buck. The Buck boost is enabled either by BB\_EN (high) or EN\_BB bit (1). BB\_EN can be used to enable the buck boost converter without need of the serial interface.

With the serial interface ACTIVE it is possible to enable, disable AND change settings for the power blocks. All changes on registers will be kept as long as the input supply is higher than 1.8V. If power is recycled the registers will be re-loaded with the programmed factory defaults.

## **Band-Gap Enable (Non EEPROM Setting)**

The LDO bandgap is normally disabled to reduce consumption and it is enabled when either of the of LDO,  $LDO_{MINI}$  or  $BUCK_{MINI}$  blocks are enabled. However, to speed up the power-up timing of the LDO it can be enabled in advance (register 4, bit 5)

# **BUCK**<sub>MINI</sub> operation (Non EEPROM setting)

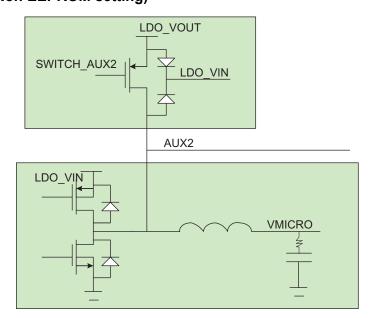

Figure 54.

$BUCK_{MINI}$  is a hysteretic buck converter that can deliver up to 30mA and therefore can be used beyond the sleep mode operation of the micro. When using this block is important to keep the following in mind:

- AUX2 output is not available as this pin is used to connect the external inductor required by the converter.

- If VMICRO has a ceramic capacitor, it is recommend to add a small resistor (0.5 to  $1\Omega$ ) to guarantee a fixed ripple value at the output.

- BUCK<sub>MINI</sub> does not feature a current limit circuit. Overcurrent protection (if needed) needs to be provided externally.

- When used to support loads between 100µA to 1mA there is trade-off between input quiescent current and output ripple. It is suggested to use the settings for low and high power mode (Register 2, Bits [5,4]) to determine which power mode is most suitable for the application. Plots on the characteristics section show the typical trade-off between efficiency and ripple.

- BUCK<sub>MINI</sub> starts at automatic power selection mode. If loading higher than 100μA-1mA is required, set the BUCK<sub>MINI</sub> setting to (Register 2, Bits [5,4]) [11] to reduce ripple.

- Once the loading is removed, set (Register 2, Bits [5,4]) [10] to reduce power consumption

#### BUCK-BOOST OPERATION

#### **Inductor Selection**

To estimate the inductance of the buck-boost converter the following equations can be used:

$$L_1 = (V_{\text{IN MAX}} - V_{\text{OUT}}) \times 0.5 \times (\mu \text{s/A}) \tag{1}$$

$$L_2 = V_{OUT} \times 0.5 \times (\mu s/A)$$

(2)

$L_1$  is used for step down mode operation . VIN is the maximum input voltage.  $L_2$  is used for boost mode operation is calculated. The recommended minimum inductor value is either  $L_1$  or  $L_2$  whichever is higher. As an example, a suitable inductor for generating 3.3V from a Li-ion battery with a battery voltage range from 2.5V up to 4.2V is 2.2 $\mu$ H. The recommended inductor range is between 1.5 $\mu$ H and 4.7 $\mu$ H. In general, this means that at high voltage conversion rates, higher inductor values offer better performance.

The table below shows the recommended inductance for input and output voltage combinations. The highest inductance among the region of interest is recommended.

Figure 55. Recommended Inductance for Input and Output Voltage Combination (μH)

| Vout\Vin | 1.8  | 1.9  | 2    | 2.2  | 2.5  | 3    | 3.6  | 4    | 4.5  | 5    |

|----------|------|------|------|------|------|------|------|------|------|------|

| 1        | 0.4  | 0.45 | 0.5  | 0.6  | 0.75 | 1    | 1.3  | 1.5  | 1.75 | 2    |

| 2        | 1    | 1    | 1    | 0.1  | 0.25 | 0.5  | 0.8  | 1    | 1.25 | 1.5  |

| 2.4      | 1.2  | 1.2  | 1.2  | 1.2  | 0.05 | 0.3  | 0.6  | 0.8  | 1.05 | 1.3  |

| 3        | 1.5  | 1.5  | 1.5  | 1.5  | 1.5  | 1.5  | 0.3  | 0.5  | 0.75 | 1    |

| 3.4      | 1.7  | 1.7  | 1.7  | 1.7  | 1.7  | 1.7  | 0.1  | 0.3  | 0.55 | 0.8  |

| 4        | 2    | 2    | 2    | 2    | 2    | 2    | 2    | 2    | 0.25 | 0.5  |

| 4.5      | 2.25 | 2.25 | 2.25 | 2.25 | 2.25 | 2.25 | 2.25 | 2.25 | 2.25 | 0.25 |

| 5        | 2.5  | 2.5  | 2.5  | 2.5  | 2.5  | 2.5  | 2.5  | 2.5  | 2.5  | 2.5  |

With the chosen inductance value, the peak current for the inductor in steady state operation can be calculated. Equation 3 shows how to calculate the peak current  $I_1$  in step down mode operation and Equation 4 show how to calculate the peak current  $I_2$  in boost mode operation.

$$I_{I} = \frac{I_{OUT}}{0.8} + \frac{V_{OUT} \left(V_{IN\_MAX} - V_{OUT}\right)}{2 \cdot V_{OUT} \cdot f \cdot L}$$

(3)

$$I_{2} = \frac{V_{OUT} \bullet I_{OUT}}{0.8 \bullet V_{IN\_MIN}} + \frac{V_{IN\_MIN} \left(V_{OUT} - V_{IN\_MIN}\right)}{2 \bullet V_{OUT} \bullet f \bullet L}$$

(4)

In both equations f is the switching frequency. The critical current value for selecting the right inductor is the higher value of  $I_1$  and  $I_2$ . It also needs to be taken into account that load transient and error conditions may cause higher inductor currents. This also needs to be taken into account when selecting an appropriate inductor.

The table below shows the recommended inductor current rating for input and output voltage combinations with assumption of 1.6MHz switching frequency, 500mA loading, 3.3µH inductance. The highest current rating among the region of interest is recommended.

Figure 56. Recommended Inductor Current Rating for Input and Output Voltage Combination with 3.3µH Inductor, 1.6MHz Switching Frequency and 500mA load (A)

| Vout\Vin | 1.8  | 1.9  | 2    | 2.2  | 2.5  | 3    | 3.6  | 4    | 4.5  | 5    |

|----------|------|------|------|------|------|------|------|------|------|------|

| 1        | 0.79 | 0.79 | 0.80 | 0.80 | 0.81 | 0.81 | 0.82 | 0.82 | 0.82 | 0.82 |

| 2        | 0.85 | 0.80 | 0.75 | 0.77 | 0.79 | 0.81 | 0.83 | 0.84 | 0.85 | 0.86 |

| 2.4      | 1.04 | 0.98 | 0.93 | 0.84 | 0.76 | 0.79 | 0.82 | 0.84 | 0.85 | 0.86 |

| 3        | 1.32 | 1.25 | 1.19 | 1.08 | 0.94 | 0.75 | 0.80 | 0.82 | 0.84 | 0.86 |

| 3.4      | 1.49 | 1.42 | 1.35 | 1.23 | 1.08 | 0.88 | 0.77 | 0.80 | 0.83 | 0.85 |

| 4        | 1.76 | 1.67 | 1.59 | 1.45 | 1.29 | 1.07 | 0.87 | 0.75 | 0.79 | 0.82 |

| 4.5      | 1.97 | 1.88 | 1.79 | 1.64 | 1.45 | 1.22 | 1.00 | 0.88 | 0.75 | 0.79 |

| 5        | 2.19 | 2.08 | 1.99 | 1.82 | 1.61 | 1.36 | 1.13 | 1.01 | 0.87 | 0.75 |

#### **Buck-Boost Input Capacitor Selection**

A 10µF ceramic capacitor is recommended to improve transient behavior of the regulator and EMI behavior of the total power supply circuit. A ceramic capacitor placed as close as possible to the buck-boost input pin and power ground of the IC is recommended.

# **Battery Input Pin Capacitor Selection**

To make sure that the internal control circuits are supplied with a stable low noise supply voltage, a capacitor can be connected between VIN and AGND. Using a ceramic capacitor with a value of 0.1µF is recommended. The value of this capacitor should not be higher than 0. 22µF

#### **Buck-Boost Output Capacitor**

For the output capacitor, it is recommended to use small ceramic capacitors placed as close as possible to the BB\_OUT and PGND. If, for any reason, the application requires the use of large capacitors which can not be placed close to the IC, using a smaller ceramic capacitor in parallel to the large one is recommended. This small capacitor should be placed as close as possible to the BB\_OUT and PGND pins of the IC.

To get an estimate of the recommended minimum output capacitance, the following equation can be used.

(5)

A capacitor with a value in the range of the calculated minimum should be used. There are no additional requirements regarding minimum ESR. There is also no upper limit for the output capacitor value. Larger capacitors will cause lower output voltage ripple as well as lower output voltage drop during load transients.

# Setting V<sub>MAX</sub> (Non EEPROM Setting)

The operation of  $V_{MAX}$  is not set on EEPROM and the switches inside the block can be programmed for specific conditions such as diode drops, To connect to VBAT, To follow the maximum voltage with its logic enabled or to follow the maximum voltage and to connect to VBAT when VBB is lower than VBAT and to disconnect the  $V_{MAX}$  logic. The following table shows the options available.

# Table 1. Setting V<sub>MAX</sub> (Non EEPROM Setting)

| REG6_BIT6 | REG6_BIT7 | REG3 BIT7  |                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                 |

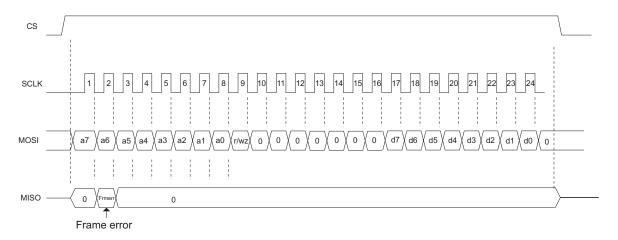

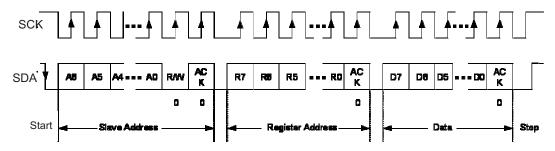

|-----------|-----------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|