# 54/74155 0/0/// 54LS/74LS155 0/0594

# **DUAL 1-OF-4 DECODER/DEMULTIPLEXER**

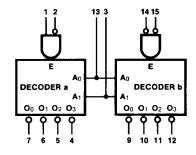

**DESCRIPTION** — The '155 contains two decoders with common Address ( $A_0$ ,  $A_1$ ) inputs and separate enable gates. Decoder "a" has an enable gate with one active HIGH and one active LOW input, while decoder "b" has two active LOW inputs. If the enable functions are satisfied, one output of each decoder will be LOW, as selected by the Address inputs.

### **ORDERING CODE:** See Section 9

|                    | PIN | COMMERCIAL GRADE                                                                         | MILITARY GRADE                                                                                          | PKG  |  |  |

|--------------------|-----|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------|--|--|

| PKGS               | ОПТ | $V_{CC} = +5.0 \text{ V } \pm 5\%,$<br>$T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}$ | $V_{CC} = +5.0 \text{ V} \pm 10\%,$<br>$T_A = -55^{\circ} \text{ C} \text{ to } +125^{\circ} \text{ C}$ | TYPE |  |  |

| Plastic<br>DIP (P) | Α   | 74155PC, 74LS155PC                                                                       |                                                                                                         | 9B   |  |  |

| Ceramic<br>DIP (D) | Α   | 74155DC, 74LS155DC                                                                       | 54155DM, 54LS155DM                                                                                      | 6B   |  |  |

| Flatpak<br>(F)     | Α   | 74155FC, 74LS155FC                                                                       | 54155FM, 54LS155FM                                                                                      | 4L   |  |  |

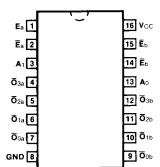

# CONNECTION DIAGRAM PINOUT A

### INPUT LOADING/FAN-OUT: See Section 3 for U.L. definitions

| PIN NAMES                         | DESCRIPTION                | <b>54/74 (U.L.)</b><br>HIGH/LOW | <b>54/74LS (U.L.)</b><br>HIGH/LOW |

|-----------------------------------|----------------------------|---------------------------------|-----------------------------------|

| A <sub>0</sub> , A <sub>1</sub>   | Address Inputs             | 1.0/1.0                         | 0.5/0.25                          |

| Ēa, Ēb                            | Enable Inputs (Active LOW) | 1.0/1.0                         | 0.5/0.25                          |

| E <sub>a</sub>                    | Enable Input (Active HIGH) | 1.0/1.0                         | 0.5/0.25                          |

| $\overline{O}_0 - \overline{O}_3$ | Outputs (Active LOW)       | 20/10                           | 10/5.0                            |

|                                   |                            |                                 | (2.5)                             |

### **LOGIC DIAGRAM**

V<sub>CC</sub> = Pin 16 GND = Pin 8 **FUNCTIONAL DESCRIPTION** — The '155 and '156 are dual 1-of-4 decoder/demultiplexers with common Address inputs and separate gated Enable inputs. When enabled, each decoder section accepts the binary weighted Address inputs (A<sub>0</sub>, A<sub>1</sub>) and provides four mutually exclusive active LOW outputs  $(\overline{O}_0 - \overline{O}_3)$ . If the Enable requirements of each decoder are not met, all outputs of that decoder are HIGH.

Each decoder section has a 2-input enable gate. The enable gate for decoder "a" requires one active HIGH input and one active LOW input ( $E_a$ ,  $\overline{E}_a$ ). In demultiplexing applications, decoder "a" can accept either true or complemented data by using the  $\overline{E}_a$  or  $E_a$  inputs respectively. The enable gate for decoder "b" requires two active LOW inputs ( $\overline{E}_b$ ,  $\overline{E}_b$ ). The devices can be used as a 1-of-8 decoder/demultiplexer by tying  $E_a$  to  $\overline{E}_b$  and relabeling the common connection as  $A_2$ . The other  $\overline{E}_b$  and  $\overline{E}_a$  are connected together to form the common enable.

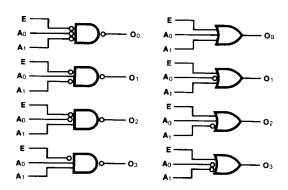

The '155 and '156 can be used to generate all four minterms of two variables. These four minterms are useful in some applications replacing multiple gate functions as shown in *Figure a*. The '156 has the further advantage of being able to AND the minterm functions by tying outputs together. Any number of terms can be wired-AND as shown below.

$$f = (E + A_0 + A_1) \bullet (E + \overline{A}_0 + A_1) \bullet (E + \overline{A}_0 + \overline{A}_1) \bullet (E + \overline{A}_0 + \overline{A}_1)$$

$$\text{where } = E = E_a + \overline{E}_a; E = E_b + E_b$$

Fig. a

#

### TRUTH TABLE

|   | ADD            | RESS        | ENA    | 3LE a  | 0           | OUTF           | TU <sup>r</sup> | 1                                | ENA    | BLE b          | (   | DUT         | PUT            | b              |

|---|----------------|-------------|--------|--------|-------------|----------------|-----------------|----------------------------------|--------|----------------|-----|-------------|----------------|----------------|

| L | A <sub>0</sub> | <b>A</b> 1  | Ea     | Ēa     | ıő          | Ō <sub>1</sub> | Ō₂              | Ō3                               | Ēδ     | Ē <sub>b</sub> | ō   | Ōı          | Ō <sub>2</sub> | Ō <sub>3</sub> |

|   | X<br>X<br>L    | X<br>L      | ΥX     | ΓIΧ    | IΙ          | H              | H               | $\mathtt{r}\mathtt{r}\mathtt{r}$ | HXL    | X<br>H<br>L    | HHL | H<br>H      | H<br>H<br>H    | H<br>H         |

|   | H              | L<br>H<br>H | H<br>H | L<br>L | Н<br>Н<br>Н | L<br>H<br>H    | H               | TIL                              | L<br>L | L<br>L         | H   | L<br>H<br>H | H<br>L<br>H    | H<br>H<br>L    |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

# DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

| SYMBOL | PARAMETER                       |          | 54/74      |            | 54/74LS    |              | UNITS      | CONDITIONS                                                                           |  |

|--------|---------------------------------|----------|------------|------------|------------|--------------|------------|--------------------------------------------------------------------------------------|--|

|        |                                 | Min      | Max        | Min        | Max        | 011110       | CONDITIONS |                                                                                      |  |

| los    | Output Short Circuit<br>Current | XM<br>XC | -20<br>-18 | -55<br>-57 | -20<br>-20 | -100<br>-100 | ns         | V <sub>CC</sub> = Max                                                                |  |

| loc    | Power Supply Current            | XM       |            | 35<br>40   |            | 10<br>10     | mA         | $V_{CC} = Max; \overline{E}_a, \overline{E}_b = Gno$ $A_0, A_1, E_a = 4.5 \text{ V}$ |  |

# AC CHARACTERISTICS: $V_{CC} = +5.0 \text{ V}$ , $T_A = +25^{\circ}\text{C}$ (See Section 3 for waveforms and load configurations)

| SYMBOL       |                                                                         | 54/74                                            | 54/74LS                | UNITS |                 |  |

|--------------|-------------------------------------------------------------------------|--------------------------------------------------|------------------------|-------|-----------------|--|

|              | PARAMETER                                                               | C <sub>L</sub> = 15 pF<br>R <sub>L</sub> = 400 Ω | C <sub>L</sub> = 15 pF |       | CONDITIONS      |  |

|              |                                                                         | Min Max                                          | Min Max                |       |                 |  |

| tplH<br>tpHL | Propagation Delay<br>An to On                                           | 32<br>32                                         | 18<br>27               | ns    | Figs. 3-1, 3-20 |  |

| tpLH<br>tpHL | Propagation Delay<br>E <sub>a</sub> or E <sub>b</sub> to O <sub>n</sub> | 20<br>27                                         | 15<br>24               | ns    | Figs. 3-1, 3-5  |  |

| tplH<br>tpHL | Propagation Delay<br>E <sub>a</sub> to Ō <sub>n</sub>                   | 24<br>30                                         | 25<br>25               | ns    | Figs. 3-1, 3-4  |  |