19 A13

18 A12 17 A A 1 1

16 A10

15 T A9

14 A8

13**5** A7

12**T** D

11 TE

18 A12

17 A A 1 1

16 A10

**A8**

15 A9

14

131 Α7

**FG PACKAGE** (TOP VIEW)

9 10 11 12

PIN NOMENCLATURE

Data Input

Ground 5-V Supply

Data Output

Write Enable

Address Inputs

Chip Enable/Power Down

JD PACKAGE (TOP VIEW)

A0 1 U20 VCC

A1 [ 2

A2∏3

A3 7 4

A4∏5

A5 ∏6

**А6**П

αП

$\nabla \Pi$

GND ∏ 10

A2 13

A3 14

A6 17

Q lis

Α5

A0-A13

D

Q

Ē

GND

Vcc

₩

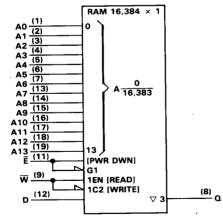

| • | 16.384 | x 1 | Organization |

|---|--------|-----|--------------|

- Separate I/O

- Military Temperature Range . . . 55 °C to 125°C (M Suffix)

- **Fast Static Operation**

- Battery Back-Up Operation . . . 2 Volt Data Retention

- Maximum Access Time from Address or Chip Enable

- '61CD16-25 . . . 25 ns

- '61CD16-35 . . . 35 ns '61CD16-45 . . . 45 ns

- Single 5-V Supply (10% Tolerance)

- JEDEC Standardized Pinout

- Complementary Silicon Gate MOS Technology with a 6-Transistor Memory Cell

- TTL Compatible Inputs and Outputs

- **Automatic Powerdown When Deselected**

- 125 μA MAX Standby Current at CMOS Levels

- Low Power Dissipation (VCC = 5.5 V)

- Active . . . 660 mW MAX

- Standby . . . 110 mW MAX (TTL Inputs)

- Standby . . . 0.68 mW MAX (CMOS Inputs)

- Standard and Class B Processing

- SM Prefix . . . Standard Processing

- SMJ Prefix . . . Class B Processing

- Three State Output

- **Packaging Options:**

- 20-Pin Ceramic 300-mil DIP

- 20-Pad Leadless Ceramic Chip Carrier

#### description

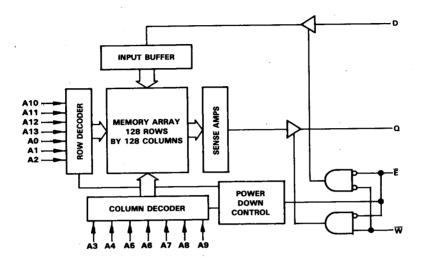

The '61CD16 is a separate I/O, 16,384-bit static random-access memory organized as 16,384 words by 1 bit. This memory is fabricated using complementary MOS technology utilizing a full

CMOS (six transistor cell) memory array. The six transistor cell provides for inherently lower soft error rates, improved stability across the operating temperature range, and extremely low standby power compared to the four transistor/two poly load cell making it ideal for military applications.

The '61CD16's static design and control signals (E and W) remove the need for refresh circuitry and simplify timing requirements. The chip-enable pin allows for easy memory expansion and automatic power-down. Access time from either address or chip enable is a maximum of 25, 35, or 45 ns, allowing speed upgrades for new and existing designs.

**PRODUCTION DATA documents contain information** current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1987, Texas Instruments Incorporated

8-167

Printed from www.freetradezone.com, a service of Partminer, Inc. This Material Copyrighted By Its Respective Manufacturer

#### addresses (A0-A13)

The 14 address inputs select one of the 16,384 -bit words in the RAM. The address inputs must be stable for the duration of a read or write cycle. The address inputs can be driven directly from standard Series 54/74 TTL with no external pull-up resistors.

### chip enable/power down (E)

The chip enable/power down terminal, which can be driven directly by standard TTL circuits, affects the data-in and data-out terminals and the internal functioning of the chip itself. Whenever the chip enable/power down is low (enabled), the device is operational, input and output terminals are enabled, and data can be read or written. When the chip enable/power down terminal is high (disabled), the device is deselected and put into a reduced-power standby mode. Data is retained during standby.

#### write enable (W)

The read or write mode is selected through the write-enable terminal. A logic high selects the read mode; a logic low selects the write mode.  $\overline{W}$  or  $\overline{E}$  must be high when changing addresses to prevent inadvertently writing data into a memory location. The  $\overline{W}$  input can be driven directly from standard TTL circuits.

#### data in (D)

Data can be written into a selected device when the write-enable input is low. The input terminal can be driven directly from standard TTL circuits. Data on the input pin (D) is written into the memory location specified on the address pins (AO-A13).

#### data out (Q)

The three-state output buffer provides direct TTL compatability with a fanout of two Series 54 TTL gates, one Series 54S TTL gate, or eight Series 54LS TTL gates. The output terminal is in the high-impedance state when chip enable  $(\overline{E})$  is high or whevever a write operation is being performed. Data out is the same polarity as data in.

# logic symbol†

#### **FUNCTION TABLE**

| INP | UTS | OUTPUTS     | MODE    | POWER   |

|-----|-----|-------------|---------|---------|

| Ē   | w   | Q           | WIODE   | 1011211 |

| Н   | х   | HI-Z        | Standby | Standby |

| L   | н   | Data Output | Read    | Active  |

| L   | Ll  | HI-Z        | Write   | Active  |

X = Don't Care.

<sup>†</sup>This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

Pin numbers shown are for the JD package.

8-168

Printed from www.freetradezone.com, a service of Partminer, Inc. This Material Copyrighted By Its Respective Manufacturer

8

#### functional block diagram

Storage temperature range .....-65°C to 150°C

NOTES: 1. All voltage values in this data sheet are with respect to GND.

2. V<sub>IL</sub> (MIN) of -3 V for short pulse durations of 20 ns or less. Prolonged operation at V<sub>IL</sub> levels below -1 V will result in excessive currents that may damage the device.

#### recommended operating conditions

|                                                      |   | IN  | NOM | MAX    | UNIT |

|------------------------------------------------------|---|-----|-----|--------|------|

| V <sub>CC</sub> Supply voltage                       | 4 | .5  | 5   | 5.5    | V    |

| V <sub>IH</sub> High-level input voltage             |   | 2   |     | CC + 1 | ٧    |

| V <sub>IL</sub> Low-level input voltage (see Note 2) |   | - 1 |     | 0.8    | V    |

| T <sub>C</sub> Operating case temperature            |   |     |     | 125    | °C   |

| To Operating free-air temperature                    |   | 55  |     |        | °C   |

# electrical characteristics over full ranges of recommended operating conditions (unless otherwise noted)

|      |                        |                   | TEST                                                     | '61  | CD16- | 25    | '61  | CD16- | 35    | UNIT |

|------|------------------------|-------------------|----------------------------------------------------------|------|-------|-------|------|-------|-------|------|

|      | PARAME                 | rer               | CONDITIONS                                               | MIN  | TYP   | MAX   | MIN  | TYP   | MAX   | ONI  |

| Vou  | High-level output      | voltage           | V <sub>CC</sub> = 4.5 V, I <sub>OH</sub> = -4 mA         | 2.4  |       |       | 2.4  |       |       | >    |

|      | Low-level output       |                   | V <sub>CC</sub> = 4.5 V, l <sub>OL</sub> = 8 mA          |      |       | 0.4   |      |       | 0.4   | >    |

| 100  | Input current (load    |                   | 0 V ≤ V <sub>I</sub> ≤ V <sub>CC</sub>                   | - 10 |       | 10    | - 10 |       | 10    | μА   |

| 10   | Output current (le     |                   | 0 V ≤ V <sub>O</sub> ≤ V <sub>CC</sub> , Output disabled | 50   |       | 50    | - 50 |       | 50    | μA   |

| los  | Short circuit outpo    |                   | V <sub>CC</sub> = 5.5 V, V <sub>O</sub> = GND            |      |       | - 350 |      |       | - 350 | mA   |

| 100  | VCC operating su       | pply current      | V <sub>CC</sub> = 5.5 V, I <sub>O</sub> = 0 mA           |      |       | 120   |      |       | 120   | mA   |

| 100  | V <sub>CC</sub> supply | TTL-level inputs  | Ē ≥ V <sub>IH</sub> , V <sub>CC</sub> = 5.5 V            |      |       | 20    |      |       | 20    | mA   |

| ICCI |                        | CMOS-level inputs |                                                          |      |       | 125   |      |       | 125   | μA   |

# electrical characteristics over full ranges of recommended operating conditions (unless otherwise noted)

|                                |                                   | TEST              |                                                          | '61CD16-45 |  |       |      |  |

|--------------------------------|-----------------------------------|-------------------|----------------------------------------------------------|------------|--|-------|------|--|

|                                | PARAMETER                         |                   | RAMETER CONDITIONS                                       |            |  |       | UNIT |  |

| Vон                            | High-level output voltage         |                   | V <sub>CC</sub> = 4.5 V, I <sub>OH</sub> = -4 mA         | 2.4        |  |       | V    |  |

| VOL                            | Low-level output voltage          |                   | V <sub>CC</sub> = 4.5 V, I <sub>OL</sub> = 8 mA          |            |  | 0.4   | V    |  |

| i<br>li                        | Input current (load)              |                   | 0 V ≤ V <sub>I</sub> ≤ V <sub>CC</sub>                   | - 10       |  | 10    | μΑ   |  |

| 10                             | Output current (leakage)          |                   | 0 V ≤ V <sub>O</sub> ≤ V <sub>CC</sub> , Output disabled | - 50       |  | 50    | μА   |  |

| los                            | Short circuit output current (see | B Note 3)         | V <sub>CC</sub> = 5.5 V, V <sub>O</sub> = GND            |            |  | - 350 | mA   |  |

| ICC                            | VCC operating supply current      |                   | V <sub>CC</sub> = 5.5 V, I <sub>O</sub> = 0 mA           |            |  | 120   | mA   |  |

|                                |                                   | TTL-level inputs  | Ë ≥ V <sub>1H</sub> , V <sub>CC</sub> = 5.5 V            |            |  | 20    | mA   |  |

| ICCI VCC supply current (stand | VCC supply current (standby)      | CMOS-level inputs | Inputs = V <sub>CC</sub> ±0.3, V <sub>CC</sub> = 5.5 V   |            |  | 125   | μА   |  |

NOTE 3: Not more than one output should be shorted at a time. The duration of the short circuit should not exceed 30 seconds.

TEXAS INSTRUMENTS

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77001

•

Military Products

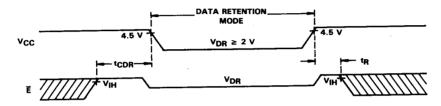

#### data retention characteristics

|                  | PARAMETER                            | TEST CONDITION                            | MIN    | TY<br>V <sub>C</sub> (<br>2.0 V | <i>.</i> @ | M/<br>VC0<br>2.0 V | ; <b>@</b> | UNIT        |

|------------------|--------------------------------------|-------------------------------------------|--------|---------------------------------|------------|--------------------|------------|-------------|

| VDR              | VCC for data retention               |                                           | 2.0    |                                 |            |                    |            | <b>&gt;</b> |

|                  | Data retention current               | $\overline{E} \geq V_{CC} - 0.2 V$ ,      |        | 3                               | 5          | 50                 | 75         | μА          |

| tCDR             | Chip deselect to data retention time | V <sub>IN</sub> ≥ V <sub>CC</sub> - 0.2 V | 0      |                                 |            |                    |            | ns          |

|                  | Operation recovery time              | or ≤ GND + 0.2 V                          | tc(RD) |                                 | _          |                    |            | ns          |

| ILI <sup>§</sup> | Input leakage current                |                                           |        |                                 | _          | <u> </u>           | 1          | μА          |

<sup>†</sup>TYP values listed are typical values at 25 °C.

#### data retention waveform

## capacitance, TA = 25°C, f = 1 MHz¶

| PARAMETER             | TEST CONDITIONS                 | MIN | TYP MA | UNIT |

|-----------------------|---------------------------------|-----|--------|------|

| C: Input capacitance  | TA = 25°C, f = 1 MHz, VCC = 5 V |     |        | 4 pF |

| Co Output capacitance | TA = 25°C, f = 1 MHz, VCC = 5 V |     |        | 7 pF |

<sup>¶</sup>Capacitance measurements are made on sample basis only.

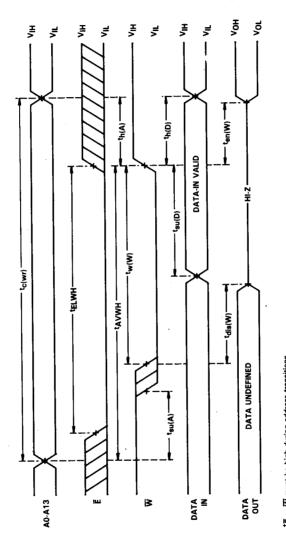

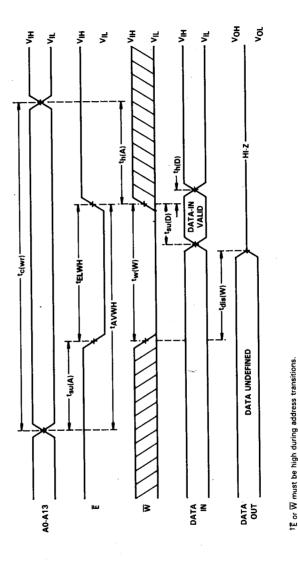

# timing requirements over recommended supply voltage range and operating temperature range

|                    |                                                         | '61CD16-25 |     | '61CD16-35 |     |     | UNIT |    |

|--------------------|---------------------------------------------------------|------------|-----|------------|-----|-----|------|----|

|                    |                                                         | MIN        | TYP | MAX        | MIN | TYP | MAX  |    |

| t <sub>c(rd)</sub> | Read cycle time                                         | 25         |     |            | 35  |     |      | ns |

| tc(wr)             | Write cycle time                                        | 25         |     |            | 35  |     |      | ns |

| tw(W)              | Write-enable pulse duration                             | 15         |     |            | 20  |     |      | ns |

| tELWH              | Chip-enable low to end of write                         | 25         |     |            | 30  |     |      | ns |

| t <sub>su(A)</sub> | Address setup time to write start                       | 0          |     |            | 0   |     |      | ns |

| t <sub>su(D)</sub> | Data setup time to write end                            | 12         |     |            | 15  |     |      | ns |

| th(A)              | Address hold from write end                             | 0          |     |            | 0   |     |      | ns |

| th(D)              | Data hold from write end                                | 0          |     |            | 0   |     |      | ns |

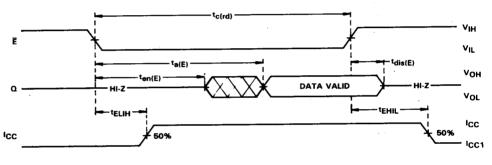

| <sup>t</sup> ELIH  | Delay time, chip-enable low to power up§                | 5          |     |            | 5   |     |      | ns |

| tEHIL.             | Delay time, chip-enable high to power down <sup>§</sup> |            |     | 35         |     |     | 35   | ns |

| tAVWH              | Address setup to write end                              | 25         |     |            | 30  |     |      | ns |

<sup>§</sup>This parameter is guaranteed but not tested.

t<sub>C(RD)</sub> = read cycle time.

This parameter is guaranteed but not tested.

<sup>t</sup>ELIH

teHIL.

<sup>t</sup>AVWH

'61CD16-45 UNIT MIN TYP MAX 45 ns <sup>t</sup>c(rd) Read cycle time 45 ns Write cycle time tc(wr) 20 กร Write-enable pulse duration tw(W) 40 ns Chip-enable low to end of write **tELWH** 0 ns Address setup time to write start t<sub>su(A)</sub> 15 ns Data setup time to write end t<sub>su(D)</sub> ns Address hold from write end th(A) 0 Data hold from write end th(D) Delay time, chip-enable low to power up<sup>†</sup> 5

timing requirements over recommended supply voltage range and operating temperature range

Address setup to write end

Delay time, chip-enable high to power down<sup>†</sup>

# switching characteristics over recommended supply voltage range and operating temperature range

35

ns

ns

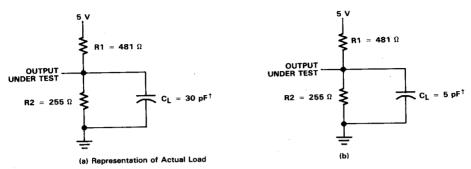

|           |                                                        | TEST                                  | '61CD16-25 |     | -25 | ′6  | 1CD16 | -35 | UNIT   |

|-----------|--------------------------------------------------------|---------------------------------------|------------|-----|-----|-----|-------|-----|--------|

|           | PARAMETER                                              | CONDITIONS                            |            | TYP | MAX | MIN | TYP   | MAX | O.C.I. |

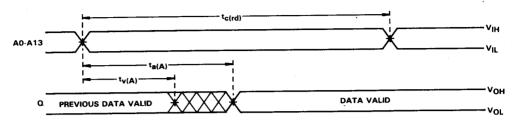

| ta(A)     | Access time from address                               | IOH = -4 mA, IOL = 8 mA               |            |     | 25  |     |       | 35  | ns     |

| -a(m)     | Access time from chip enable low                       | C <sub>L</sub> = 30 pF,               |            |     | 25  |     |       | 35  | ņs     |

|           | Output data valid after address change                 | See Figure 1a.                        | 0          | 3   |     | 0   | 3.    |     | ns     |

|           | Output enable time from write enable high ‡            |                                       | 0          |     | 15  | 0   |       | 20  | ns     |

|           | Output enable time from chip enable low <sup>‡</sup>   | R1 = 481 Ω, R2 = 255 Ω,               | 5          |     |     | 5   |       |     | ns     |

|           | Output disable time from chip enable high <sup>‡</sup> | C <sub>L</sub> = 5 pF, See Figure 1b. |            |     | 10  |     |       | 15  | ns     |

| tdie/\A/\ | Output disable time from write enable low <sup>‡</sup> |                                       |            |     | 10  |     |       | 15  | ns     |

# switching characteristics over recommended supply voltage range and operating temperature range

|                                                            | TEST                                            | ′61     | UNIT |     |      |  |

|------------------------------------------------------------|-------------------------------------------------|---------|------|-----|------|--|

| PARAMETER                                                  | CONDITIONS                                      | MIN TYP |      | MAX | UNII |  |

| ta(A) Access time from address                             | I <sub>OH</sub> = -4 mA, I <sub>OL</sub> = 8 mA |         |      | 45  | ns   |  |

| ta(E) Access time from chip enable low                     | C <sub>L</sub> = 30 pF,                         |         |      | 45  | ns   |  |

| ty(A) Output data valid after address change               | See Figure 1a.                                  | 0       | 3    |     | ns   |  |

| ten(W) Output enable time from write enable high           |                                                 | 0       |      | 20  | ns   |  |

| en(E) Output enable time from chip enable low <sup>‡</sup> | $R1 = 481 \Omega, R2 = 255 \Omega,$             | 5       |      |     | กร   |  |

| dis(E) Output disable time from chip enable high‡          | $C_L = 5$ pF, See Figure 1b.                    |         |      | 20  | ns   |  |

| tdis(W) Output disable time from write enable low          |                                                 |         |      | 20  | ns   |  |

<sup>&</sup>lt;sup>‡</sup>Transition is measured ±500 mV from steady state voltage; this parameter is guaranteed but not tested.

Military Products

<sup>&</sup>lt;sup>†</sup>This parameter is guaranteed but not tested.

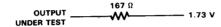

## PARAMETER MEASUREMENT INFORMATION

THEVENIN EQUIVALENT OF (a) OR (b)

<sup>†</sup>C<sub>L</sub> includes jig and scope capacitances.

FIGURE 1. OUTPUT LOAD CIRCUIT

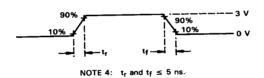

FIGURE 2. TRANSITION TIMES

# read cycle timing from address†

$^{\dagger}\overline{W}$  is high, and  $\overline{E}$  is low.

# read cycle timing from chip enable‡

${}^{\ddagger}\overline{W}$  is high, address is valid prior to or simultaneously with the high-to-low transition of  $\overline{E}.$

**Military Products**

8

TEXAS INSTRUMENTS

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77001

write cycle timing controlled by write enable†

1E or W must be high during address transitions.

NOTE: For both W-controlled and E-controlled Write operations, the internal write time of the memory is defined by the overlap of E low and W NOTE: For both W-controlled and E-controlled Write operations, the internal earlies as write is and either signal can terminate a write by going high. The data input setup and hold times low. Both signals must be low to initiate a write, and either signal can terminate a write by going high. The data input setup and hold times should be referenced to the edge that terminates the write.

TEXAS INSTRUMENTS

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77001

write cycle timing controlled by chip enable†

8

**Military Products**

8-176

Printed from www.freetradezone.com, a service of Partminer, Inc. This Material Copyrighted By Its Respective Manufacturer