### **General Description**

The MAX5963 dual hot-swap and diode ORing controller provides complete protection for dual-supply high availability systems. The device operates from 7.5V to 76V and provides hot-swap and low voltage-drop diode ORing functionality for two 7.5V to 76V outputs.

The MAX5963 allows for the safe insertion and removal of system line cards and FireWire® peripherals into a live backplane by providing inrush current control and active current limiting. The device controls external n-channel power MOSFETs to perform low-voltage-drop ORing, inrush current control, and current limiting functions. The current-limit function actively limits the current drawn by the load, protecting the load from a short-circuit condition. The MAX5963 also features a circuit-breaker function that disconnects the power to the load if the load current exceeds the circuit-breaker limit for a programmable circuit-breaker timeout.

The MAX5963 features an autoretry/latchoff input. In autoretry mode, the MAX5963 automatically restarts the turned-off channel after a programmable delay. In latchoff mode, the MAX5963 latches the channel off.

The MAX5963 consumes less than 10µA from the PWR supply in system power-off mode.

The MAX5963 is available in a 40-pin TQFN package (6mm x 6mm) and operates over the 0°C to +85°C upper commercial temperature range.

### **Applications**

Blade Servers Base-Station Line Cards Network Switches/Routers FireWire Desktops/Notebook Ports FireWire Hubs

Typical Operating Circuit appears at end of data sheet.

FireWire is a registered trademark of Apple, Inc.

**Features**

- ♦ Hot Swaps Two 7.5V to 76V Supplies

- **♦ Integrates Low-Voltage-Drop ORing Controller**

- ♦ ±5% Accuracy Bilevel Active Current Limit/Circuit **Breaker**

- ♦ Programmable Current-Limit/Circuit-Breaker **Timeout**

- ♦ 10µA Power-Off Mode Current

- ◆ Protects Up to Two FireWire Ports

- ♦ System Power-On/Off ORing

- **♦ Latchoff or Autoretry Power Management**

- **♦ Independent ON/OFF Control Allows Undervoltage Lockout Programming**

- **♦** Fast Load Disconnect through FOSO Input (FireWire Port)

### **Ordering Information**

| PART        | TEMP RANGE   | PIN-PACKAGE |  |  |

|-------------|--------------|-------------|--|--|

| MAX5963UTL+ | 0°C to +85°C | 40 TQFN-EP* |  |  |

<sup>+</sup>Denotes a lead-free/RoHS-compliant package.

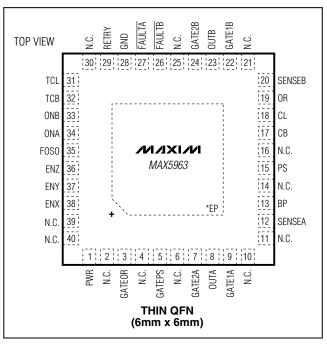

### Pin Configuration

<sup>\*</sup>EP = Exposed pad.

### **ABSOLUTE MAXIMUM RATINGS**

| PWR, PS to GND OUTA, OUTB, BP, RETRY to GND BP to PS BP to PWR OUTA, OUTB to PS SENSEA, SENSEB to PS. SENSEA, SENSEB, CL, CB, OR to GND SENSEA, SENSEB to CL, CB, OR CL, CB, OR to PS | 0.3V to +85V<br>0.3V to +85V<br>85V to +85V<br>40V to +85V<br>1V to +0.3V<br>0.3V to +85V<br>5V to +5V |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| GATE1A, GATE2A, GATE1B, GATE2B, GATEPS, GATEOR to GND                                                                                                                                 | 0.3V to +8V<br>0.3V to +8V<br>0.3V to +8V                                                              |

| FAULTA, FAULTB to GNDONA, ONB, FOSO, TCL.                             | 0.3V to +85V                             |

|-----------------------------------------------------------------------|------------------------------------------|

| TCB to GND0.3V to the lesser of + TCL, TCB to GND                     | $0.3V \text{ to } (V_{PS} + 0.3V)$       |

| Continuous Power Dissipation<br>40-Pin TQFN (derate 37mW/°C above +70 |                                          |

| Thermal Resistance (Note 1) θJAθJC                                    |                                          |

| Operating Temperature Range                                           | 0°C to +85°C<br>+150°C<br>60°C to +150°C |

**Note 1:** Package thermal resistances obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maxim-ic.com/thermal-tutorial">www.maxim-ic.com/thermal-tutorial</a>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{PS} = V_{PWR} = 12V, V_{FOSO} = 0, V_{ENX} = V_{ENY} = V_{ENZ} = V_{PWR}, and T_A = T_J = 0^{\circ}C$  to +85°C, unless otherwise noted. See the *Typical Operating Circuit* for connections. Typical values are at T\_A = +25°C.) (Note 2)

| PARAMETER                              | SYMBOL              | CONDITIONS                                                                                                                      | MIN | TYP  | MAX | UNITS |

|----------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| PS Voltage Range                       | VPS                 |                                                                                                                                 | 7.5 |      | 76  | V     |

| PS Supply Current                      | I <sub>PS</sub>     | $7.5V \le V_{PWR} \le 76V$ , $V_{PS} = V_{PWR}$ , $V_{ONA} = V_{ONB} = 3V$ , no load                                            |     | 4.5  | 7   | mA    |

| PWR Voltage Range                      | V <sub>PWR</sub>    |                                                                                                                                 | 7.5 |      | 76  | V     |

| PWR Supply Current                     | I <sub>PWR</sub>    | $7.5V \le V_{PWR} \le 76V$ , $V_{PS} = V_{PWR}$ , $V_{ONA} = V_{ONB} = 3V$ , no load                                            |     | 400  | 600 | μΑ    |

| PWR Shutdown Current                   | Inwo outh           | 7.5V ≤ V <sub>PWR</sub> ≤ 12V, V <sub>ENX</sub> = V <sub>ENY</sub> = V <sub>ENZ</sub> = 0.4V, PS is open                        |     | 5    | 10  |       |

|                                        | IPWR_SHDN           | 12V ≤ V <sub>PWR</sub> ≤ 76V, V <sub>ENX</sub> = V <sub>ENY</sub> = V <sub>ENZ</sub><br>= 0.4V, PS is open                      |     | 12   | 24  | μΑ    |

| PWR Standby Current                    | I <sub>PWR_SB</sub> | $7.5V \le V_{PWR} \le 76V$ , $V_{PS} = V_{PWR}$ , $V_{ENX} = V_{ENY} = V_{ENZ} = 0.4V$                                          |     | 50   | 75  | μА    |

| PS Undervoltage Lockout<br>Threshold   | VPS_UVLO            | PS rising, V <sub>ENX</sub> = V <sub>ENY</sub> = V <sub>ENZ</sub> = 0,<br>V <sub>ONA</sub> = V <sub>ONB</sub> = V <sub>BP</sub> | 6.0 | 6.5  | 7.0 | V     |

| PS Undervoltage Lockout<br>Hysteresis  |                     |                                                                                                                                 |     | 0.35 |     | V     |

| PWR Undervoltage Lockout<br>Threshold  | VPWR_UVLO           | V <sub>PWR</sub> rising, PS = GND, V <sub>ONA</sub> = V <sub>ONB</sub> = V <sub>BP</sub>                                        | 6.0 | 6.5  | 7.0 | V     |

| PWR Undervoltage Lockout<br>Hysteresis |                     |                                                                                                                                 |     | 0.35 |     | V     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{PS} = V_{PWR} = 12V, V_{FOSO} = 0, V_{ENX} = V_{ENY} = V_{ENZ} = V_{PWR}, and T_A = T_J = 0^{\circ}C$  to +85°C, unless otherwise noted. See the *Typical Operating Circuit* for connections. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER SYMBOL CONDITIONS                  |                                     | MIN                                                                                        | TYP   | MAX   | UNITS |    |

|----------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------|-------|-------|-------|----|

| LOGIC INPUTS                                 |                                     |                                                                                            |       |       |       | •  |

| ON_ Threshold                                | Vonth                               | V <sub>ON</sub> _ rising                                                                   | 1.150 | 1.240 | 1.350 | V  |

| ON_ Hysteresis                               | Vonth_Hys                           |                                                                                            |       | 70    |       | mV |

| ON_ Input Bias Current                       | I <sub>ON</sub>                     | V <sub>ON</sub> _ = 76V                                                                    |       |       | 1     | μΑ |

| EN_ Input Logic-Low Voltage<br>Threshold     | V <sub>EN_L</sub>                   |                                                                                            |       |       | 0.7   | V  |

| EN_ Input Logic-High Voltage<br>Threshold    | V <sub>EN_H</sub>                   |                                                                                            | 1.8   |       |       | V  |

| EN_ Input Bias Current                       | I <sub>EN</sub> _                   | V <sub>EN</sub> _ = 76V, V <sub>FOSO</sub> = 0                                             |       |       | 1     | μΑ |

| RETRY Pulldown Current                       | I <sub>RTRY</sub>                   | V <sub>RETRY</sub> = 0.7V                                                                  |       | 20    |       | μΑ |

| RETRY Input Logic-Low Voltage Threshold      | V <sub>RTRYL</sub>                  |                                                                                            |       |       | 0.7   | V  |

| RETRY Input Logic-High<br>Voltage Threshold  | V <sub>RTRYH</sub>                  |                                                                                            | 1.8   |       |       | V  |

| FOSO Threshold                               | VFOSO_TH                            | V <sub>ONA</sub> or V <sub>ONB</sub> = 3V                                                  | 1.150 | 1.240 | 1.350 | V  |

| FOSO Hysteresis                              |                                     | V <sub>ONA</sub> or V <sub>ONB</sub> = 3V                                                  |       | 70    |       | mV |

| FOSO Input Leakage Current                   | IFOSOL                              | V <sub>ENZ</sub> = 0, V <sub>FOSO</sub> = V <sub>PWR</sub> = 76V                           |       |       | 1     | μΑ |

| TCL, TCB Input Bias Current in Shutdown      | I <sub>TCL</sub> , I <sub>TCB</sub> | V <sub>ENZ</sub> = 0, V <sub>PS</sub> = 76V, V <sub>TCL</sub> = V <sub>TCB</sub> = 76V     |       |       | 4     | μA |

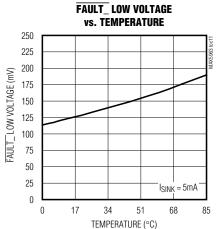

| FAULT_ Output Low Voltage                    | V <sub>OL</sub>                     | Low-impedance state, IFAULTA = IFAULTB = 5mA                                               |       | 0.12  | 0.275 | V  |

| FAULT_ Output High Leakage<br>Current        | Іон                                 | High-impedance state, VFAULTA = VFAULTB = 76V                                              |       |       | 1     | μA |

| OUT_ Input Current                           | I <sub>OUT</sub> _                  | V <sub>ENZ</sub> = 0, V <sub>PS</sub> = 76V, V <sub>OUTA</sub> = V <sub>OUTB</sub> = 76.1V | 15    | 50    | 100   | μΑ |

| SENSE_ Input Current                         | ISENSE_                             | VENZ = 0, VPS = VOR = VCL = VCB = 76V,<br>VSENSEA = VSENSEB = 76V                          | 1     |       | 4     | μΑ |

| CIRCUIT-BREAKER, CURRENT                     | LIMIT, AND C                        | PRING THRESHOLDS                                                                           |       |       |       | •  |

| Circuit-Breaker Set Current                  | ICBSET                              | 7.5V ≤ V <sub>PWR</sub> ≤ 76V, V <sub>PS</sub> = V <sub>PWR</sub>                          | 97.0  | 100.0 | 103.2 | μΑ |

| Circuit-Breaker Comparator<br>Offset Voltage |                                     | 7.5V ≤ V <sub>PWR</sub> ≤ 76V, V <sub>PS</sub> = V <sub>PWR</sub>                          | -2.5  |       | +2.5  | mV |

| Current-Limit Set Current                    | ICLSET                              | 7.5V ≤ V <sub>PWR</sub> ≤ 76V, V <sub>PS</sub> = V <sub>PWR</sub>                          | 97.0  | 100.0 | 103.2 | μΑ |

| Current-Limit Comparator Offset<br>Voltage   |                                     | 7.5V ≤ V <sub>PWR</sub> ≤ 76V, V <sub>PS</sub> = V <sub>PWR</sub>                          | -2.5  |       | +2.5  | mV |

| ORing Threshold Set Current                  | IORSET                              | 7.5V ≤ V <sub>PWR</sub> ≤ 76V, V <sub>PS</sub> = V <sub>PWR</sub>                          | 96.5  | 100   | 103.5 | μΑ |

| ORing Threshold Set Current<br>Hysteresis    | IORHYS                              | 7.5V ≤ V <sub>PWR</sub> ≤ 76V, V <sub>PS</sub> = V <sub>PWR</sub>                          | 47.5  | 50    | 52.5  | μΑ |

|                                              | •                                   | •                                                                                          |       |       |       |    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{PS} = V_{PWR} = 12V, V_{FOSO} = 0, V_{ENX} = V_{ENY} = V_{ENZ} = V_{PWR}, and T_A = T_J = 0^{\circ}C$  to +85°C, unless otherwise noted. See the *Typical Operating Circuit* for connections. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                                                                          | SYMBOL           | CONDITIONS                                                                 | MIN  | TYP                      | MAX  | UNITS |

|------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------|------|--------------------------|------|-------|

| ORing Threshold Comparator Offset Voltage                                          |                  | 7.5V ≤ V <sub>PWR</sub> ≤ 76V, V <sub>PS</sub> = V <sub>PWR</sub> (Note 3) | -0.4 | 0                        | +0.4 | mV    |

| ORing Threshold Comparator<br>Total Offset Voltage Supply Drift                    |                  | 7.5V ≤ V <sub>PWR</sub> ≤ 76V, V <sub>PS</sub> = V <sub>PWR</sub>          |      | 100                      |      | μV    |

| ORing Threshold Comparator<br>Total Offset Temperature Drift                       |                  | 0°C ≤ T <sub>A</sub> ≤ +85°C, V <sub>PS</sub> = V <sub>PWR</sub>           |      | 40                       |      | μV    |

| Fast Pulldown Current-Limit<br>Threshold Voltage                                   | V <sub>THF</sub> | 7.5V ≤ V <sub>PWR</sub> ≤ 76V, V <sub>PS</sub> = V <sub>PWR</sub>          |      | V <sub>CL</sub> +<br>57  |      | mV    |

| TIMING                                                                             |                  |                                                                            |      |                          |      |       |

| Circuit-Breaker Timeout                                                            | tcB              | $R_{TCB} = 4k\Omega$ (Note 4)                                              | 0.85 | 1.02                     | 1.23 | ms    |

| Circuit-Breaker Default Timeout                                                    |                  | V <sub>TCB</sub> = V <sub>BP</sub>                                         | 2.2  | 3.0                      | 3.8  | ms    |

| Circuit-Breaker Timeout Count-<br>Down/Count-Up Ratio                              |                  |                                                                            |      | 1                        |      |       |

| Current-Limit Timeout                                                              | tcL              | $R_{TCL} = 4k\Omega$ (Note 4)                                              | 0.85 | 1.02                     | 1.23 | ms    |

| Current-Limit Default Timeout                                                      |                  | V <sub>TCL</sub> = V <sub>BP</sub>                                         | 0.85 | 1.02                     | 1.23 | ms    |

| Current-Limit Timeout Count-<br>Down/Count-Up Ratio                                |                  |                                                                            |      | 128                      |      |       |

| Automatic Restart Delay after<br>Current-Limit Timeout                             | tOFFCL           |                                                                            |      | t <sub>CL</sub> x<br>128 |      | ms    |

| Automatic Restart Delay after Circuit-Breaker Timeout                              | tOFFCB           |                                                                            |      | t <sub>CB</sub> x<br>128 |      | ms    |

| Channel A/Channel B FOSO<br>Turn-On Delay                                          | tFOSOF           | Vona = Vonb = 3V, FOSO falling                                             | 0.4  | 1.0                      | 1.5  | S     |

| ON_Turn-On Response Time<br>(Time from ON_ Pulled High to<br>GATE_ Pulled High)    | ton_             |                                                                            |      | 2                        |      | ms    |

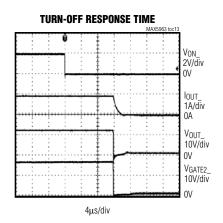

| ON_Turn-Off Response Time<br>(Time from ON_ Pulled Low to<br>GATE_ Pulled Low)     | ton_off          | VON_ < VONTH_HYST, (VGATE VOUT_)<br>< 1V, GATE_A and GATE_B are open       |      | 10                       |      | μs    |

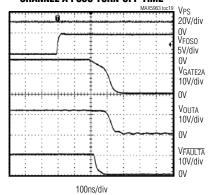

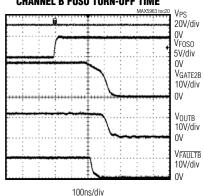

| FOSO Turn-Off Response Time<br>(Time from FOSO Rising Edge<br>to GATE_ Pulled Low) | tFOSO_OFF        | (VGATE_A - VOUTA) < 1V, (VGATE_B - VOUTB) < 1V, GATE_A and GATE_B are open |      | 0.34                     | 0.60 | μs    |

| Minimum Delay from ENZ Low to Low-Current Shutdown Mode                            | tshdn            | ENZ steps from 1.3V to 0.4V                                                |      | 50                       |      | μs    |

\_\_\_\_\_\_\_/N/XI/M

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{PS} = V_{PWR} = 12V, V_{FOSO} = 0, V_{ENX} = V_{ENY} = V_{ENZ} = V_{PWR}, and T_A = T_J = 0^{\circ}C$  to +85°C, unless otherwise noted. See the *Typical Operating Circuit* for connections. Typical values are at T\_A = +25°C.) (Note 2)

| PARAMETER                               | SYMBOL                                  | CONDITIONS                                                                                                                                                    |                                                                                                                                  | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| GATE CONTROLS                           |                                         |                                                                                                                                                               |                                                                                                                                  |      |      |      |       |

| GATE_ Pullup Current                    | IGU_                                    |                                                                                                                                                               |                                                                                                                                  | 35   | 48   | 60   | μΑ    |

|                                         | VGATE1A,<br>VGATE2A,<br>VGATE1B,        | VGATE1A - VOUTA,<br>VGATE2A - VOUTA,<br>VGATE1B - VOUTB,                                                                                                      | V <sub>PWR</sub> = V <sub>PS</sub> ,<br>7.5V ≤ V <sub>PWR</sub> ≤ 8V,<br>V <sub>OUTA</sub> = V <sub>OUTB</sub> = V <sub>PS</sub> | 4.00 | 4.75 | 6.00 | V     |

| GATE_ High Voltage                      | VGATE2B,<br>VGATEPS,<br>VGATEOR         | VGATE2B - VOUTB,<br>VGATEPS - VPS,<br>VGATEOR - VPWR                                                                                                          | VPWR = VPS,<br>8V ≤ VPWR ≤ 76V,<br>VOUTA = VOUTB = VPS                                                                           | 4.50 | 5.50 | 6.50 | V     |

| GATE_ Pulldown Current                  | IGDA1,<br>IGDA2,<br>IGDB1, IGDB2        | V <sub>CL</sub> < (V <sub>PS</sub> - V <sub>SENS</sub>                                                                                                        | E_) < VTHF                                                                                                                       | 350  | 500  | 650  | μΑ    |

| GATE_ Fast Pulldown Current             | IGDFA1,<br>IGDFA2,<br>IGDFB1,<br>IGDFB2 | (VPS - VSENSE_) > VTHF,<br>VGATE_ = (VOUT_ + 4.5V)                                                                                                            |                                                                                                                                  | 40   | 125  | 190  | mA    |

| GATE_ Peak Pulldown Current             | IGDPA1,<br>IGDPA2,<br>IGDPB1,<br>IGDPB2 | (VPS - VSENSE_) = 1V                                                                                                                                          |                                                                                                                                  |      | 1.0  |      | А     |

| GATE_ Pulldown Current During           | IGOFFA1,<br>IGOFFA2,                    | VGATE = (VOUT + 4.5V), VPS > VPS_UVLO                                                                                                                         |                                                                                                                                  | 40   | 125  | 200  | mA    |

| Any GATE_ Turn-Off Condition            | IGOFFB1,<br>IGOFFB2                     |                                                                                                                                                               |                                                                                                                                  | 30   |      | 150  |       |

| GATEPS Pulldown Current                 | IGDPS                                   | V <sub>ENZ</sub> = 0, V <sub>GATEPS</sub> - V <sub>PS</sub> = 4.5V                                                                                            |                                                                                                                                  | 45   | 125  | 200  | mA    |

| GATEOR Turn-Off Switch<br>On-Resistance | RGATEOR                                 | Measured between GATEOR and V <sub>PWR</sub> , (V <sub>SENSEA</sub> + V <sub>SENSEB</sub> )/2 > V <sub>OR</sub> , V <sub>GATEOR</sub> - V <sub>PWR</sub> = 2V |                                                                                                                                  |      | 2    | 3    | Ω     |

- Note 2: All min/max parameters are tested at  $T_A = +25^{\circ}C$  and  $T_A = +85^{\circ}C$ . Limits through the temperature range are guaranteed by design.

- **Note 3:** This is the offset value immediately after initialization. The MAX5963 minimizes offset at startup according to the temperature at that time. After initialization the temperature offset voltage drift and supply voltage drift apply.

- Note 4: Connect TCL/TCB to BP or PS for the default timeout period or connect a resistor from TCL/TCB to GND to program the current-limit timeout.

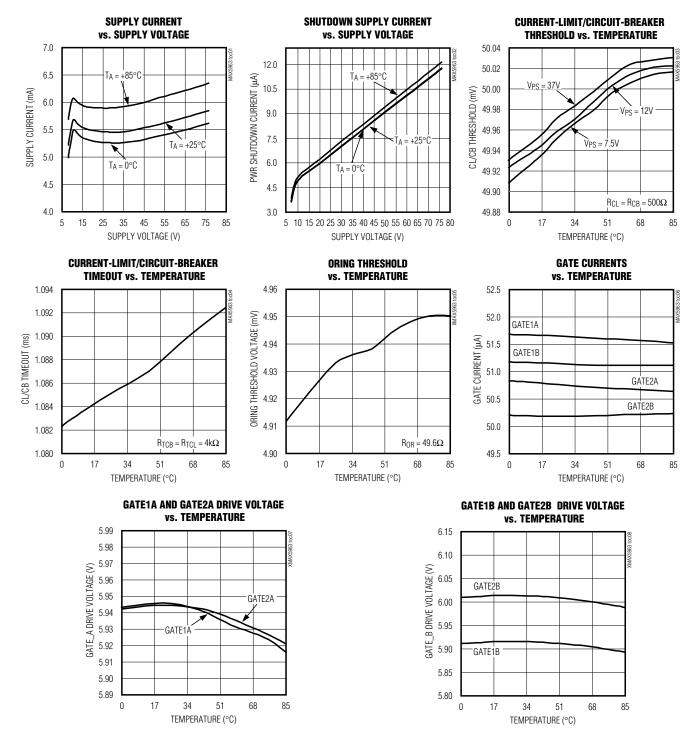

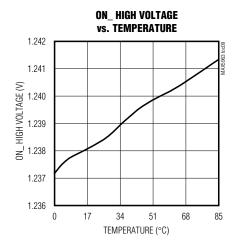

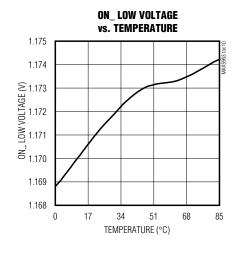

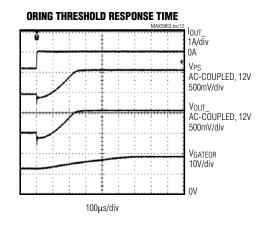

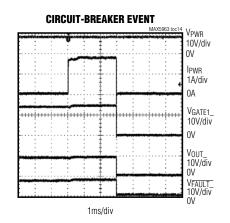

### **Typical Operating Characteristics**

$(V_{PS} = V_{PWR} = 12V, V_{GND} = V_{FOSO} = 0. T_A = +25^{\circ}C, unless otherwise noted.)$

### Typical Operating Characteristics (continued)

(VPS = VPWR = 12V, VGND = VFOSO = 0.  $T_A = +25$ °C, unless otherwise noted.)

### Typical Operating Characteristics (continued)

(VPS = VPWR = 12V, VGND = VFOSO = 0. TA = +25°C, unless otherwise noted.)

### **CHANNEL A FOSO TURN-OFF TIME**

### **CHANNEL B FOSO TURN-OFF TIME**

### Pin Description

| PIN                                               | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                 | PWR    | System Power Input. Connect to the system power source. The MAX5963 draws less than 10µA of current from this input when GATEPS is off. Bypass PWR to GND with a 0.1µF ceramic capacitor.                                                                                                                                     |

| 2, 4, 6, 10, 11,<br>14, 16, 21, 25,<br>30, 39, 40 | N.C.   | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                      |

| 3                                                 | GATEOR | ORing MOSFET Gate-Drive Output. Referenced to PWR. GATEOR is a charge pump with a 50µA pullup current to 5.5V (typ) above V <sub>PWR</sub> when active.                                                                                                                                                                       |

| 5                                                 | GATEPS | System Power MOSFET Gate-Drive Output. Referenced to PS. GATEPS is a charge pump with a 50µA pullup current to 5.5V (typ) above V <sub>PS</sub> when active.                                                                                                                                                                  |

| 7                                                 | GATE2A | Channel A Current-Limiter Switch Gate-Drive Output 2. Referenced to OUTA. Connect GATE2A to the gate of the second n-channel MOSFET (see the <i>Typical Operating Circuit</i> ). GATE2A is a charge pump with a 50µA pullup current to 5.5V (typ) above OUTA when active. GATE2A is identical to, but independent of, GATE1A. |

| 8                                                 | OUTA   | Channel A Output-Voltage Sense. Connect to the output.                                                                                                                                                                                                                                                                        |

| 9                                                 | GATE1A | Channel A Current-Limiter Switch Gate-Drive Output 1. Referenced to OUTA. Connect GATE1A to the gate of the first n-channel MOSFET (see the <i>Typical Operating Circuit</i> ). GATE1A is a charge pump with a 50µA pullup current to 5.5V (typ) above OUTA when active. GATE1A is identical to, but independent of, GATE2A.  |

| 12                                                | SENSEA | Channel A Current-Sense Negative Input. Connect the negative voltage-sensing terminal of a current-sense resistor, R <sub>SENSEA</sub> , to SENSEA. Connect the positive voltage-sensing terminal of R <sub>SENSEA</sub> to PS.                                                                                               |

| 13                                                | BP     | Output of Diode OR Connection between PWR and PS. Bypass BP to GND with a 1µF capacitor.                                                                                                                                                                                                                                      |

| 15                                                | PS     | Power Priority Input. Connect to the source of the external QPS FET. The MAX5963 draws most of its power from PS whenever possible. Bypass PS to GND with a 0.1µF ceramic capacitor. Ensure that the bypass capacitance on PS is less than or equal to the bypass capacitance on PWR.                                         |

| 17                                                | СВ     | Circuit-Breaker Threshold Programming Input. Connect a resistor from PS to CB to program the circuit-breaker threshold. A capacitor connected from CB to PS is recommended for impedance matching.                                                                                                                            |

| 18                                                | CL     | Current-Limit Threshold Programming Input. Connect a resistor from PS to CL to program the current-limit threshold. A capacitor connected from CL to PS is recommended for impedance matching.                                                                                                                                |

| 19                                                | OR     | ORing Threshold Programming Input. Connect a resistor from PS to OR to program the ORing current threshold. A capacitor connected from OR to PS is recommended for impedance matching.                                                                                                                                        |

| 20                                                | SENSEB | Channel B Current-Sense Negative Input. Connect the negative voltage-sensing terminal of a current-sense resistor, R <sub>SENSEB</sub> , to SENSEB. Connect the positive voltage-sensing terminal of R <sub>SENSEB</sub> to PS.                                                                                               |

| 22                                                | GATE1B | Channel B Current-Limiter Switch Gate-Drive Output 1. Referenced to OUTB. Connect GATE1B to the gate of the 1st n-channel MOSFET (see the <i>Typical Operating Circuit</i> ). GATE1B is a charge pump with a 50µA pullup current to 5.5V (typ) above OUTB when active. GATE1B is identical to, but independent of, GATE2B.    |

| 23                                                | OUTB   | Channel B Output-Voltage Sense. Connect to the output.                                                                                                                                                                                                                                                                        |

|                                                   | •      | •                                                                                                                                                                                                                                                                                                                             |

### Pin Description (continued)

| PIN | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24  | GATE2B | Channel B Current-Limiter Switch Gate-Drive Output 2. Referenced to OUTB. Connect GATE2B to the gate of the second n-channel MOSFET (see the <i>Typical Operating Circuit</i> ). GATE2B is a charge pump with a 50µA pullup current to 5.5V (typ) above OUTB when active. GATE2B is identical to, but independent of, GATE1B.                                                                                                                                                   |

| 26  | FAULTB | Channel B Current-Fault Status Output. FAULTB is an open-drain output. FAULTB goes low after a current-limit or circuit-breaker fault on channel B has exceeded the current-limit or circuit-breaker timeout period (see the Current-Fault Status Output (FAULT_) section).                                                                                                                                                                                                     |

| 27  | FAULTA | Channel A Current-Fault Status Output. FAULTA is an open-drain output. FAULTA goes low after a current-limit or circuit-breaker fault on channel A has exceeded the current-limit or circuit-breaker timeout period (see the Current-Fault Status Output (FAULT_) section).                                                                                                                                                                                                     |

| 28  | GND    | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 29  | RETRY  | Latch or Autoretry Fault Management Selection Input. Internally pulled to ground. Connect RETRY to BP or PS for autorestart mode. Leave RETRY floating to select latchoff mode after a current-limit/circuit-breaker timeout.                                                                                                                                                                                                                                                   |

| 31  | TCL    | Current-Limit Timer Programming Input. Connect TCL to BP or PS for the default timeout period or connect a resistor from TCL to GND to program the current-limit timeout.                                                                                                                                                                                                                                                                                                       |

| 32  | TCB    | Circuit-Breaker Timer Programming Input. Connect TCB to BP or PS for the default timeout period or connect a resistor from TCB to GND to program the circuit-breaker timeout.                                                                                                                                                                                                                                                                                                   |

| 33  | ONB    | Channel B On/Off Control Input. ONB sets the undervoltage lockout threshold for channel B and resets the channel after a fault latch. Drive ONB high (>1.24V (typ)) to turn on channel B. Drive ONB low to disable the channel. Connect a resistive-divider from PS to ONB and to GND to program the desired undervoltage lockout threshold for the channel.                                                                                                                    |

| 34  | ONA    | Channel A On/Off Control Input. ONA sets the undervoltage lockout threshold for channel A and resets the channel after a fault latch. Drive ONA high (>1.24V (typ)) to turn on channel A. Drive ONA low to disable the channel. Connect a resistive-divider from PS to ONA and to GND to program the desired undervoltage lockout threshold for the channel.                                                                                                                    |

| 35  | FOSO   | Fast-Off/Slow-On Logic Input. GATE1A, GATE2A, GATE1B, and GATE2B immediately pull low when FOSO exceeds the 1.24V (typ) threshold. The MAX5963 waits for the 1s (typ) turn-on delay once FOSO falls below the threshold hysteresis before allowing either channel to turn back on.                                                                                                                                                                                              |

| 36  | ENZ    | Enable Z Logic Input. Pull ENZ up to PWR for logic-high. ENZ is a logic input that is ANDed with the OR combination of ENX and ENY. The output of this logic determines whether the MAX5963 goes into PWR shutdown mode. In PWR shutdown mode, the MAX5963 draws less than 10µA from PWR. However, if the logic combination of ENX, ENY, and ENZ is low, the chip can still be powered through either channel. See the <i>Power-Supply Enables (ENX, ENY, and ENZ)</i> section. |

| 37  | ENY    | Logic-Enable Input Control GATEPS On/Off. Pull up to PWR for logic-high. See the <i>Power-Supply Enables (ENX, ENY, and ENZ)</i> section.                                                                                                                                                                                                                                                                                                                                       |

| 38  | ENX    | Logic-Enable Input Control GATEPS On/Off. Pull up to PWR for logic-high. See the <i>Power-Supply Enables (ENX, ENY, and ENZ)</i> section.                                                                                                                                                                                                                                                                                                                                       |

| _   | EP     | Exposed Pad. Connect EP to the GND plane. EP functions as a heatsink to maximize thermal dissipation. Do not use as the main ground connection.                                                                                                                                                                                                                                                                                                                                 |

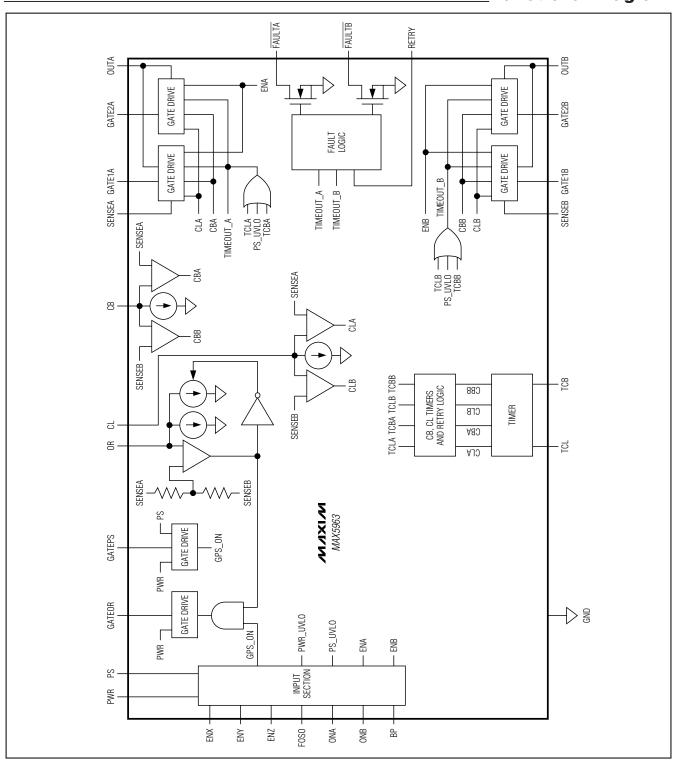

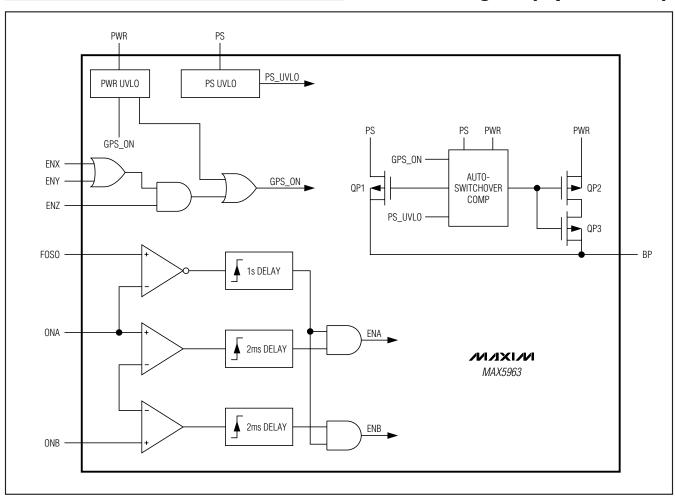

### Functional Diagram

### Functional Diagram (Input Section)

### **Detailed Description**

The MAX5963 dual-channel, hot-swap controller IC performs hot-swapping, power-supply ORing, and current limiting for high availability systems. The MAX5963 incorporates six MOSFET drivers (GATEPS, GATEOR, GATE1\_, and GATE2\_) to control external n-channel power MOSFETs to perform low-voltage-drop power-supply ORing (GATEOR), hot-swapping, and current limiting from the input power supply to the load. A sense resistor provides accurate current limiting for each independent channel. GATE1\_ and GATE2\_ provide load disconnect to prevent current flow from PS to OUT\_. GATEOR and GATEPS provide true load disconnect from PS to PWR.

The MAX5963 independent channels remain in low-current PWR shutdown mode when ENZ is low or when both ENX and ENY are low. Low-current shutdown mode disables the MAX5963 channels resulting in less than 10µA drawn from PWR. However, if the logic combination of ENX, ENY, and ENZ is low, the chip can still be powered through either channel.

When the input supply voltage (VPS) is above the 6.5V (typ) PS\_UVLO threshold, and VON\_ is above the 1.24V (typ) VONTH threshold, the MAX5963 channel turns on, sourcing 50µA (typ) current from GATE\_, to enhance Q\_ slowly. If the voltage across the current-sense resistor, VSENSE\_, is greater than the current-limit threshold, the MAX5963 regulates the GATE\_ voltage to limit the load current at the current-limit level so that VSENSE\_ is equal to the current-limit threshold voltage, VCL. In normal operation, VSENSE\_ drops below VCL and GATE\_ rises to approximately 5.5V (typ) above OUT\_.

If the channel continues to operate in current limit beyond the current-limit timeout (t<sub>CL</sub>), the MAX5963 either latches off the channel or retries depending on the state of RETRY. If the voltage across the current-sense resistor, VSENSE\_, is greater than the circuit-breaker threshold for longer than the circuit-breaker timeout (t<sub>CB</sub>), the MAX5963 either latches off the channel or retries depending on the state of RETRY. See the *Current-Limit Timeout* and *Circuit-Breaker Timeout* sections for more information on setting TCL and TCB.

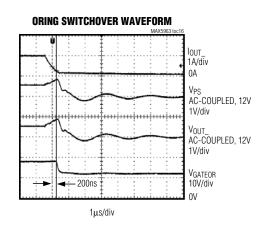

GATEOR controls the MAX5963 ORing function. Initially, GATEOR is off and the load current conducts through the body diode of QOR. GATEOR rises to 5.5V above VPWR when (VSENSEA + VSENSEB)/2 exceeds VOR\_TH, thereby enhancing QOR and reducing the voltage drop, power dissipation, and heat generation in the power-supply pathway. When a voltage greater than VPWR is connected at OUTA or OUTB the higher

voltage source provides current to the load(s). The MAX5963 turns off GATEOR rapidly upon VSENSE\_falling below the VOR hysteresis, thus blocking the higher voltage from backdriving VPWR. When the load current drops, causing VSENSE\_ to fall below the hysteresis, GATEOR turns off.

#### **Current Limiting**

The MAX5963 limits the load current by monitoring the voltage across RSENSE\_ and regulating the current to the load, ensuring that the voltage across the resistor is below the programmable current-limit threshold voltage (VCL). Set the maximum current limit (ICL\_LIMIT) by placing the appropriate sense resistor between PS and SENSE\_ and the appropriate current-limit threshold set resistor (RCL) between CL and PS. When the load current is less than the maximum current limit, GATE\_ rises to 5.5V (typ) above VOUT\_ to fully enhance MOSFET Q1\_ and Q2\_. See the  $Current\text{-}Limit\ Threshold}$  section for more information on setting the current-limit threshold.

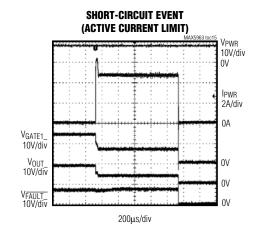

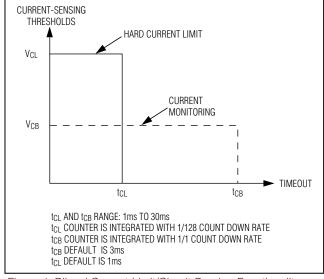

When the load attempts to draw more current than  $I_{CL\_LIMIT}$ , the MAX5963's GATE\_ pulldown current ( $I_{GD}$ ) regulates the current through Q1\_ and Q2\_, causing OUT\_ to act as a constant current source. The output current is limited to  $I_{CL\_LIMIT}$ . If the current-limit condition persists after the adjustable current-limit timeout period ( $I_{CL}$ ) has expired, the GATE\_ fast pulldown current ( $I_{GDF}$ ) quickly turns off GATE\_ to disconnect the load from the power supply. FAULT\_ asserts low under these conditions (Figure 1).

Figure 1. Bilevel Current-Limit/Circuit-Breaker Functionality

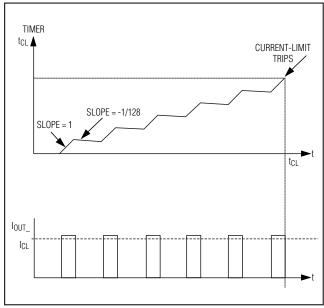

An external resistor connected to TCL and an internal 1/128 integrating counter determines the current-limit timeout. If the current-limit threshold is exceeded for more than roughly 100ns (comparator and logic delays), the timer counts up. Note that multiple consecutive overcurrent occurrences may cause the current-limit timer to trip (Figure 2).

During an output short-circuit event or a gross overload, the load current overshoots and causes VSENSE\_to exceed the fast pulldown current-limit threshold voltage (VTHF). The MAX5963 responds with much stronger GATE\_pulldown currents (IGDP\_ and/or IGDF\_) to quickly bring the load current back down to the programmed current limit.

In extreme cases where VSENSE\_ is less than VPS by more than 700mV (typ), the MAX5963 immediately pulls GATE1\_ and GATE2\_ low with a 1A (typ) peak pulldown current to disconnect the load from the power supply.

Following an overcurrent event, the gates of the external MOSFETs are held low (latched) if the device is in latchoff mode. Toggle ON\_ to restart the device under these conditions. If RETRY is pulled high or connected to BP or PS, the device pulls the gates high again following the automatic restart delay toffcl.

#### Current-Limit Threshold

The MAX5963 features adjustable current limits for channel A and channel B. Set the current-limit threshold voltage (VCL\_TH) for both channels by connecting a resistor, R<sub>CL</sub>, from CL to PS. Calculate V<sub>CL\_TH</sub> using the following equation:

where I<sub>CLSET</sub> is the 100 $\mu$ A (typ) current-limit set current shown in the *Electrical Characteristics* table.

Connect a sense resistor (RSENSE\_) between PS and SENSE\_ to set the individual current limits for channel A and channel B. Calculate the required sense resistor for each channel using the following equation:

$$R_{SENSE\_} = \frac{V_{CL\_TH}}{I_{CL\_LIMIT}}$$

where ICL\_LIMIT is the maximum channel current limit.

#### **Current-Limit Timeout**

The MAX5963 autoretry feature attempts to restart the device following the adjustable current-limit timeout, limiting the duty cycle of the MOSFETs under continuous fault conditions. The autoretry timeout is equal to 128 times the current-limit timeout:

$tOFFCL (ms) = 128 \times tCL (ms)$

Figure 2: Current-Limit Timeout Following Consecutive Overcurrent Events

Set the current-limit timeout from 1ms to 30ms by connecting a resistor between TCL and ground. See Figure 3 for resistor values and associated timeouts. Connect TCL to BP to select the 1ms (typ) default current-limit timeout.

#### Circuit Breaker

The MAX5963 features internal circuit-breaker circuitry that functions as a current monitor. Once the output current exceeds the circuit-breaker limit (ICB\_LIMIT), the circuit-breaker timer begins. When the circuit-breaker timeout (tCB) is reached, GATE\_ is pulled low and a fault condition is asserted (Figure 1).

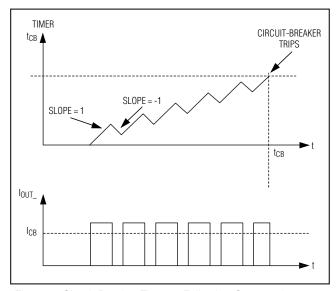

An external resistor connected to TCB and an internal 1/1 integrating counter determines the circuit-breaker timeout. If the circuit-breaker threshold is exceeded for more than roughly 100ns (comparator and logic delays), the timer counts up. Note that multiple consecutive circuit-breaker overcurrent occurrences may cause the circuit-breaker timer to trip (Figure 4).

Following a circuit-breaker event, the gates of the external MOSFETs are held low (latched) if the device is in latchoff mode. If RETRY is pulled high or connected to BP, the device pulls the gates high again following the automatic restart delay toffcb.

MIXIM

#### Circuit-Breaker Threshold

The MAX5963 features adjustable circuit-breaker limits for channels A and B. Set the circuit-breaker threshold voltage (V<sub>CB\_TH</sub>) for both channels by connecting a resistor, R<sub>CB</sub>, from CB to PS. Calculate V<sub>CB\_TH</sub> using the following equation:

where I<sub>CBSET</sub> is the 100µA (typ) circuit-breaker set current shown in the *Electrical Characteristics* table.

A sense resistor (RSENSE\_) between PS and SENSE\_sets the individual circuit-breaker limits for channels A and B. Calculate the circuit-breaker current limit (ICB\_LIMIT) for each channel using the following equation:

$$I_{CB\_LIMIT} = \frac{V_{CB\_TH}}{R_{SENSE}}$$

#### Circuit-Breaker Timeout

The MAX5963 autoretry feature attempts to restart after an adjustable circuit-breaker timeout. The autoretry timeout is equal to 128 times the circuit-breaker timeout:

$$toffcb (ms) = 128 \times tcb (ms)$$

Set the circuit-breaker timeout from 1ms to 30ms by connecting a resistor between TCB and ground. See Figure 3 for resistor values and associated timeouts. Connect TCB to BP to select the 3ms (typ) default circuit-breaker timeout.

Figure 3: Current-Limit/Circuit-Breaker Timeout vs. RTCL and RTCB Resistor Values

## Power-Supply ORing (GATEPS and GATEOR)

The MAX5963 controls two back-to-back n-channel power MOSFETs, QPS and QOR (see the *Typical Operating Circuit*), for system power-on/power-off control and ORing functionality. GATEPS is pulled high once VPWR exceeds the UVLO threshold and a valid combination of EN\_ inputs is received. Initially, GATEOR is off and the load current conducts through the body diode of QOR.

GATEOR rises to 5.5V above VPWR when the voltage across the sense resistors (VSENSEA + VSENSEB)/2 exceeds the ORing threshold, enhancing QOR. QOR's low RDS(ON) provides a very low voltage drop across its source to drain, which results in less power dissipation and heat generation in the power-supply path than a traditional diode.

Connect a resistor from OR to PS to set the ORing threshold (VOR\_TH). Calculate the ORing threshold using the following equation:

where  $I_{ORSET}$  is the 100 $\mu$ A (typ) ORing threshold set current, and  $R_{OR}$  is the resistance connected between OR and PS.

The MAX5963 continuously monitors the voltage drops across the sense resistors, VSENSEA and VSENSEB. QOR turns off rapidly when the voltage across the sense resistors decreases below the VOR threshold minus its hysteresis. See Table 1.

Figure 4: Circuit-Breaker Timeout Following Consecutive Overcurrent Events

**Table 1. ORing Protection Truth Table**

| INPUT (VSENSEA + VSENSEB)/2 > VOR | OUTPUT<br>GATEOR | DESCRIPTION                                                                                                                         |

|-----------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Yes                               | On               | Normal operation. ORing MOSFET (QOR) is on to minimize power dissipation.                                                           |

| No                                | Off              | ORing protection. ORing MOSFET (QOR) is off, preventing current flowing backward into the system's power supply, V <sub>PWR</sub> . |

#### **Undervoltage Lockout**

The MAX5963 dual-channel, independent current-limit switches have independent ON/OFF control. Both channels operate from 7.5V to 76V and have default 6.5V (typ) undervoltage lockout thresholds. The external MOSFETs remain off as long as VPS < 6.5V or VON\_ < VONTH. The UVLO thresholds are programmable by connecting a resistive voltage-divider between ON\_ and GND. When VPS is greater than 7.5V and VON\_ exceeds the 1.24V (typ) threshold, GATE1\_ and GATE2\_ enhance to 5.5V, with respect to OUT\_ and the MAX5963 switch goes into normal operation.

Calculate the resistor values to program the switches' individual turn-on threshold voltages using the following formula:

$$R_1 = \left(\frac{V_{TURN}_{ON}}{1.24V} - 1\right) \times R_2$$

where V<sub>TURN\_ON</sub> is the desired turn-on voltage of channel A and/or B. R<sub>1</sub> and R<sub>2</sub> create a resistive divider from PS to ON\_ (see the *Typical Operating Circuit*).

When operating the MAX5963, ON\_ must remain above its 1.24V (typ) threshold. If VON\_ falls below the threshold and hysteresis for more than 10µs (typ), the power-supply MOSFETs turn off. This allows the power supply to disconnect from the load in the event of a fault condition such as shorting of the output to a different power-supply voltage or to a FireWire signal pin. If possible transient conditions exist that may exceed 10µs (typ) at the main power-supply line (PS), place an RC filter at

ON\_ to reject transient voltage dips to prevent unnecessary power-supply interruptions.

### Current-Fault Status Output (FAULT\_)

FAULTA and FAULTB are high-voltage, open-drain outputs that pull low when a current-limit or circuit-breaker fault shutdown has occurred. FAULTA and FAULTB remain low until the next startup cycle. FAULTA and FAULTB are capable of sinking up to 5mA when asserted.

#### Autoretry/Latchoff Fault Management

The MAX5963 autoretry feature attempts to restart after an adjustable current-limit or circuit-breaker timeout, limiting the duty cycle of the MOSFETs under continuous fault conditions. Connect RETRY to BP or PS for autorestart mode. Leave RETRY floating to select latchoff mode after a current-limit/circuit-breaker timeout.

FAULT\_ deasserts every time a restart attempt is made.

#### **Logic Inputs**

#### Power-Supply Enables (ENX, ENY, and ENZ)

Three enable inputs, ENX, ENY, and ENZ, can be used to control power-on/power-off.

ENZ is a logic input that is ANDed with the OR combination of ENX and ENY. Apply a voltage greater than 1.8V (min) to ENZ to ensure that GATEPS is pulled high when VPWR rises above the 6.5V (typ) PWR undervoltage lockout threshold.

Pull ENZ low to put the MAX5963 into PWR standby or shutdown mode. The MAX5963 draws less than  $10\mu$ A from PWR in shutdown. See Table 2.

**Table 2. Logic Input Truth Table**

| INPUT                | OUTPUT | DESCRIPTION                                                                                                                          |  |  |

|----------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|

| (ENX OR ENY) AND ENZ | GATEPS | DESCRIPTION                                                                                                                          |  |  |

| L                    | Off    | System Power-Off Mode. The MAX5963 draws < 10µA from PWR after [(ENX or ENY) and ENZ] goes low for more than t <sub>SHDN</sub> time. |  |  |

| Н                    | On     | Enable System Power. The system power supply, V <sub>SUPPLY</sub> , provides power to the FireWire ports.                            |  |  |

The MAX5963 is capable of being powered through PWR or through channel A or B. Pull ENZ low and apply a voltage to either channel to power the device. In this mode, BP is powered by VPs according to Table 3.

#### Fast-Off/Slow-On (FOSO) Protection

GATE1A, GATE2A, GATE1B, and GATE2B immediately pull low when FOSO exceeds the 1.24V (typ) threshold. The MAX5963 waits for the 1s (typ) turn-on delay once FOSO falls below the threshold hysteresis before allowing either channel to turn back on. See the *FireWire Power Management* section for more information.

### Applications Information

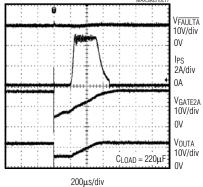

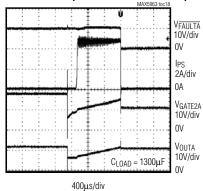

### **Startup Considerations**

Set the appropriate current-limit threshold for successful startup. A successful startup is dependent on the MAX5963 current-limit threshold and timeout period. A large capacitor at the output results in a charging current equivalent to the current-limit threshold and may cause the MAX5963 to exceed its 1ms (typ) default timeout period if the current-limit threshold is set too low. Use the following formula to compute the minimum current-limit setting:

$$I_{CL\_LIMIT} > \frac{C_{OUT} \times V_{PS}}{t_{CL}} + I_{LOAD}$$

where I<sub>CL\_LIMIT</sub> is the programmed current limit, C<sub>OUT</sub> is the capacitor at OUT\_, V<sub>PS</sub> is the supply voltage, t<sub>CL</sub> is the adjustable current-limit timeout period, and I<sub>LOAD</sub> is the load current during startup. With V<sub>PS</sub> = 12V, C<sub>OUT</sub> = 220 $\mu$ F, t<sub>CL</sub> = 1ms, and I<sub>LOAD</sub> = 0, set the MAX5963 current limit greater than 2.6A. This calculation does not include tolerances.

### Choosing Rsense\_

Select sense resistors, RSENSEA and RSENSEB, which cause the circuit-breaker voltage drop at a current-

limit/circuit-breaker level above the maximum normal operating current. Typically, set the current limit at 1.2 to 1.5 times the nominal load current.

Choose the sense resistor power rating to accommodate a current-limit condition:

where PSENSE\_ is the power dissipated across RSENSE\_during a current-limit/circuit-breaker fault.

### **MOSFET Selection**

Select external MOSFETs according to the application current level. The MOSFETs' on-resistance (RDS(ON)) should be chosen low enough to have minimum voltage drop at full load to limit the MOSFET power dissipation. High RDS(ON) also causes large output ripple if there is a pulsating load. Determine the device power rating to accommodate a short-circuit condition on the board, at startup, and when the device is in autoretry mode. During normal operation, the external MOSFETs dissipate little power. The power dissipated in normal operation is:

$$P = I_{LOAD^2} \times R_{DS(ON)}$$

The most power dissipation occurs during a current-limit event, resulting in high power dissipated in Q\_ during the current-limit period for the MAX5963. Calculate the power dissipated across Q\_ during this period using the following equation:

where VSENSE\_ is the voltage across the current-sense resistor, RSENSE\_, VPS is the input voltage and ICL\_LIMIT is the programmed current limit. Though there are two MOSFETs in series at the outputs, the safest assumption is that all of the current-limiting power dissipation occurs in one of the two MOSFETs; perfect sharing of the current-limit voltage drop is unlikely.

| Table 3. BP | Voltage in | Standby | Mode |

|-------------|------------|---------|------|

|-------------|------------|---------|------|

| PWR AND PS CONFIGURATION                  | ENZ   | PS_UVLO | V <sub>BP</sub> (V)    |

|-------------------------------------------|-------|---------|------------------------|

| V <sub>PS</sub> > V <sub>PWR</sub> - 0.1V | Low   | High    | V <sub>PS</sub> - 0.7V |

| V <sub>PS</sub> > V <sub>PWR</sub> - 0.1V | Low   | Low     | V <sub>PS</sub>        |

| V <sub>PS</sub> < V <sub>PWR</sub> - 0.1V | Low   | Low     | V <sub>PS</sub>        |

| V <sub>PS</sub> < V <sub>PWR</sub> - 0.1V | High* | Low     | V <sub>PS</sub>        |

| V <sub>PS</sub> < V <sub>PWR</sub> - 0.1V | High* | High    | VpwR                   |

<sup>\*</sup>ENX or ENY must be high to turn on GATEPS.

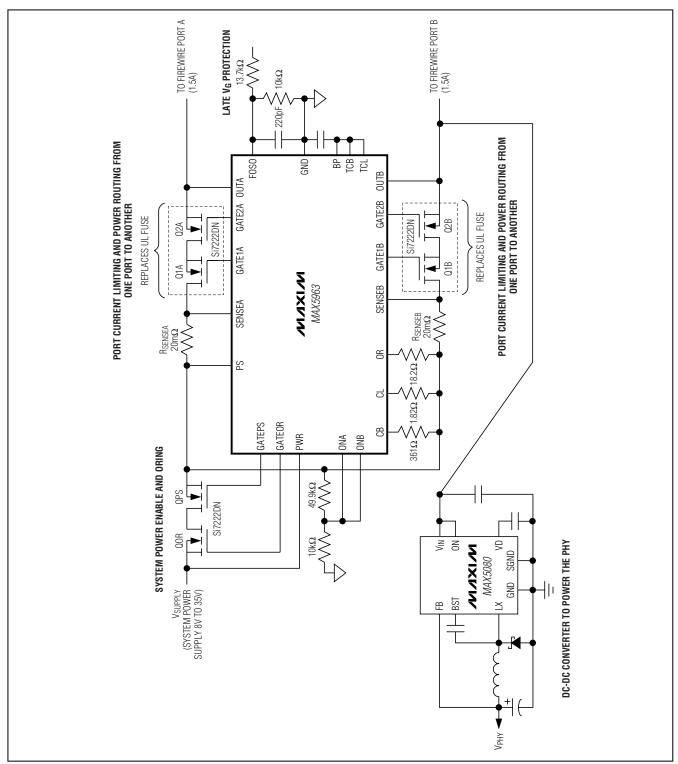

#### FireWire Power Management

The MAX5963 is an excellent solution for FireWire port control and protection. In a two-port power-sourcing application, the MAX5963 can route system power to both ports, or it can allow either port to pass power to the other port, while blocking reverse current to the system power supply.

In these applications, it is important that no loads be placed on the PS node of the application circuit because VPS is not protected against overcurrent faults. Loads should be placed at the port connections OUTA and OUTB instead, as shown in Figure 5.

The fast-off, slow-on input can be used to implement late VG protection for FireWire ports. In the event that a FireWire device makes connection with VP prior to VG, protection diodes in the load device can apply high

voltage to the signal lines, damaging the host PHY. Connect the FOSO input as shown in Figure 5 to sense high voltage on the signal lines, and the MAX5963 immediately disconnects until VG is connected.

#### **Transient Protection**

If PS or OUT\_ experiences a fast transient rise in voltage, the drain-to-gate overlap capacitance of GATE1\_ and/or GATE2\_ FETs may be sufficient to enhance both of the transistors, allowing current to flow. If the circuit is subjected to large transients, connect capacitors from the gate to source across the appropriate MOS-FET to prevent the overlap capacitance from turning on the device. This causes the turn-off time of the FETs to increase due to the additional discharge of the capacitor. Use the minimum capacitor value that prevents reverse currents from flowing in hot-plug situations.

Table 4. FireWire Port Powering and Late Vg (FOSO) Protection Truth Table

| INPUT |     | ОИТРИТ |        | DESCRIPTION |                                                             |  |

|-------|-----|--------|--------|-------------|-------------------------------------------------------------|--|

| FOSO  | ONA | ONB    | GATE_A | GATE_B      | DESCRIPTION                                                 |  |

| Н     | Χ   | Χ      | Off    | Off         | Late V <sub>G</sub> event, all ports are off.               |  |

| L     | Н   | Χ      | On     | _           | Enable port A power.                                        |  |

| L     | L   | Χ      | Off    | _           | Disable port A power.                                       |  |

| L     | Χ   | H      | _      | On          | Enable port B power.                                        |  |

| L     | Χ   | L      |        | Off         | Disable port B power.                                       |  |

| L     | Н   | Ι      | On     | On          | Enable port A, B power and power routing between the ports. |  |

X = Don't care.

Figure 5. MAX5963 FireWire Application

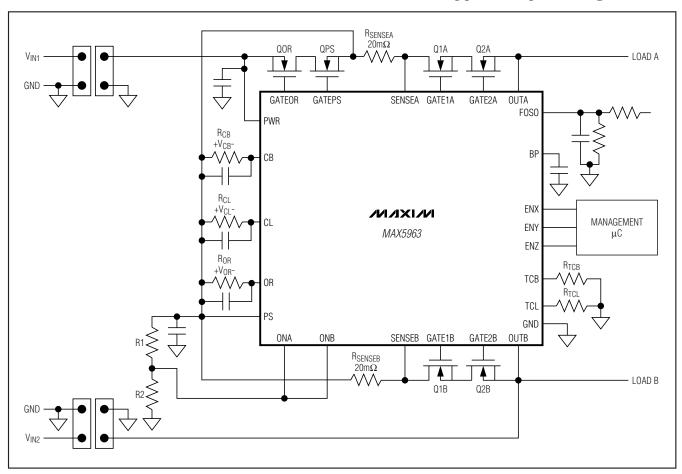

### **Typical Operating Circuit**

### **Chip Information**

### \_Package Information

PROCESS: BICMOS

For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 40 TQFN-EP   | T4066+5      | <u>21-0141</u> |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.