## Automotive chip for single and dual H-bridge

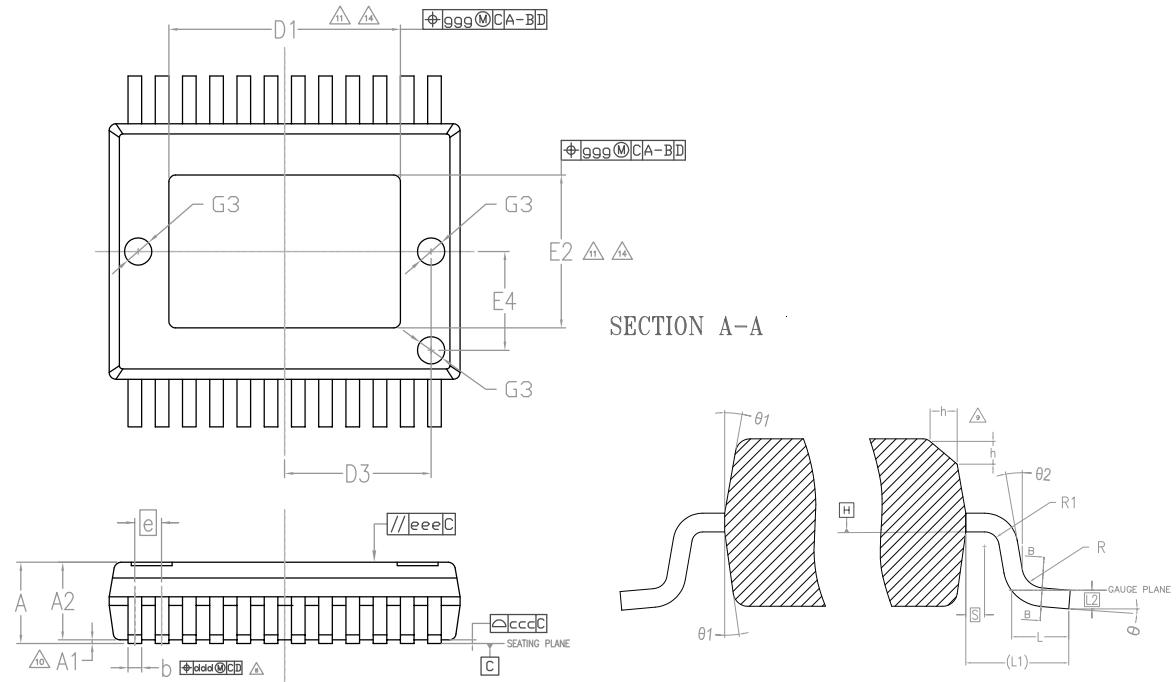

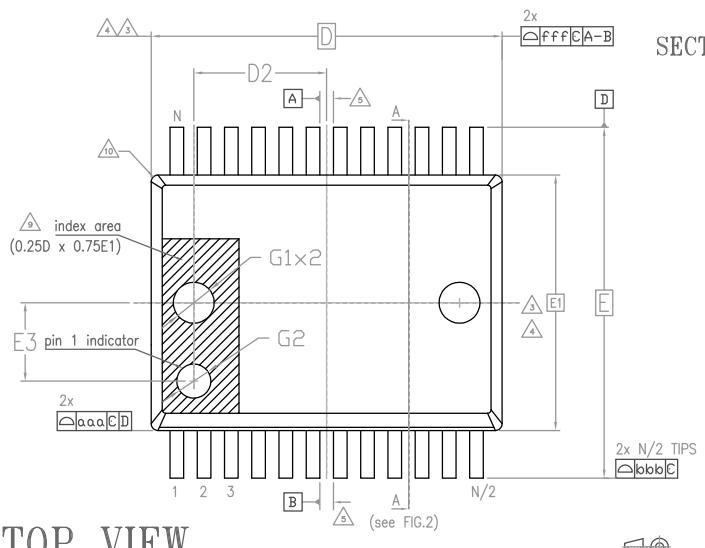

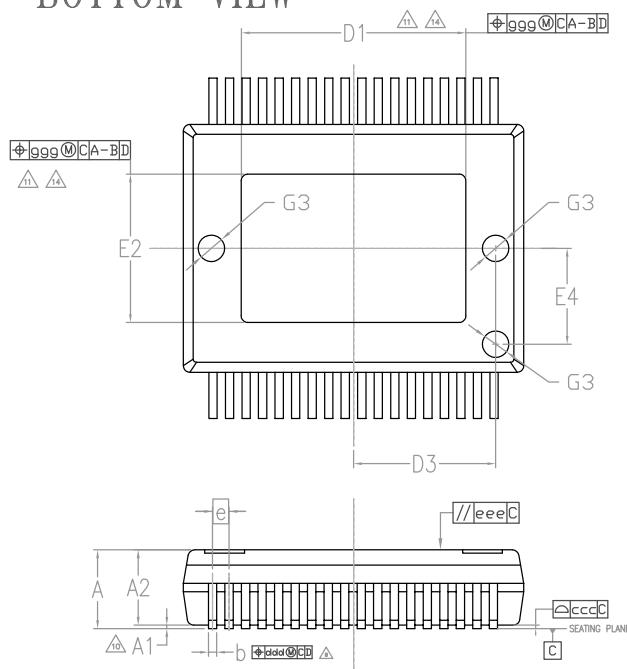

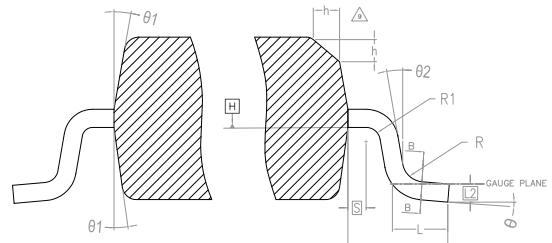

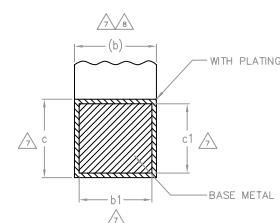

**PowerSSO24**

**PowerSSO36**

### Features

- AEC-Q100 qualified

- Full path  $R_{DS(on)}$  less than 540 mΩ

- Nominal continuous load current > 3 A

- Operating battery supply voltage 4.5 V to 28 V

- Operating VDD supply voltage 4.5 V to 5.5 V

- All ECU internal pins can withstand up to 18 V

- Output switching frequency up to 20 kHz

- Monitoring of VDD supply voltage including bidirectional switch-off pin NABE

- Overtemperature and short-circuit protection

- Full diagnosis capability

- Output stage with SPI-adjustable current limitation 5-8.6 A in 3 steps (two-point regulation)

- Fast switch-off open-drain input/output

- Current-monitoring with current feedback output signal CF

- Reliable full diagnostic capability

- Settable chip-address via bond-wire configuration on the silicon or E-Fuse

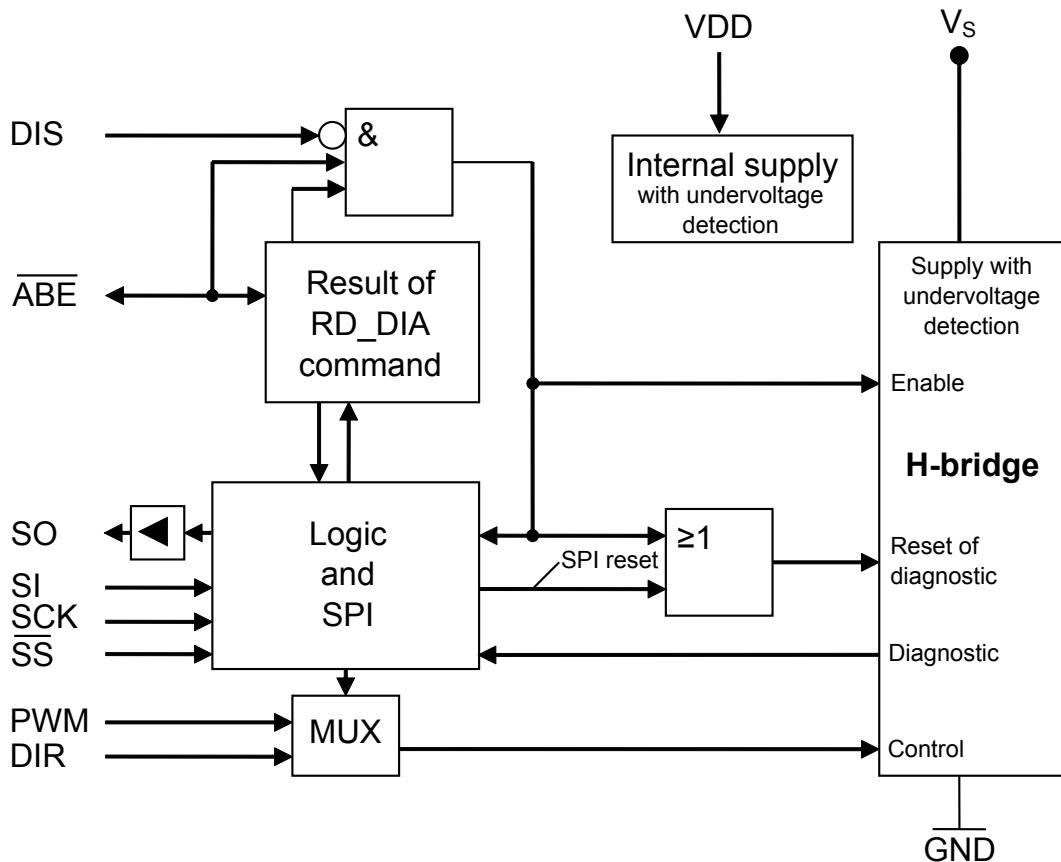

- SPI-interface for configuration and diagnosis

- Error history in diagnosis register

- Two independent enable pins: "NABE" and "DIS"

- Control of power stages by SPI or two input signals, PWM and DIR (configurable via SPI)

- Logic levels 5 V compatible

- Conformity to improved EMC requirements due to smart H-bridge switching

- Full ISO 26262 compliant, ASIL-B (D) systems ready

| Product status links |                        |  |

|----------------------|------------------------|--|

|                      | <a href="#">L9969S</a> |  |

|                      | <a href="#">L9969T</a> |  |

|                      | <a href="#">L9969U</a> |  |

| Product summary |         |               |

|-----------------|---------|---------------|

| Order code      | Package | Packing       |

| L9969S          | PSSO24  |               |

| L9969T          | PSSO36  | Tape and reel |

| L9969U          |         |               |

### Description

[L9969S](#)/[L9969U](#) and [L9969T](#) are single and dual integrated H-bridges for resistive and inductive loads featuring output current direction and supervising functions.

The PowerSSO24 houses one full H-bridge, while the PowerSSO36 houses both two H-bridges that can work in parallel, through independent input driving commands.

Target application ranges from throttle control actuators to exhaust gas recirculation control valves in automotive domain to a more general use to drive DC and Stepper motors.

## 1 Block diagram and pin description

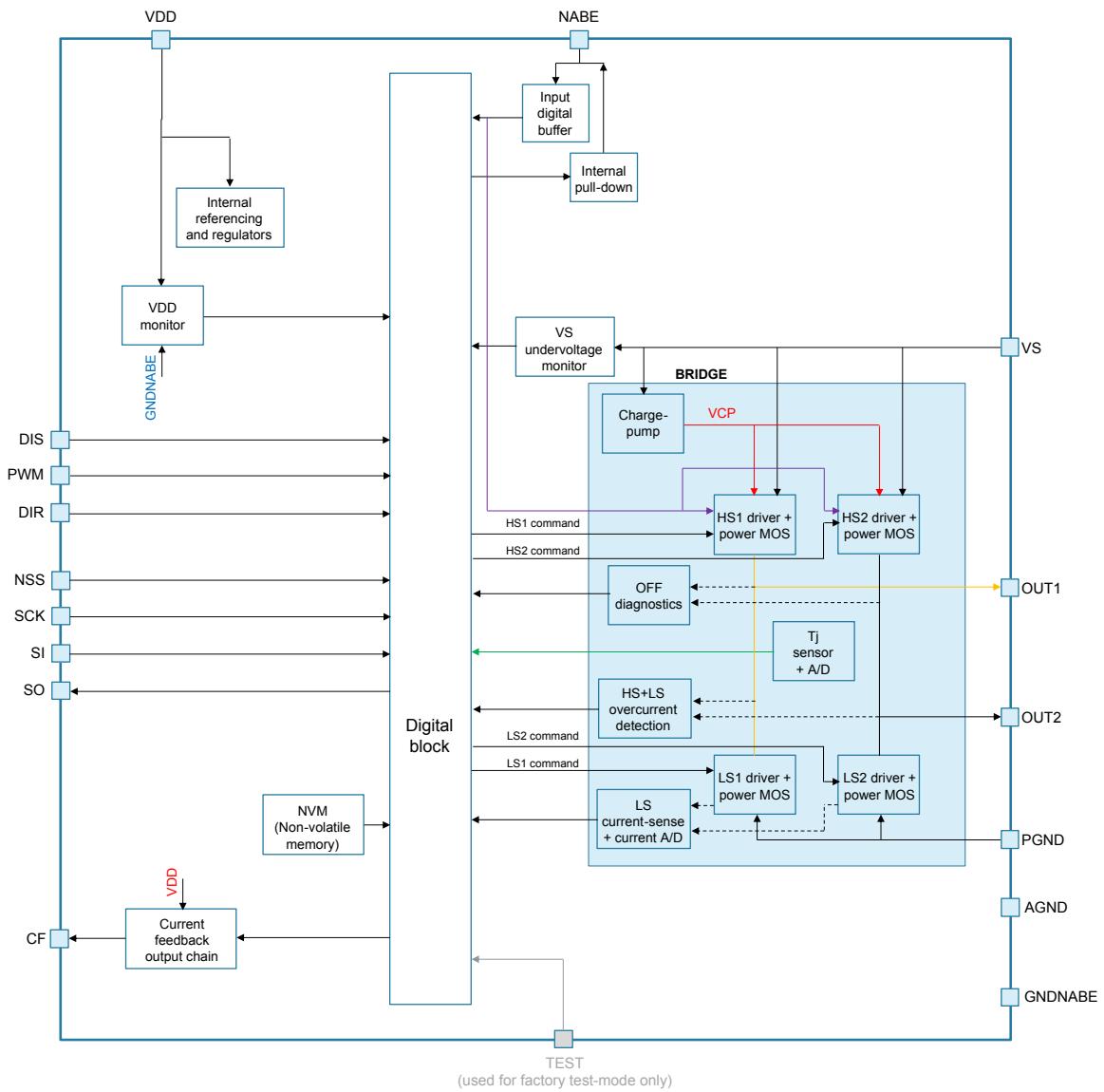

## 1.1 Block diagram

**Figure 1. L9969S/L9969U single bridge IC block diagram**

**Figure 2. L9969T twin bridge IC block diagram**

## 1.2 Pin description

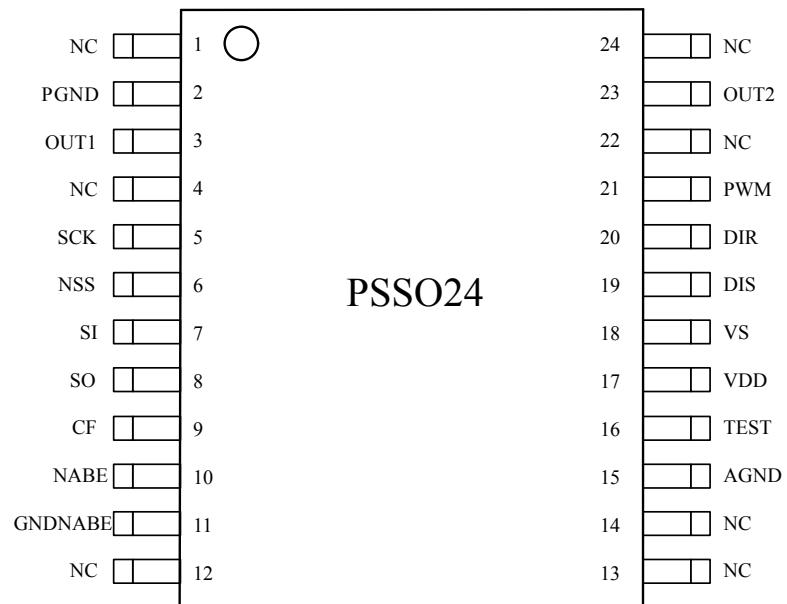

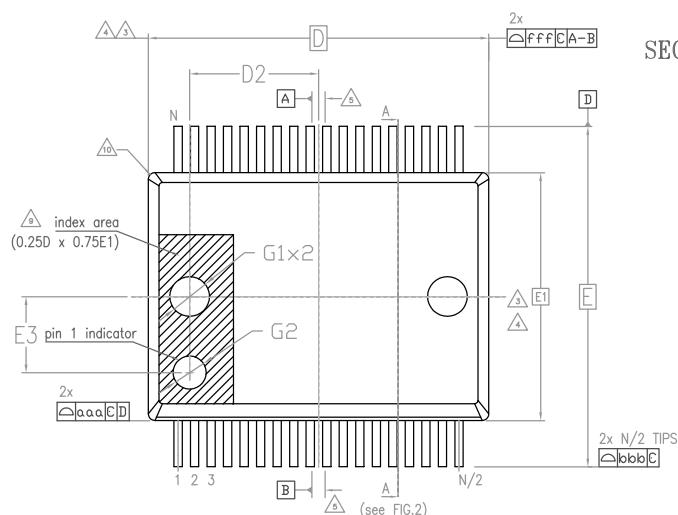

Figure 3. L9969S - pin connection (top view)

Figure 4. L9969U - pin connection (top view)

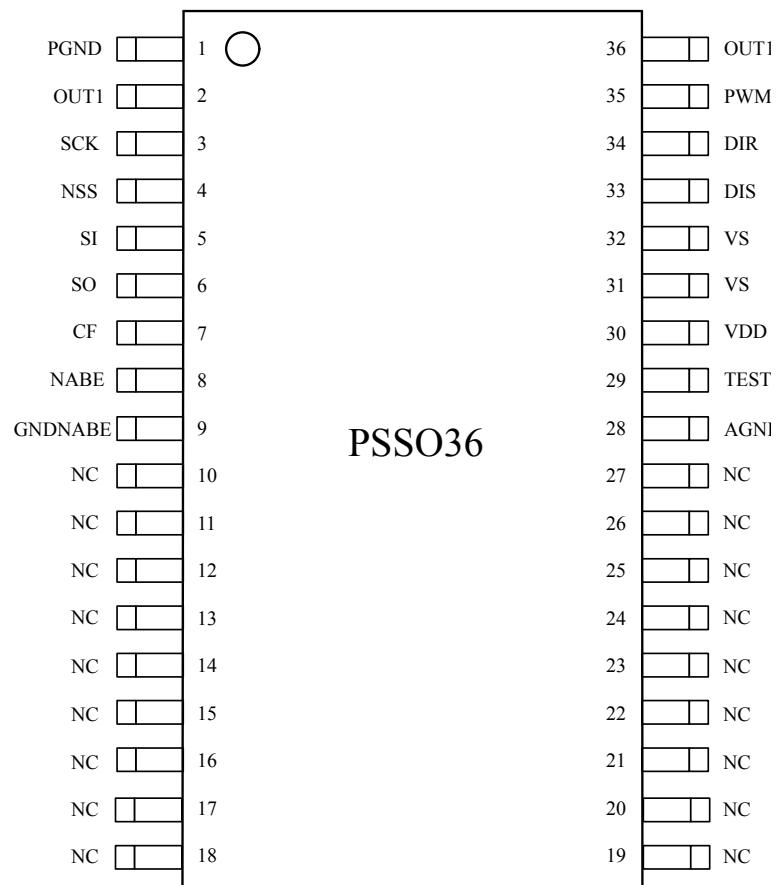

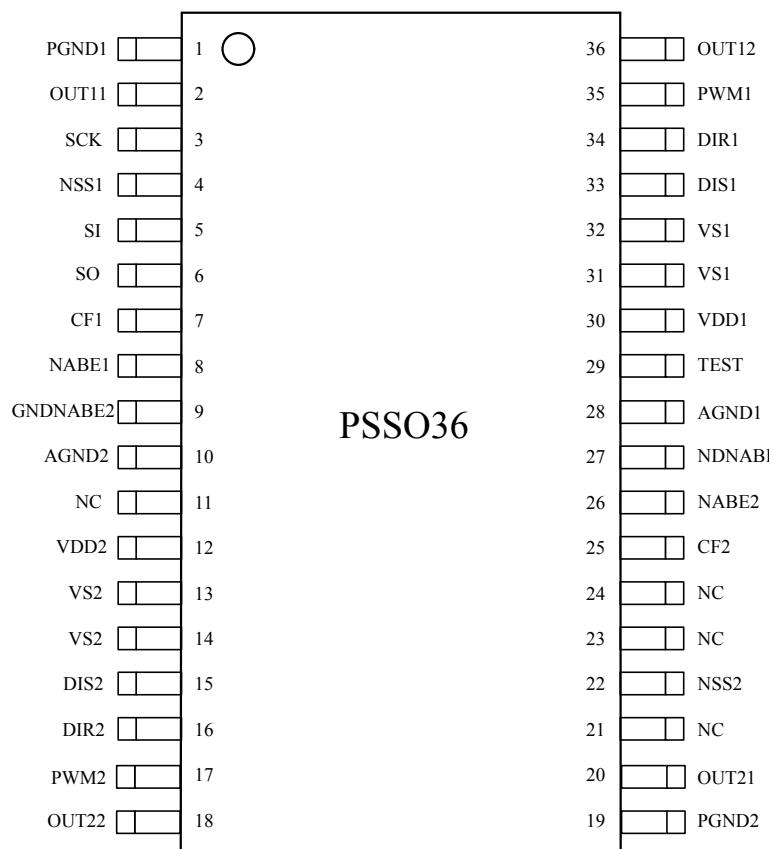

Figure 5. L9969T - pin connection (top view)

### 1.3 Pin definitions and functions

Table 1. L9969S pin-out

| Pin # | Pin name | Description                                                                                                                                                                   | I/O type | Class  |

|-------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|

| 1     | NC       | Not connected                                                                                                                                                                 | -        | -      |

| 2     | PGND     | Power Ground of H-bridge                                                                                                                                                      | G        | Global |

| 3     | OUT1     | Output 1 of H-bridge                                                                                                                                                          | O        | Global |

| 4     | NC       | Not connected                                                                                                                                                                 | -        | -      |

| 5     | SCK      | SPI-Clock input of H-bridge                                                                                                                                                   | I        | Local  |

| 6     | NSS      | SPI-Slave Select input of H-bridge                                                                                                                                            | I        | Local  |

| 7     | SI       | SPI-Slave In (data receive) input of H-bridge                                                                                                                                 | I        | Local  |

| 8     | SO       | SPI-Slave Out (data transceive) output of H-bridge                                                                                                                            | O        | Local  |

| 9     | CF       | Current feedback of H-bridge.<br>Signal is proportional to the positive current in active LS-transistor of H-bridge.                                                          | O        | Local  |

| 10    | NABE     | Bidirectional Enable/Disable in-/output.<br>Open-drain output, switched to low at VDD over and undervoltage condition.<br>Low level disables the power stage. (OUT1 and OUT2) | I/O      | Local  |

| 11    | GNDNABE  | Reference Ground of VDD-monitoring.                                                                                                                                           | G        | Local  |

| 12    | NC       | Not connected                                                                                                                                                                 | -        | -      |

| 13    | NC       | Not connected                                                                                                                                                                 | -        | -      |

| Pin # | Pin name | Description                                                                                             | I/O type | Class  |

|-------|----------|---------------------------------------------------------------------------------------------------------|----------|--------|

| 14    | NC       | Not connected                                                                                           | -        | -      |

| 15    | AGND     | Ground connection of H-bridge                                                                           | G        | Local  |

| 16    | TEST     | Factory test-mode activation                                                                            | I        | Local  |

| 17    | VDD      | 5 V Supply for H-bridge. Input for VDD monitoring.                                                      | P        | Local  |

| 18    | VS       | Supply voltage for H-bridge power stage                                                                 | P        | Global |

| 19    | DIS      | Disable input for H-bridge.<br>High-level disables the power stage (OUT1 and OUT2)                      | I        | Local  |

| 20    | DIR      | Direction input of H-bridge.                                                                            | I        | Local  |

| 21    | PWM      | PWM input of H-bridge.<br>Controls the frequency and the duty cycle of the power stage (OUT1 and OUT2). | I        | Local  |

| 22    | NC       | Not connected                                                                                           | -        | -      |

| 23    | OUT2     | Output 2 of H-bridge.                                                                                   | O        | Global |

| 24    | NC       | Not connected                                                                                           | -        | -      |

| -     | Exp. PAD | Exposed pad is connected to AGND                                                                        | -        | -      |

Note: **Legenda:** I = Input, O = Output, P = Power Supply, G = Ground, I/O = Input/Output

**Table 2. L9969U pin-out**

| Pin # | Pin name | Description                                                                                                                                                                   | I/O type | Class  |

|-------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|

| 1     | PGND     | Power Ground of H-bridge                                                                                                                                                      | G        | Global |

| 2     | OUT1     | Output 1 of H-bridge                                                                                                                                                          | O        | Global |

| 3     | SCK      | SPI-Clock input                                                                                                                                                               | I        | Local  |

| 4     | NSS      | SPI-Slave Select input                                                                                                                                                        | I        | Local  |

| 5     | SI       | SPI-Slave In (data receive) input                                                                                                                                             | I        | Local  |

| 6     | SO       | SPI- Slave Out (data transceive) output                                                                                                                                       | O        | Local  |

| 7     | CF       | Current feedback of H-bridge<br>Signal is proportional to the positive current in active LS-transistor of H-bridge.                                                           | O        | Local  |

| 8     | NABE     | Bidirectional Enable/Disable in-/output.<br>Open-drain output, switched to low at VDD over and undervoltage condition.<br>Low level disables the power stage. (OUT1 and OUT2) | I/O      | Local  |

| 9     | GNDNABE  | Reference Ground for VDD-monitoring of H-bridge                                                                                                                               | G        | Local  |

| 10    | NC       | Not connected.                                                                                                                                                                | -        | -      |

| 11    | NC       | Not connected.                                                                                                                                                                | -        | -      |

| 12    | NC       | Not connected.                                                                                                                                                                | -        | -      |

| 13    | NC       | Not connected.                                                                                                                                                                | -        | -      |

| 14    | NC       | Not connected.                                                                                                                                                                | -        | -      |

| 15    | NC       | Not connected.                                                                                                                                                                | -        | -      |

| 16    | NC       | Not connected.                                                                                                                                                                | -        | -      |

| 17    | NC       | Not connected.                                                                                                                                                                | -        | -      |

| 18    | NC       | Not connected.                                                                                                                                                                | -        | -      |

| 19    | NC       | Not connected.                                                                                                                                                                | -        | -      |

| 20    | NC       | Not connected.                                                                                                                                                                | -        | -      |

| Pin # | Pin name | Description                                                                                            | I/O type | Class  |

|-------|----------|--------------------------------------------------------------------------------------------------------|----------|--------|

| 21    | NC       | Not connected.                                                                                         | -        | -      |

| 22    | NC       | Not connected.                                                                                         | -        | -      |

| 23    | NC       | Not connected.                                                                                         | -        | -      |

| 24    | NC       | Not connected.                                                                                         | -        | -      |

| 25    | NC       | Not connected.                                                                                         | -        | -      |

| 26    | NC       | Not connected.                                                                                         | -        | -      |

| 27    | NC       | Not connected.                                                                                         | -        | -      |

| 28    | AGND     | Ground connection for H-bridge (Device ground)                                                         | G        | Local  |

| 29    | TEST     | Factory test-mode activation                                                                           | I        | Local  |

| 30    | VDD      | 5 V Supply for H-bridge. Input for VDD monitoring.                                                     | P        | Local  |

| 31    | VS       | Supply voltage of H-bridge power stage                                                                 | P        | Global |

| 32    | VS       | Supply voltage of H-bridge power stage                                                                 | P        | Global |

| 33    | DIS      | Disable input of H-bridge.<br>High-level disables the power stage (OUT1 and OUT2)                      | I        | Local  |

| 34    | DIR      | Direction input of H-bridge                                                                            | I        | Local  |

| 35    | PWM      | PWM input of H-bridge<br>Controls the frequency and the duty cycle of the power stage (OUT1 and OUT2). | I        | Local  |

| 36    | OUT2     | Output 2 of H-bridge                                                                                   | O        | Global |

| -     | Exp. PAD | Exposed pad is connected to AGND                                                                       | -        | -      |

Note: **Legenda:** I = Input, O = Output, P = Power Supply, G = Ground, I/O = Input/Output

**Table 3. L9969T pin-out**

| Pin # | Pin name | Description                                                                                                                                                                      | I/O type | Class  |

|-------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|

| 1     | PGND1    | Power Ground of H-bridge1                                                                                                                                                        | G        | Global |

| 2     | OUT11    | Output 1 of H-bridge1                                                                                                                                                            | O        | Global |

| 3     | SCK      | SPI-Clock input                                                                                                                                                                  | I        | Local  |

| 4     | NSS1     | SPI-Slave Select input of H-bridge1                                                                                                                                              | I        | Local  |

| 5     | SI       | SPI-Slave In (data receive) input                                                                                                                                                | I        | Local  |

| 6     | SO       | SPI-Slave Out (data transceive) output                                                                                                                                           | O        | Local  |

| 7     | CF1      | Current feedback for H-bridge1.<br>Signal is proportional to the positive current in active LS-transistor of H-bridge1.                                                          | O        | Local  |

| 8     | NABE1    | Bidirectional Enable/Disable in-/output.<br>Open-drain output, switched to low at VDDx over and undervoltage condition.<br>Low level disables the power stage. (OUT11 and OUT12) | I/O      | Local  |

| 9     | GNDNABE2 | Reference Ground for VDD2-monitoring of H-bridge 2                                                                                                                               | G        | Local  |

| 10    | AGND2    | Ground connection for H-bridge2 (Device ground)                                                                                                                                  | G        | Local  |

| 11    | NC       | Not connected.                                                                                                                                                                   | -        | -      |

| 12    | VDD2     | 5 V Supply for H-bridge (2). Input for VDD (2) monitoring.                                                                                                                       | P        | Local  |

| 13    | VS2      | Supply voltage for H-bridge2 power stage                                                                                                                                         | P        | Global |

| 14    | VS2      | Supply voltage for H-bridge2 power stage                                                                                                                                         | P        | Global |

| 15    | DIS2     | Disable input for H-bridge2.                                                                                                                                                     | I        | Local  |

| Pin # | Pin name | Description                                                                                                                                                                      | I/O type | Class  |

|-------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|

|       |          | High-level disables the power stage (OUT21 and OUT22)                                                                                                                            |          |        |

| 16    | DIR2     | Direction input of H-bridge2.                                                                                                                                                    | I        | Local  |

| 17    | PWM2     | PWM input of H-bridge2.<br>Controls the frequency and the duty cycle of the power stage (OUT21 and OUT22).                                                                       | I        | Local  |

| 18    | OUT22    | Output 2 of H-bridge2                                                                                                                                                            | O        | Global |

| 19    | PGND2    | Power ground connection for H-bridge2.                                                                                                                                           | G        | Global |

| 20    | OUT21    | Output 1 of H-bridge2                                                                                                                                                            | O        | Global |

| 21    | NC       | not connected.                                                                                                                                                                   | -        | -      |

| 22    | NSS2     | SPI-Slave Select input of H-bridge2.                                                                                                                                             | I        | Local  |

| 23    | NC       | not connected.                                                                                                                                                                   | -        | -      |

| 24    | NC       | not connected.                                                                                                                                                                   | -        | -      |

| 25    | CF2      | Current feedback of H-bridge2.<br>Signal is proportional to the positive current in active LS-transistor of H-bridge2.                                                           | O        | Local  |

| 26    | NABE2    | Bidirectional Enable/Disable in-/output.<br>Open-drain output, switched to low at VDDx over and undervoltage condition.<br>Low level disables the power stage. (OUT21 and OUT22) | I/O      | Local  |

| 27    | GNDNABE1 | Reference Ground of VDD1-monitoring of H-bridge 1                                                                                                                                | G        | Local  |

| 28    | AGND1    | Ground connection for H-bridge1 (Device ground)                                                                                                                                  | G        | Local  |

| 29    | TEST     | Factory test-mode activation                                                                                                                                                     | I        | Local  |

| 30    | VDD1     | 5 V Supply for H-bridge1. Input for VDD1 monitoring.                                                                                                                             | P        | Local  |

| 31    | VS1      | Supply voltage of H-bridge1 power stage                                                                                                                                          | P        | Global |

| 32    | VS1      | Supply voltage of H-bridge1 power stage                                                                                                                                          | P        | Global |

| 33    | DIS1     | Disable input of H-bridge1.<br>High-level disables the power stage (OUT11 and OUT12)                                                                                             | I        | Local  |

| 34    | DIR1     | Direction input of H-bridge1.                                                                                                                                                    | I        | Local  |

| 35    | PWM1     | PWM input of H-bridge1.<br>Controls the frequency and the duty cycle of the power stage (Out11 and Out 12).                                                                      | I        | Local  |

| 36    | OUT12    | Output 2 of H-bridge1.                                                                                                                                                           | O        | Global |

| -     | Exp. PAD | Exposed pad is connected to AGNDx                                                                                                                                                | -        | -      |

Note:

Legenda: I = Input, O = Output, P = Power Supply, G = Ground, I/O = Input/Output

## 2 Electrical specifications

### 2.1 Operating range

Within the operating range the part operates as specified and without parameter deviations. The device may not operate properly if maximum operating conditions are exceeded.

Once taken beyond the operative ratings and returned back within, the part will recover with no damage or degradation.

The voltages are referred to ground, and currents are assumed positive, when the current flows into the pin.

**Table 4. Operating range**

| Symbol                 | Parameter                                                     | Condition                                                                     | Min  | Typ | Max | Unit |

|------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------|------|-----|-----|------|

| VS_or                  | VS operative range                                            | -                                                                             | 5    | -   | 18  | V    |

| VDD_or                 | VDD operative range                                           | -                                                                             | 4.5  | -   | 5.2 | V    |

| T <sub>j</sub>         | Junction temperature                                          | -                                                                             | -40  | -   | 150 | °C   |

| V <sub>VS_slew</sub>   | Maximum slew rate on V <sub>S</sub> (no change of parameters) | VDD = 5 V<br>I <sub>OUT</sub> = 3 A<br>V <sub>S</sub> = 6 V, 10 V, 14 V, 18 V | -    | -   | 20  | V/μs |

| V <sub>GND_DELTA</sub> | Voltage differences between GND pins                          | -                                                                             | -0.3 | -   | 0.3 | V    |

### 2.2 Thermal data

**Table 5. Temperature data**

| Symbol                     | Description                                                  | Min | Typ  | Max | Unit |

|----------------------------|--------------------------------------------------------------|-----|------|-----|------|

| T <sub>amb</sub>           | Operating temperature (ECU environment)                      | -40 | -    | 125 | °C   |

| T <sub>j</sub>             | Operating junction temperature                               | -40 | -    | 150 | °C   |

| T <sub>stg</sub>           | Storage temperature                                          | -55 | -    | 150 | °C   |

| R <sub>Th j-amb</sub>      | Thermal resistance junction-to-ambient for L9969T PSSO36     | -   | 23.9 | -   | °C/W |

| R <sub>Th j-amb</sub>      | Thermal resistance junction-to-ambient for L9969S PSSO36     | -   | 25.4 | -   | °C/W |

| R <sub>Th j-amb</sub>      | Thermal resistance junction-to-ambient for L9969S PSSO24     | -   | 25.4 | -   | °C/W |

| R <sub>Th j-case_bot</sub> | Thermal resistance junction-to-case bottom for L9969T PSSO36 | -   | 1    | -   | °C/W |

| R <sub>Th j-case_bot</sub> | Thermal resistance junction-to-case bottom for L9969S PSSO36 | -   | 2    | -   | °C/W |

| R <sub>Th j-case_bot</sub> | Thermal resistance junction-to-case bottom for L9969S PSSO24 | -   | 2    | -   | °C/W |

#### 2.2.1 Temperature and load profile

The IC is designed for temperature profile that is transferred for T<sub>j</sub> = 175 °C at t ≥ 1500 h.

## 2.3 Absolute maximum ratings

### 2.3.1 Supply voltage

There is no special sequence to switch on the different voltages ( $V_S$ , VDD and voltages on any input pins).

Even if there is only  $V_S$  applied, signals on the internal inputs or outputs, even up to 18 V, must not result in any kind of faulty reaction of the H-bridge or in a destruction of the H-bridge.

**Table 6. Absolute Maximum Ratings**

| Symbol         | Parameter                                                                                                                    | Condition                                                                                                         | Min  | Typ | Max                             | Unit       |

|----------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------|-----|---------------------------------|------------|

| $V_{VS}$       | VS Static destruction proof                                                                                                  | $VDD = 0 \text{ V}$<br>$VDD = 5 \text{ V}$                                                                        | -1.0 | -   | 28                              | V          |

| $V_{VS}$       | VS Dynamic destruction proof; see load dump pulse                                                                            | $VDD = 0 \text{ V}$<br>$VDD = 5 \text{ V}$                                                                        | -1.0 | -   | 40                              | V          |

| $I_{VS,INV}$   | Dynamic destruction proof $t < 0.25 \text{ s}$                                                                               | $VDD = 0 \text{ V}$<br>$VDD = 5 \text{ V}$                                                                        | -    | -   | 5.0                             | A          |

| $V_{VDD}$      | VDD Static destruction proof                                                                                                 | $V_S = 0 \text{ V}$<br>$V_S = 18 \text{ V}$                                                                       | -0.5 | -   | 18                              | V          |

| $V_{CP}$       | Charge Pump Destruction proof                                                                                                | $VDD = 0 \text{ V}$<br>$VDD = 5 \text{ V}$                                                                        | -    | -   | $V_{VS} + \text{CP}$<br>voltage | V          |

| $V_{OUTx}$     | Vout static destruction proof                                                                                                | $V_S = 28 \text{ V}$<br>$VDD = 0 \text{ V}$<br>$VDD = 5 \text{ V}$<br>$I_x = 3 \text{ A}$                         | -1.0 | -   | $V_S + V_f$                     | V          |

| $V_{OUTx}$     | $V_{out}$ dynamic destruction proof, see load dump pulse)<br>load condition: 0.8 mH to 1 mH, PWM $f_{max} = 20 \text{ kHz}$  | $V_S = 40 \text{ V}$<br>$VDD = 0 \text{ V}$<br>$VDD = 5 \text{ V}$<br>$I_x = 10 \text{ A}$                        | -    | -   | $V_S + V_f$                     | V          |

| $I_{OUTx}$     | $I_{out}$ dynamic destruction proof $t < 0.5 \text{ s}$ (load<br>condition: 0.8 mH to 1 mH, PWM $f_{max} = 20 \text{ kHz}$ ) | $VOUTx \leq V_S + V_f$<br>$VDD = 0 \text{ V}$<br>$VDD = 5 \text{ V}$                                              | -    | -   | 10                              | A          |

| $V_x$          | Static destruction proof for internal pins                                                                                   | $V_S = 0 \text{ V}$<br>$V_S = 18 \text{ V}$<br>$VDD = 0 \text{ V}$<br>$VDD = 5 \text{ V}$<br>$VDD = 18 \text{ V}$ | -0.5 | -   | 18                              | V          |

| $V_{VS\_slew}$ | Maximum slew rate on $V_S$ (no destruction and no<br>change of parameters)                                                   | $VDD = 5 \text{ V}$<br>$IOUT = 3 \text{ A}$<br>$V_S = 6 \text{ V}, 10 \text{ V}, 14 \text{ V}, 18 \text{ V}$      | -    | -   | 60                              | V/ $\mu$ s |

*Note:*  $V_f$  is the voltage drop (by the defined current) over the body diode of the H-bridge driver.

## 2.4

### Quiescent current consumption

L9969 can guarantee quiescent current values below defined values. Table 7 reports all cases of interest, varying from disabled bridge, to bridge driven ON at different PWM frequencies, but without any output current to loads.  $5 \text{ V} < \text{VBATT} < 18 \text{ V}$ ,  $4.5 \text{ V} < \text{VDD} < 5.5 \text{ V}$ ,  $T_J = -40 \text{ }^\circ\text{C}$  to  $150 \text{ }^\circ\text{C}$ , unless otherwise specified.

**Table 7. Quiescent current consumption**

| Symbol   | Parameter                     | Condition                                                                                                          | Min | Typ | Max | Unit          |

|----------|-------------------------------|--------------------------------------------------------------------------------------------------------------------|-----|-----|-----|---------------|

| $I_{VS}$ | Quiescent current consumption | $5 \text{ V} < V_S < 18 \text{ V}$<br>Bridge disabled<br>$VDD = 5 \text{ V}$                                       | -   | -   | 15  | mA            |

| $I_{VS}$ | Stand-by current consumption  | $V_S = 14 \text{ V}$<br>Bridge disabled<br>$VDD = 0 \text{ V}$                                                     | 10  | -   | 100 | $\mu\text{A}$ |

| $I_{VS}$ | Quiescent current consumption | $5 \text{ V} < V_S < 18 \text{ V}$<br>$f_{OUT} = 2 \text{ kHz}$<br>$VDD = 5 \text{ V}$<br>$I_{OUT} = 0 \text{ A}$  | -   | -   | 18  | mA            |

| $I_{VS}$ | Quiescent current consumption | $5 \text{ V} < V_S < 18 \text{ V}$<br>$f_{OUT} = 10 \text{ kHz}$<br>$VDD = 5 \text{ V}$<br>$I_{OUT} = 0 \text{ A}$ | -   | -   | 21  | mA            |

| $I_{VS}$ | Quiescent current consumption | $V_S = 28 \text{ V}$<br>$f_{OUT} = 10 \text{ kHz}$<br>$VDD = 5 \text{ V}$<br>$I_{OUT} = 0 \text{ A}$               | -   | -   | 25  | mA            |

## 2.5

### ESD protection

**Table 8. ESD protection**

| Item                             | Parameter | Condition                                | Min         | Typ | Max       | Unit |

|----------------------------------|-----------|------------------------------------------|-------------|-----|-----------|------|

| All pins                         | -         | HBM                                      | -2          | -   | 2         | kV   |

| All pins                         | -         | CDM (values for corner pins in brackets) | -500/(-750) | -   | 500/(750) | V    |

| Pins to connector <sup>(1)</sup> | -         | HBM                                      | -4          | -   | 4         | kV   |

1. Pins are all GND connected together.

## 2.6 Power Supply

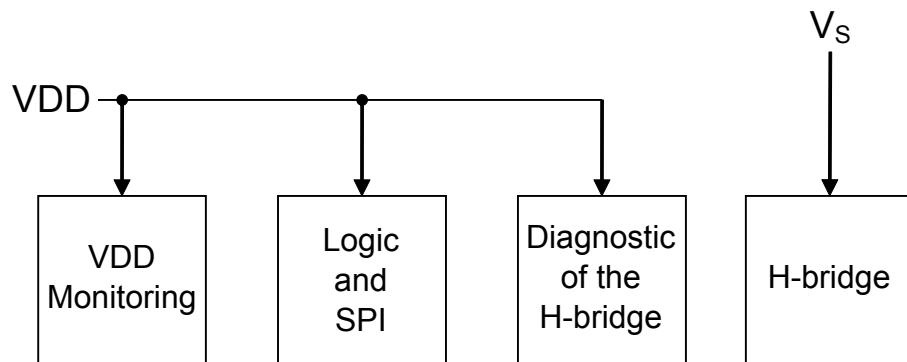

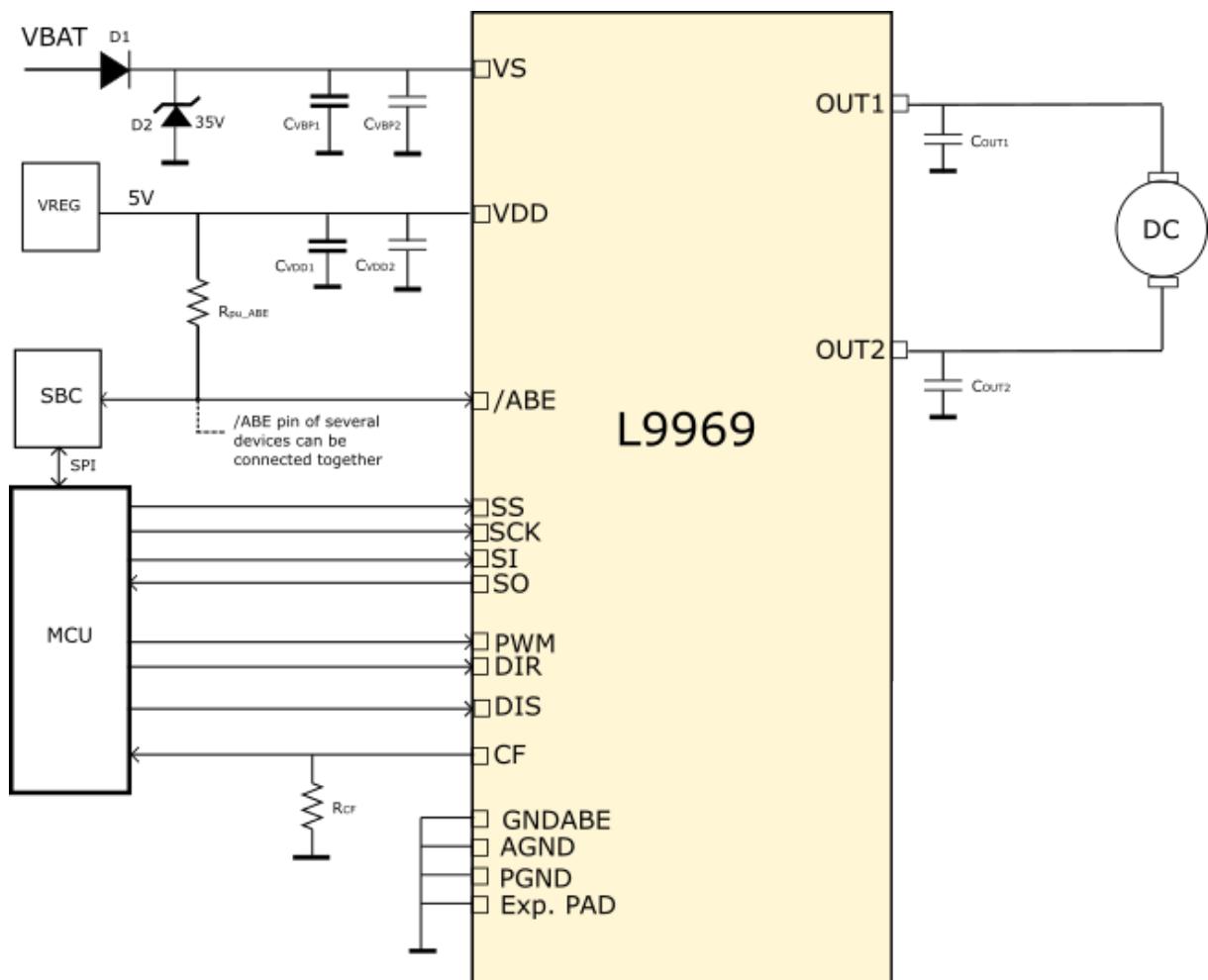

Figure 6 shows the connections between power supplies and L9969 internal blocks.

**Figure 6. Schematic of internal power supply**

**Table 9. VDD current absorption**

| Symbol                    | Parameter                                                                               | Condition                                                                                                                                                                         | Min | Typ | Max  | Unit |

|---------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| $I_{VDD\_SINGLE\_OFF}$    | Single bridge IC VDD supply current, bridge disabled                                    | $VDD = 4.5 \text{ V to } 5.5 \text{ V}$<br>$DIS = VDD$<br>$NABE = 0 \text{ V}$<br>$R_{CF} = 5.1 \text{ k}\Omega$<br>$CL4$                                                         | -   | -   | 11   | mA   |

| $I_{VDD\_SINGLE\_ON\_3A}$ | Single bridge IC VDD supply current, bridge enabled with 3 A load                       | $VDD = 4.5 \text{ V to } 5.5 \text{ V}$<br>$DIS = 0 \text{ V}$<br>$NABE = VDD$<br>$R_{CF} = 5.1 \text{ k}\Omega$<br>$PWM = DIR = 0 \text{ V}$<br>$I_{OUT} = 3 \text{ A}$<br>$CL4$ | -   | -   | 13.4 | mA   |

| $I_{VDD\_TWIN\_OFF}$      | Twin bridge IC VDD supply current ( $VDD1 + VDD2$ ), both bridges disabled              | $VDDx = 4.5 \text{ V to } 5.5 \text{ V}$<br>$DISx = VDD$<br>$NABEx = 0 \text{ V}$<br>$R_{CFx} = 5.1 \text{ k}\Omega$<br>$CL4$                                                     | -   | -   | 18.3 | mA   |

| $I_{VDD\_TWIN\_ON\_3A}$   | Twin bridge IC VDD supply current ( $VDD1 + VDD2$ ), both bridges enabled with 3 A load | $VDDx = 4.5 \text{ V to } 5.5 \text{ V}$<br>$DISx=0V$<br>$NABEx = VDD$<br>$R_{CFx} = 5.1 \text{ k}\Omega$<br>$PWMx = DIRx = 0 \text{ V}$<br>$I_{OUTx2} = 3 \text{ A}$<br>$CL4$    | -   | -   | 23.1 | mA   |

## 2.6.1 Power-ON reset

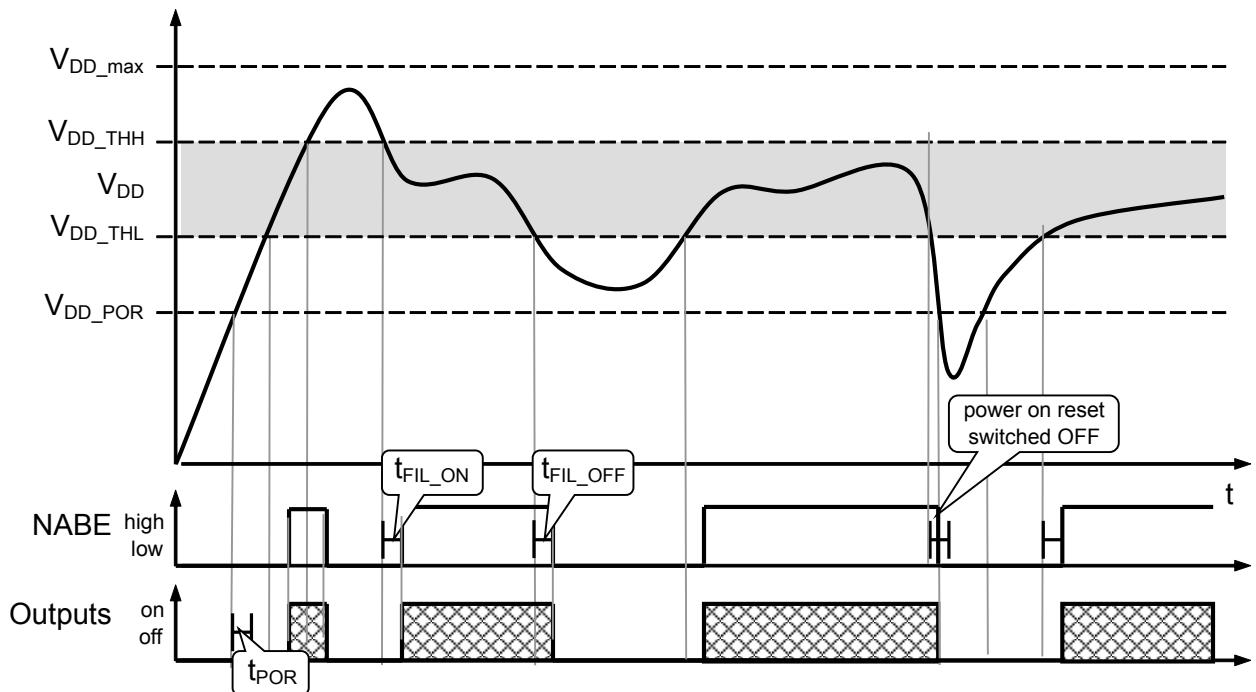

VDD is internally monitored, to keep the output stages in tristate in case VDD is incorrect.

Two internal monitoring/resetting sources are implemented:

- The internal reset function in the H-bridge if VDD is decreasing down to  $V_{DD\_RES}$ . That function resets the SPI registers, switches the output stages to tristate and switches NABE to low.

- The internal VDD monitoring, that is working, if the  $VDD > V_{DD\_POR}$  for longer than  $t_{POR}$ . In this case, the SPI is working; the VDD monitoring is active and sets the SPI registers, switches the output stages to tristate and switches NABE to low, if VDD is incorrect. In any cases, after a Power-ON Reset, the H-bridge is completely functional again, but the outputs are disabled. They can only be enabled by ENDISR.

$5 \text{ V} < VBATT < 18 \text{ V}$ ,  $T_J = -40 \text{ }^\circ\text{C}$  to  $150 \text{ }^\circ\text{C}$ , unless otherwise specified.

**Table 10. VDD monitoring thresholds**

| Symbol        | Parameter                                                                                                                                                                                                                                                                     | Condition | Min | Typ | Max  | Unit |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----|-----|------|------|

| $V_{DD\_RES}$ | VDD Undervoltage Threshold (VDD: 'H' → 'L') Below this threshold the device is in reset state, all registers are cleared.                                                                                                                                                     | -         | 3.3 | 3.6 | 3.9  | V    |

| $V_{DD\_POR}$ | Power On Reset Threshold (VDD: 'L' → 'H') Below this threshold the device is in reset state, all registers are cleared. The device starts operation (VDD monitoring forces stages off) not later than $t_{POR}$ , when VDD is rising above this threshold. SPI is functional. | -         | 3.5 | 3.8 | 4.1  | V    |

| $t_{POR}$     | Power On Reset Extension Time                                                                                                                                                                                                                                                 | -         | -   | -   | 1000 | μs   |

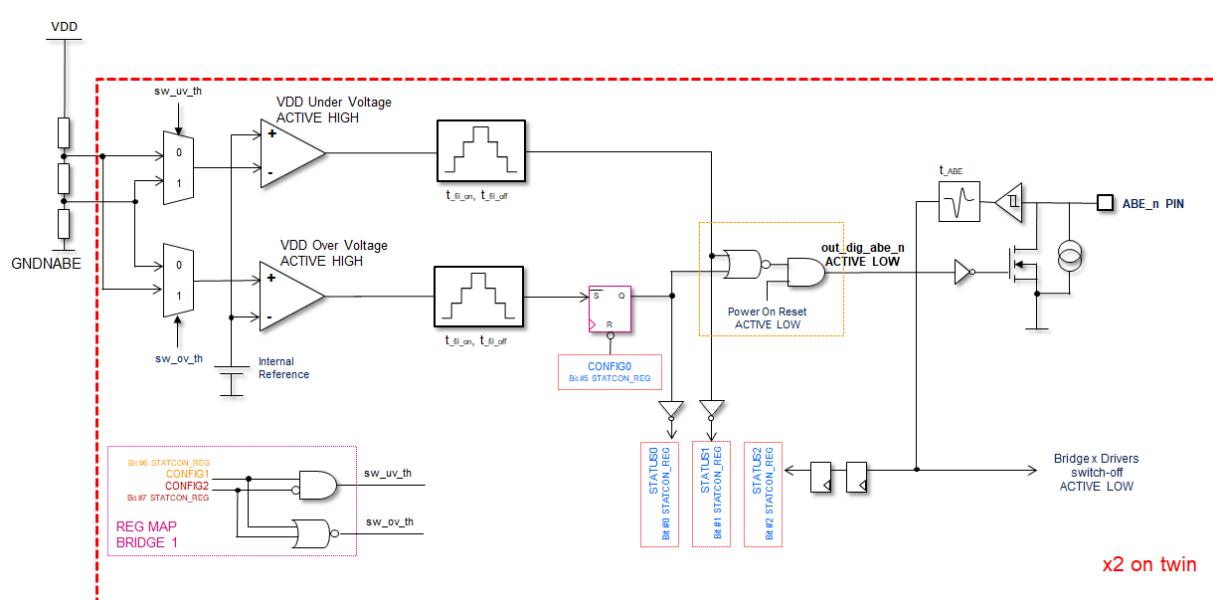

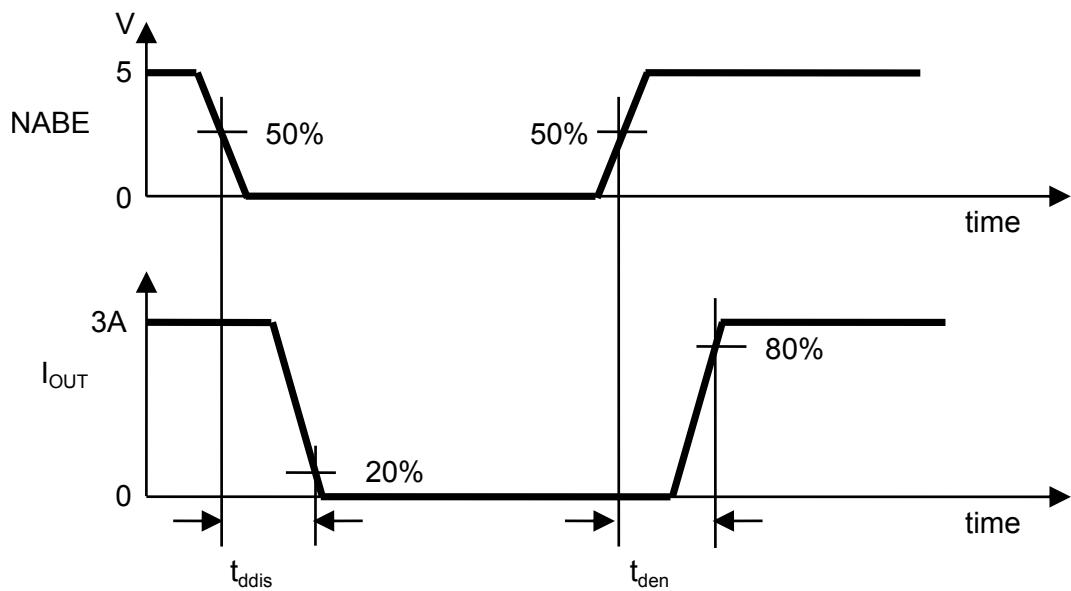

## 2.6.2 NABE and VDD monitoring

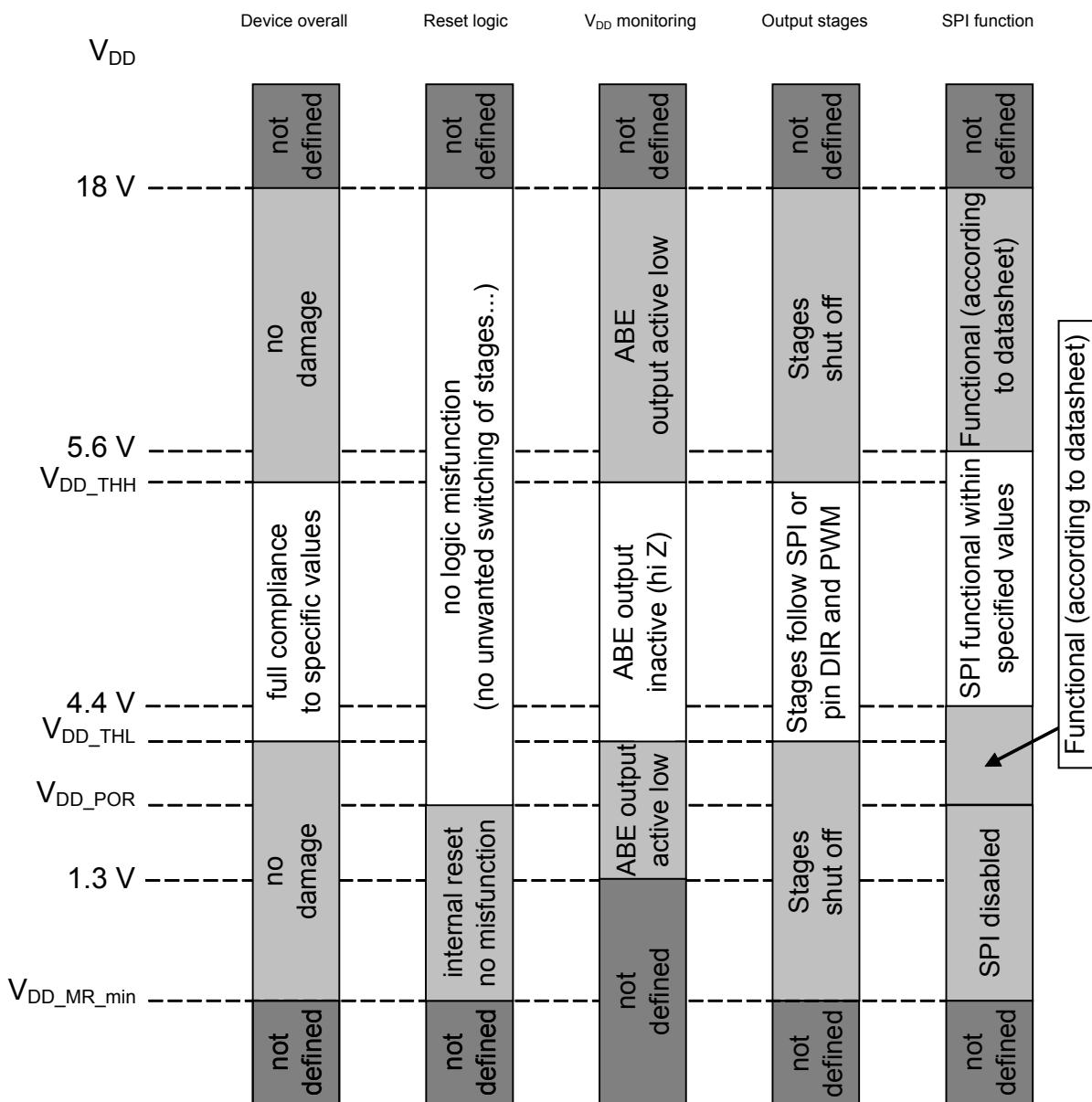

### 2.6.2.1 General functions of VDD monitoring

$V_{DD}$  is measured with reference to pin  $GND_{ABE}$ . Inside the H-bridge,  $GND_{ABE}$  is routed separately to avoid internal cross talking from power lines.

The state of  $V_{DD}$  monitoring is stored in  $STATCON\_REG$  and is read/write via SPI.

$V_{DD}$  monitoring detects faulty supply voltages at  $V_{DD}$ . It disables the output stages but does not reset registers  $DIA\_REG1$ ,  $DIA\_REG2$ ,  $CONFIG\_REG$  or  $STATCON\_REG$ .

In case of  $V_{DD}$  failure, the output stages are switched off, even if the voltage at pin NABE is a high level, for example because of an external short circuit to  $V_{DD}$  or to the battery voltage (up to 18 V).

OUT1 and OUT2 cannot be switched on in over or undervoltage condition at  $V_{DD}$ .

$POR (V_{DD} < V_{DD\_RES})$  switches off all output stages without delay.

Detailed information (differentiation of over and undervoltage detection) is possible by SPI interface.

**Figure 7. VDD Monitoring and dependencies**

#### 2.6.2.2 VDD undervoltage

If the voltage between pins  $V_{DD}$  and  $GND_{ABE}$  is below the lower  $V_{DD}$ -monitoring threshold ( $V_{DD\_THL}$ ), the output stages are switched off after a filtering time ( $t_{FIL\_OFF}$ ) and an active low signal is generated at the bi-directional pin NABE. After a transition from an undervoltage to a regular voltage between pins  $V_{DD}$  and  $GND_{ABE}$ , the signal at pin NABE is (automatically) set high again once the filtering time ( $t_{FIL\_ON}$ ) has expired. Writing new information to configuration registers is possible.

If VDD falls below the power-on-reset supply voltage ( $V_{DD\_RES}$ ) all stages are switched off and NABE is switched active low. When VDD is rising above the power-on-reset supply voltage threshold ( $V_{DD\_POR}$ ), the ASIC will remain in POR until a time  $t_{POR}$  is run out, then all registers will be reset to their respective default state (all registers cleared to default).

#### 2.6.2.3 VDD overvoltage

If the voltage between pins  $V_{DD}$  and  $GND_{ABE}$  is above the upper  $V_{DD}$ -monitoring threshold ( $V_{DD\_THH}$ ), all output stages are switched off after a filtering time ( $t_{FIL\_OFF}$ ) and an active low signal is generated at the bi-directional pin NABE.

After a transition from an overvoltage to a regular voltage between pins  $V_{DD}$  and  $GND_{ABE}$ , the behavior of the NABE level and the output stages depend on the configuration of the bit CONFIG0 of STATCON\_REG:

- 1: NABE is latched and the outputs remain off. A return to normal operation is only possible with power-on reset or by changing the bit STATCON\_REG.CONFIG0 via SPI → 0.

- 0: NABE is inactive after VDD returned to its regular operating voltage and the filtering time has expired. The power stages are enabled again automatically. Writing new information to configuration registers is possible.

**Figure 8. Overview of VDD voltage ranges**

#### 2.6.2.4

##### **Behavior on pin NABE in case of external short circuit**

In case a short circuit on the PCB pulls both pins NABE and V<sub>DD</sub> for example, to the battery voltage (max. 18 V), the internal power-stage at pin NABE is designed in such a way that the H-bridge is not damaged, in case NABE is pulled-down internally to GND, even though an external battery voltage is applied low-ohmic to pin NABE. The internal power-stage sustains such short-circuit for a few hours.

#### 2.6.2.5

##### **NABE Pin**

NABE is a bidirectional pin (input and output). As an input function, all output power-stages are permanently switched off if an external low signal is applied to pin NABE. NABE output is realized as an open drain low side switch. During a V<sub>DD</sub> over-voltage (above V<sub>DD</sub>\_THH) or undervoltage (below V<sub>DD</sub>\_THL), the pin is pulled to GND (logic low). Refer also to [Section 2.6.2.4 Behavior on pin NABE in case of external short circuit](#) in case of an external short circuit at pin NABE.

The NABE-Pin is made redundant to the DIS-Pin to reach the ISO26262 Safety Goals. The NABE goes directly to the Gate-Driver of the Bridge.

The default signal level of “NABE” (for example in case of ECU initialization) is low-level with integrated pull down-current source.

A low logic level at “NABE” and/or a high logic level at “DIS” switch off all output stages. In this case the access to the SPI is possible and the bit NABE\_DIS in the DIA\_REG1 is set to low.

Two separate pins are provided for NABE and DIS. For safety reasons, these signals are routed separately and ideally with a certain distance from each other on the silicon.

### 2.6.2.6

#### Testing of VDD monitoring

VDD Monitoring cannot be switched off. The output stages are switched off by VDD monitoring if under or overvoltage on VDD is detected. Testing of VDD monitoring is possible via SPI.

#### Testing of upper thresholds:

By writing STATCON\_REG, bit CONFIG2 = 0, the VDD test mode is activated.

If STATCON\_REG, bit CONFIG1 = 0, the upper VDD test threshold is lowered (overvoltage threshold is reduced to  $V_{TEST\_THH}$ ).

As a result, STATCON\_REG, bit STATUS0 = 0 and DIA\_REG1, bit NABE\_DIS = 0.

Overvoltage is reported and pin NABE is pulled low.

Once the test routine is ended (CONFIG2 = 1) or the upper VDD test threshold is reset to its standard value, STATUS0=1 (no overvoltage anymore) and NABE\_DIS =1. Pin NABE is pulled high.

The same test routine can be performed with STATCON\_REG, bit CONFIG0 = 1 (latching of overvoltage condition). In that case, ending the test routine will not automatically reset bit NABE\_DIS and pin NABE.

#### Testing of lower thresholds:

By writing STATCON\_REG, bit CONFIG2 = 0, the VDD test mode is activated.

If STATCON\_REG, bit CONFIG1 = 1, the lower VDD test threshold is lifted (undervoltage threshold is increased to  $V_{TEST\_THL}$ ).

As a result, STATCON\_REG, bit STATUS1 = 0 and DIA\_REG1, bit NABE\_DIS = 0.

Undervoltage is reported and pin NABE is pulled low.

Once the test routine is ended (CONFIG2 = 1) or the lower VDD test threshold is reset to its standard value, STATUS1=1 (no undervoltage anymore) and NABE\_DIS =1. Pin NABE is pulled high.

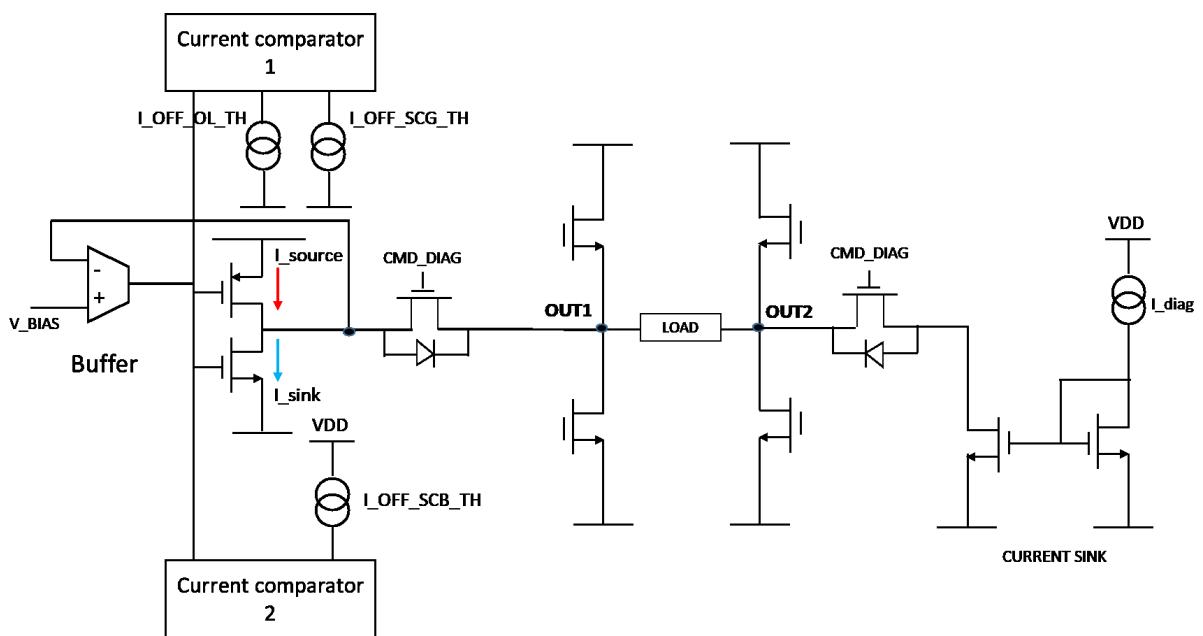

**Figure 9. Circuit diagram of VDD monitoring**

**Table 11. VDD Monitoring parameters**

| Symbol               | Parameter                                                                                          | Condition                                                                                     | Min           | Typ | Max  | Unit          |

|----------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------|-----|------|---------------|

| $V_{DD}$             | VDD voltage range at which monitoring circuit shows defined behavior on pin NABE                   | -                                                                                             | $V_{DD\_POR}$ | -   | 18   | V             |

| $V_{DD\_THL}$        | VDD Undervoltage threshold                                                                         | -                                                                                             | 4.2           | -   | 4.4  | V             |

| $V_{DD\_THH}$        | VDD Overvoltage threshold                                                                          | -                                                                                             | 5.25          | -   | 5.5  | V             |

| $t_{FIL\_OFF}$       | Filtering time before switching off, when VDD voltage goes out of thresholds                       | -                                                                                             | 60            | -   | 135  | $\mu$ s       |

| $t_{FIL\_ON}$        | Filtering time before switching on, when VDD comes back inside thresholds                          | -                                                                                             | 60            | -   | 135  | $\mu$ s       |

| $V_{TEST\_THL}$      | VDD Undervoltage threshold during VDD Monitoring test                                              | -                                                                                             | 5.25          | -   | 5.5  | V             |

| $V_{TEST\_THH}$      | VDD Overvoltage threshold during VDD Monitoring test                                               | -                                                                                             | 4.2           | -   | 4.4  | V             |

| $V_{DD\_slew}$       | Maximum slew rate on VDD without any change of parameters of VDD monitoring                        | -                                                                                             | 500           | -   | -    | $mV/\mu$ s    |

| $\Delta V_{DD\_THx}$ | Change of VDD_THH or VDD_THL, in case of inverse current on $V_S$                                  | -                                                                                             | -0.1          | -   | 0.1  | V             |

| $V_{ABE\_INL}$       | NABE input low level                                                                               | -                                                                                             | -0.3          | -   | 1.65 | V             |

| $V_{ABE\_INH}$       | NABE input high level                                                                              | -                                                                                             | 3.15          | -   | 18   | V             |

| $V_{ABE\_INHYS}$     | NABE input hysteresis                                                                              | -                                                                                             | 0.15          | -   | 1.0  | V             |

| $I_{ABE\_IN}$        | NABE input current                                                                                 | $V_{ABE} = 18\text{ V}$                                                                       | 20            | -   | 70   | $\mu\text{A}$ |

| $I_{ABE\_IN}$        | NABE input current                                                                                 | $V_{ABE} = 5\text{ V}$                                                                        | 20            | 40  | 60   | $\mu\text{A}$ |

| $I_{ABE\_IN}$        | NABE input current                                                                                 | $0\text{ V} < V_{ABE} < 1.5\text{ V}$                                                         | 0             | -   | 60   | $\mu\text{A}$ |

| $V_{ABE\_OUTL}$      | NABE output voltage when VDD below THL                                                             | $0\text{ V} < V_{DD} < V_{DD\_THL}$<br>$I_{ABE\_OUTL} < 2.5\text{ mA}$                        | 0.0           | -   | 1.0  | V             |

| $V_{ABE\_OUTL}$      | NABE output voltage when VDD above THH                                                             | $V_{DD\_THH} < V_{DD} < 18\text{ V}$<br>$I_{ABE\_OUTL} < 7.5\text{ mA}$                       | 0.0           | -   | 1.2  | V             |

| $V_{ABE\_OUTL}$      | Passive output low voltage                                                                         | Pull down current source to GND, no load Measure voltage at NABE (if NABE is high impedance). | 0.0           | -   | 1.0  | V             |

| $t_{ABE}$            | NABE pulse width (minimum width required for setting/resetting SPI bits or diagnostic information) | -                                                                                             | 0.5           | 1   | 1.5  | $\mu$ s       |

| $\Delta I_{ABE}$     | Change of input current of NABE output pin in case of inverse current on $V_S$                     | -                                                                                             | -100          | -   | 100  | $\mu\text{A}$ |

## 3 Functional description

### 3.1 Description of external interfaces

- Voltage supply  $V_S$  can be connected directly to the battery voltage via a relay (for example the main relay in an engine control system). Otherwise an additional external inverse voltage protection is necessary.

- The load at the outputs is connected between both outputs (OUT1 and OUT2) in H-bridge mode.

- The ASIC has two inputs controlling the current through the H-bridge: DIR controls the direction of the current (DIR = 0 → Current flows from OUT1 → OUT2; DIR = 1 → Current flows from OUT2 → OUT1) and PWM controls the magnitude of the current (duty cycle 0% → no current ... duty cycle 100% → maximum current).

### 3.2 Functional behavior in detail

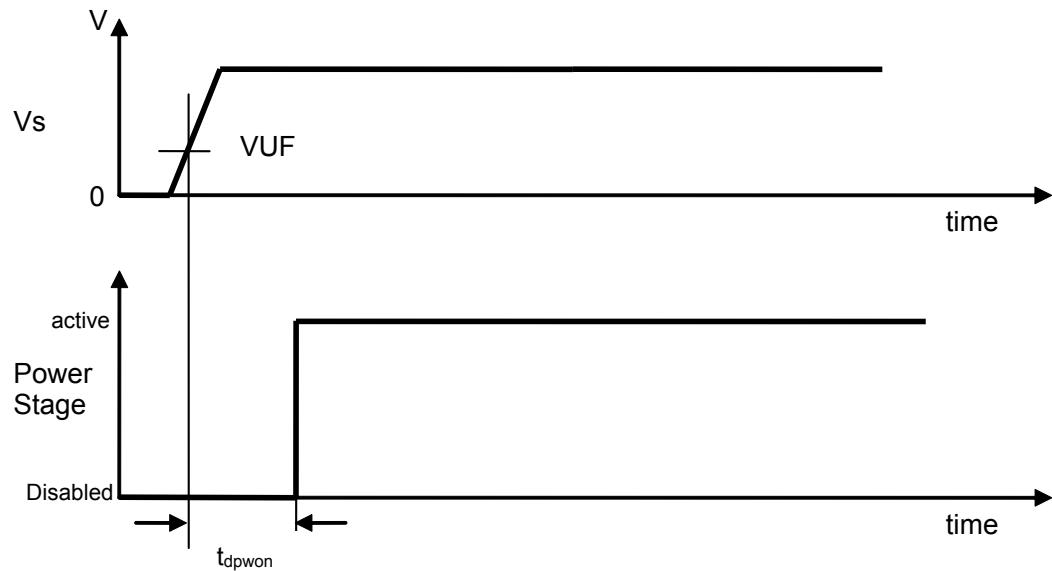

All parameters are defined at (unless otherwise specified):

- $4.5 \text{ V} < V_{DD} < 5.5 \text{ V}$

- $V_{UF} < V_S < 28 \text{ V}$  (power stages active)

- $0 \text{ V} < V_S < V_{UF}$  (power stages inactive)

- $-40 \text{ }^\circ\text{C} < T_J < 150 \text{ }^\circ\text{C}$

- The HBR can withstand a  $V_S$  of 40 V for load dump pulse (see Section 6 Load dump pulse)

- It is recommended to perform the necessary adjustments at high temperature

- All voltages refer to AGND

#### 3.2.1 Power stages

L9969 provides a full H-bridge power stage, consisting of two half bridges, which are intended to be used mainly for the control of DC motors.

The most critical loads are throttle-control actuators with the following electrical characteristics: inductance 0.8 mH to 1.0 mH, resistance 1.2  $\Omega$  to 1.8  $\Omega$  at room temperature, PWM-frequency  $f_{min} = 1 \text{ Hz}$  and  $f_{max} = 20 \text{ kHz}$ .

$5 \text{ V} < V_{BATT} < 18 \text{ V}$ ,  $4.5 \text{ V} < V_{DD} < 5.5 \text{ V}$ ,  $T_J = -40 \text{ }^\circ\text{C}$  to  $150 \text{ }^\circ\text{C}$ , unless otherwise specified.

Table 12. Power stages parameters

| Symbol        | Parameter                                                                                                | Condition                                                    | Min  | Typ | Max | Unit             |

|---------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------|-----|-----|------------------|

| $R_{OUT-GND}$ | Rds_ON resistance low side                                                                               | $I_{OUT} = 3 \text{ A}$                                      | -    | -   | 225 | $\text{m}\Omega$ |

|               |                                                                                                          | $10 \text{ V} < V_S < 28 \text{ V}$                          |      |     |     |                  |

|               |                                                                                                          | Max. values at $T_J = 150 \text{ }^\circ\text{C}$            |      |     |     |                  |

| $R_{OUT-UB}$  | Rds_ON resistance high side                                                                              | $I_{OUT} = 3 \text{ A}$                                      | -    | -   | 315 | $\text{m}\Omega$ |

| $I_{leak}$    | OFF State leakage current H-bridge disabled by short circuit detection; this is the current of one stage | $10 \text{ V} < V_S < 28 \text{ V}$                          |      |     |     |                  |

|               |                                                                                                          | Max. values at $T_J = 150 \text{ }^\circ\text{C}$            |      |     |     |                  |

| $I_{leak}$    | OFF State leakage current VDD below $V_{DD\_RES}$                                                        | $V_S = 13 \text{ V}$<br>$OUTx = 0 \text{ V} \text{ or } V_S$ | -200 | -   | 200 | $\mu\text{A}$    |

|               |                                                                                                          | $V_S = 13 \text{ V}$<br>$OUTx = 0 \text{ V} \text{ or } V_S$ | -200 | -   | 800 | $\mu\text{A}$    |

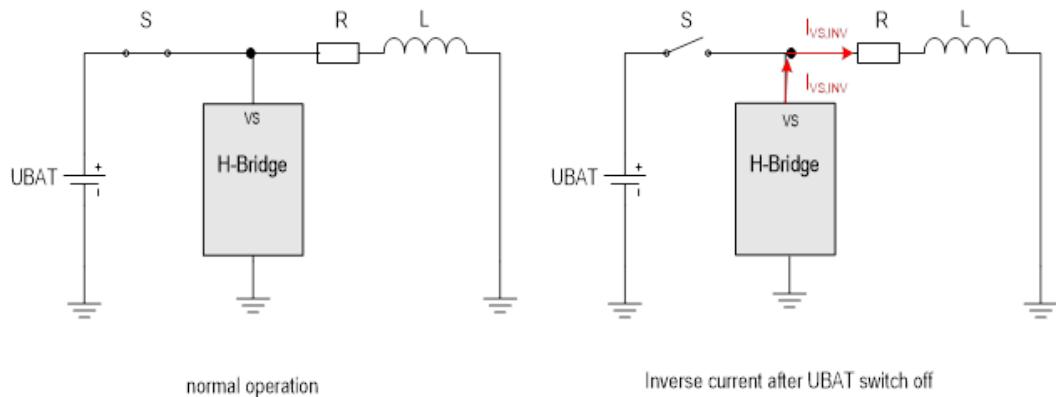

#### 3.2.2 Inverse current on $V_S$

Inverse currents flow out of  $V_S$ . An inverse current with maximum 5 A decreasing during a maximum period of 250 ms does not lead to any destruction of the H-bridge ASIC. After exposure to such an inverse current, the full functionality of the device is guaranteed (according to the product target specification).

Information is needed about the behavior of the inputs and outputs during inverse current. Furthermore, information is needed on the reliability of information stored in internal registers during inverse current.

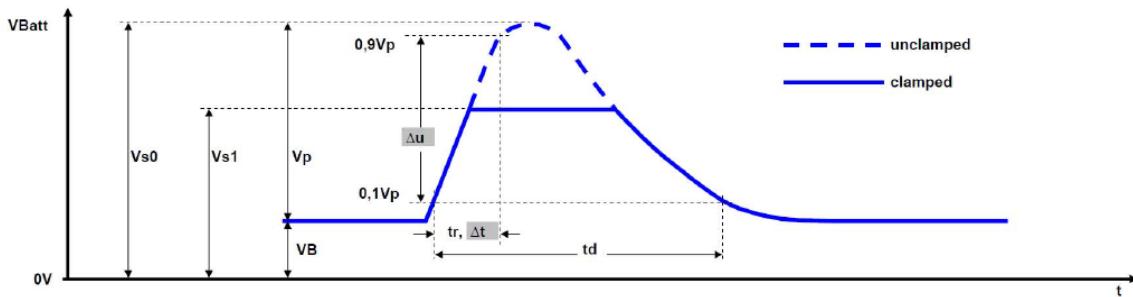

**Figure 10. Inverse current**

5 V < VBATT < 18 V, 4.5 V < VDD < 5.5 V,  $T_J = -40$  °C to 150 °C, unless otherwise specified.

**Table 13. Inverse Current**

| Symbol              | Parameter                                | Condition | Min | Typ | Max | Unit |

|---------------------|------------------------------------------|-----------|-----|-----|-----|------|

| $I_{VS,INV}$        | Inverse Current                          | 250 ms    | -   | -   | 5   | A    |

| $V_{VS\_slew\_inv}$ | Maximum slew rate during inverse current | -         | -5  | -   | -   | V/μs |

### 3.2.3 Reverse current

Reverse current is different from inverse Current. It is the current flowing in the load during the passive free-wheeling phase, and passing through the low-side body diode, as soon as the high-side of the same branch is switched OFF.

To reduce internal power losses, the free-wheeling is designed in such a way that, after some period of time, the free-wheel diode is actively short-cut by the transistor channel (beginning the so-called active free-wheeling).

5 V < VBATT < 18 V, 4.5 V < VDD < 5.5 V,  $T_J = -40$  °C to 150 °C, unless otherwise specified.

**Table 14. Reverse current**

| Symbol   | Parameter                              | Condition       | Min | Typ | Max | Unit |

|----------|----------------------------------------|-----------------|-----|-----|-----|------|

| $U_D$    | Free-wheel diode forward voltage       | $I_{OUT} = 3$ A | -   | -   | 2   | V    |

| $t_{fr}$ | Free-wheel diode reverse recovery time | -               | -   | -   | 100 | ns   |

If the H-bridge is in internal current limitation or in thermal current reduction mode, the above-mentioned short-circuiting of the free-wheeling diode is enabled or disabled according to the status of the free-wheeling bit in the SPI register: CONFIG\_REG.FW = 1 (short-cut enabled - active free wheeling) or CONFIG\_REG.FW = 0 (short-cut disabled – passive free wheeling).

### 3.2.4 Power stage switching behavior

Here below (see the Table 15) the possible combinations parallel inputs/driver outputs.

**Table 15. Parallel inputs combinations and output states**

| PWM | DIR | OUT1 | OUT2 | Remark                               |

|-----|-----|------|------|--------------------------------------|

| L   | L   | L    | L    | No active current flow into the load |

| L   | H   | L    | L    | No active current flow into the load |

| H   | L   | H    | L    | A current flows from HS1 toward LS2  |

| H   | H   | L    | H    | A current flows from HS2 toward LS1  |

Note: HS<sub>x</sub> stands for high-side transistor of half-bridge x; LS<sub>x</sub> stands for low-side transistor of half-bridge x.

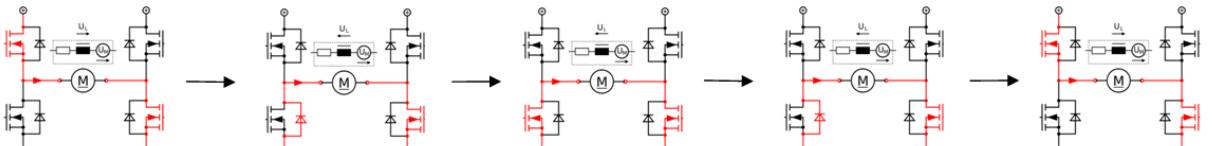

#### 3.2.4.1 Switching sequence during regular operation

The switching sequence during a regular pulsed width modulation operation is shown in the figure below and is made of 5 steps:

1. The connected load is powered, for example, via HSS1 and LSS1.

2. This is the transition between the powering and the active free-wheeling phase. During this short time where HSS1 is getting non-conductive and LSS1 has not started conducting yet, a passive free-wheeling via the bulk diode of LSS1 takes place.

3. This is the active free-wheeling. In this step LSS1 gets conductive.

4. This is the transition between the active free-wheeling and the powering phase. Similarly to the 2<sup>nd</sup> step, LSS1 is getting non-conductive and HSS1 has not started conducting yet. A passive free-wheeling via the bulk diode of LSS1 takes place.

5. See 1<sup>st</sup> step.

**Figure 11. Switching sequence during normal operation**

During a regular operation, there is always one half-bridge responsible for the pulsation (in the above example the half-bridge made of HSS1 and LSS1) and one static half-bridge (in the above example the half-bridge made of HSS2 and LSS2). As showed in the above example, the LSS of the static half-bridge remains conducting over the complete period whereas the HSS of the static half-bridge is unused.

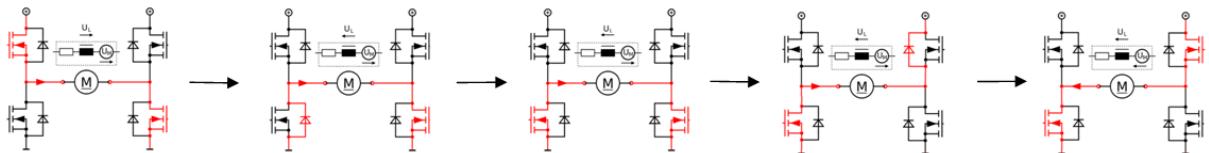

#### 3.2.4.2 Switching sequence during change of direction

The switching sequence during a change of direction is shown in the figure below and is made of 5 steps:

1. The connected load is powered, for example, via HSS1 and LSS2.

2. This is the transition between the powering and the active free-wheeling phase. During this short time where HSS1 is getting non-conductive and LSS2 has not started conducting yet, a passive free-wheeling via the bulk diode of LSS2 takes place.

3. This is the active free-wheeling. In this step LSS2 gets conductive.

4. In this step, the change of direction is starting. Now, LSS2 is getting non-conductive but HSS2 has not started conducting yet. The induced current resulting from the back electromotive force (back-EMF) is still flowing from the left to the right. The current is flowing via the bulk diode of HSS2, the external capacitor and back via LSS1.

5. In this step, HSS2 is getting conductive. The connected load is finally powered in the opposite direction via HSS2 and LSS1.

Figure 12. Switching sequence during change of direction

## 3.2.4.3

## Power stage switching parameters

Parameters valid at  $V_S$  in the range of (8 V...18 V),  $I_{OUT} = 3$  A.

$T = -40$  °C to 150 °C, unless otherwise specified;  $C_{OUTxy} = 10$  nF connected during all the tests below.

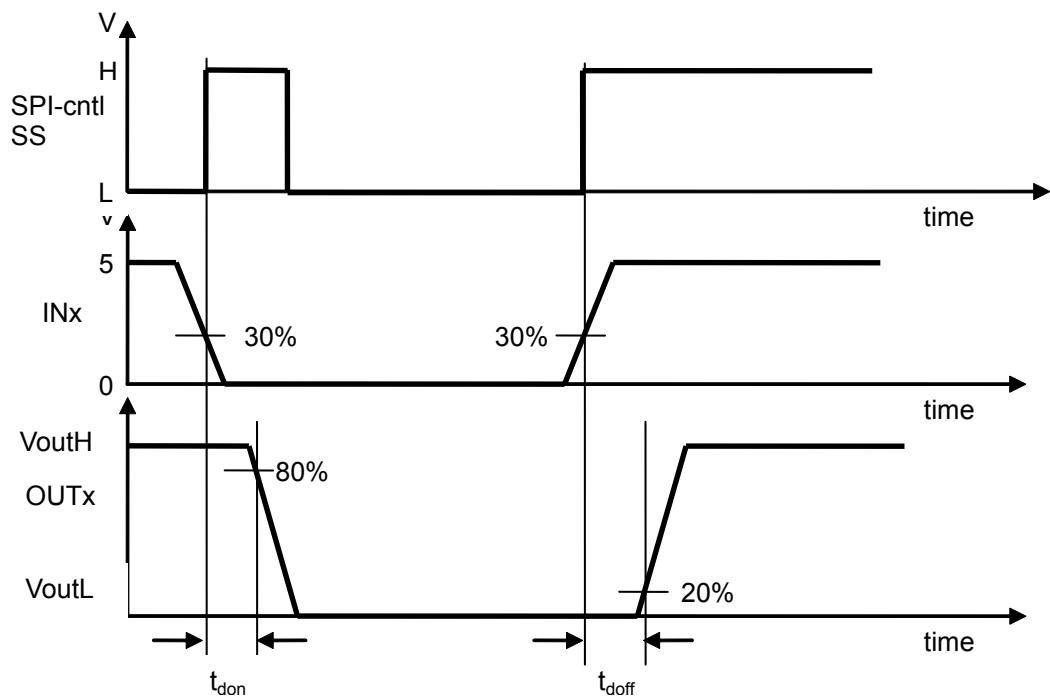

Table 16. Power stage switching parameters

| Symbol             | Parameter                                                         | Condition | Min | Typ | Max | Unit |

|--------------------|-------------------------------------------------------------------|-----------|-----|-----|-----|------|

| $t_{don00\_dcm0}$  | Output HS ON delay<br>PWM or DIR 50% → OUT 20%<br>DCmatching = 0  | SR = 00   | -   | -   | 15  | μs   |

| $t_{don01\_dcm0}$  | Output HS ON delay<br>PWM or DIR 50% → OUT 20%<br>DCmatching = 0  | SR = 01   | -   | -   | 10  | μs   |

| $t_{don10\_dcm0}$  | Output HS ON delay<br>PWM or DIR 50% → OUT 20%<br>DCmatching = 0  | SR = 10   | -   | -   | 6   | μs   |

| $t_{don11\_dcm0}$  | Output HS ON delay<br>PWM or DIR 50% → OUT 20%<br>DCmatching = 0  | SR = 11   | -   | -   | 6   | μs   |

| $t_{don00\_dcm1}$  | Output HS ON delay<br>PWM or DIR 50% → OUT 20%<br>DCmatching = 1  | SR = 00   | -   | -   | 8   | μs   |

| $t_{don01\_dcm1}$  | Output HS ON delay<br>PWM or DIR 50% → OUT 20%<br>DCmatching = 1  | SR = 01   | -   | -   | 6   | μs   |

| $t_{don10\_dcm1}$  | Output HS ON delay<br>PWM or DIR 50% → OUT 20%<br>DCmatching = 1  | SR = 10   | -   | -   | 6   | μs   |

| $t_{don11\_dcm1}$  | Output HS ON delay<br>PWM or DIR 50% → OUT 20%<br>DCmatching = 1  | SR = 11   | -   | -   | 6   | μs   |

| $t_{doff00\_dcm0}$ | Output HS OFF delay<br>PWM or DIR 50% → OUT 80%<br>DCmatching = 0 | SR = 00   | -   | -   | 25  | μs   |

| $t_{doff01\_dcm0}$ | Output HS OFF delay<br>PWM or DIR 50% → OUT 80%<br>DCmatching = 0 | SR = 01   | -   | -   | 20  | μs   |

| $t_{doff10\_dcm0}$ | Output HS OFF delay<br>PWM or DIR 50% → OUT 80%                   | SR = 10   | -   | -   | 6   | μs   |

| Symbol               | Parameter                                                                  | Condition | Min  | Typ | Max  | Unit |

|----------------------|----------------------------------------------------------------------------|-----------|------|-----|------|------|

|                      | DCmatching = 0                                                             |           |      |     |      |      |

| $t_{doff11\_dcm0}$   | Output HS OFF delay<br>PWM or DIR 50% → OUT 80%<br>DCmatching = 0          | SR = 11   | -    | -   | 6    | μs   |

| $t_{doff00\_dcm1}$   | Output HS OFF delay<br>PWM or DIR 50% → OUT 80%<br>DCmatching = 1          | SR = 00   | -    | -   | 10.5 | μs   |

| $t_{doff01\_dcm1}$   | Output HS OFF delay<br>PWM or DIR 50% → OUT 80%<br>DCmatching = 1          | SR = 01   | -    | -   | 7    | μs   |

| $t_{doff10\_dcm1}$   | Output HS OFF delay<br>PWM or DIR 50% → OUT 80%<br>DCmatching = 1          | SR = 10   | -    | -   | 6    | μs   |

| $t_{doff11\_dcm1}$   | Output HS OFF delay<br>PWM or DIR 50% → OUT 80%<br>DCmatching = 1          | SR = 11   | -    | -   | 6    | μs   |

| $t_{ddelta00\_dcm0}$ | Delta HS ON/OFF delay<br>DCmatching = 0                                    | SR = 00   | -5   | -   | 18   | μs   |

| $t_{ddelta01\_dcm0}$ | Delta HS ON/OFF delay<br>DCmatching = 0                                    | SR = 01   | -1.5 | -   | 10   | μs   |

| $t_{ddelta10\_dcm0}$ | Delta HS ON/OFF delay<br>DCmatching = 0                                    | SR = 10   | -1.5 | -   | 1.5  | μs   |

| $t_{ddelta11\_dcm0}$ | Delta HS ON/OFF delay<br>DCmatching = 0                                    | SR = 11   | -1.5 | -   | 1.5  | μs   |

| $t_{ddelta00\_dcm1}$ | Delta HS ON/OFF delay<br>DCmatching = 1                                    | SR = 00   | -4   | -   | 4    | μs   |

| $t_{ddelta01\_dcm1}$ | Delta HS ON/OFF delay<br>DCmatching = 1                                    | SR = 01   | -2   | -   | 2    | μs   |

| $t_{ddelta10\_dcm1}$ | Delta HS ON/OFF delay<br>DCmatching = 1                                    | SR = 10   | -1.5 | -   | 1.5  | μs   |

| $t_{ddelta11\_dcm1}$ | Delta HS ON/OFF delay<br>DCmatching = 1                                    | SR = 11   | -1   | -   | 1    | μs   |

| $t_{don00\_spi}$     | Output HS ON delay<br>(SPI control)<br>SS 50% → OUTx 20%<br>DCmatching = 0 | SR = 00   | -    | -   | 15   | μs   |

| $t_{don01\_spi}$     | Output HS ON delay<br>(SPI control)<br>SS 50% → OUTx 20%<br>DCmatching = 0 | SR = 01   | -    | -   | 10   | μs   |

| $t_{don10\_spi}$     | Output HS ON delay<br>(SPI control)<br>SS 50% → OUTx 20%<br>DCmatching = 0 | SR = 10   | -    | -   | 6    | μs   |

| Symbol                  | Parameter                                                                   | Condition | Min | Typ | Max  | Unit |

|-------------------------|-----------------------------------------------------------------------------|-----------|-----|-----|------|------|

| $t_{don11\_spi}$        | Output HS ON delay<br>(SPI control)<br>SS 50% → OUTx 20%<br>DCmatching = 0  | SR = 11   | -   | -   | 6    | μs   |

| $t_{don00\_spi\_dcm1}$  | Output HS ON delay<br>(SPI control)<br>SS 50% → OUTx 20%<br>DCmatching = 1  | SR = 00   | -   | -   | 8    | μs   |

| $t_{don01\_spi\_dcm1}$  | Output HS ON delay<br>(SPI control)<br>SS 50% → OUTx 20%<br>DCmatching = 1  | SR = 01   | -   | -   | 6    | μs   |

| $t_{don10\_spi\_dcm1}$  | Output HS ON delay<br>(SPI control)<br>SS 50% → OUTx 20%<br>DCmatching = 1  | SR = 10   | -   | -   | 6    | μs   |

| $t_{don11\_spi\_dcm1}$  | Output HS ON delay<br>(SPI control)<br>SS 50% → OUTx 20%<br>DCmatching = 1  | SR = 11   | -   | -   | 6    | μs   |

| $t_{doff00\_spi\_dcm0}$ | Output HS OFF delay<br>(SPI control)<br>SS 50% → OUTx 80%<br>DCmatching = 0 | SR = 00   | -   | -   | 25   | μs   |

| $t_{doff01\_spi\_dcm0}$ | Output HS OFF delay<br>(SPI control)<br>SS 50% → OUTx 80%<br>DCmatching = 0 | SR = 01   | -   | -   | 20   | μs   |

| $t_{doff10\_spi\_dcm0}$ | Output HS OFF delay<br>(SPI control)<br>SS 50% → OUTx 80%<br>DCmatching = 0 | SR = 10   | -   | -   | 6    | μs   |

| $t_{doff11\_spi\_dcm0}$ | Output HS OFF delay<br>(SPI control)<br>SS 50% → OUTx 80%<br>DCmatching = 0 | SR = 11   | -   | -   | 6    | μs   |

| $t_{doff00\_spi\_dcm1}$ | Output HS OFF delay<br>(SPI control)<br>SS 50% → OUTx 80%<br>DCmatching = 1 | SR = 00   | -   | -   | 10.5 | μs   |

| $t_{doff01\_spi\_dcm1}$ | Output HS OFF delay<br>(SPI control)<br>SS 50% → OUTx 80%<br>DCmatching = 1 | SR = 01   | -   | -   | 7    | μs   |

| Symbol                  | Parameter                                                                           | Condition | Min   | Typ | Max    | Unit |

|-------------------------|-------------------------------------------------------------------------------------|-----------|-------|-----|--------|------|

| $t_{doff10\_spi\_dcm1}$ | Output HS OFF delay<br>(SPI control)<br>SS 50% → OUTx 80%<br>DCmatching = 1         | SR = 10   | -     | -   | 6      | μs   |

| $t_{doff11\_spi\_dcm1}$ | Output HS OFF delay<br>(SPI control)<br>SS 50% → OUTx 80%<br>DCmatching = 1         | SR = 11   | -     | -   | 6      | μs   |

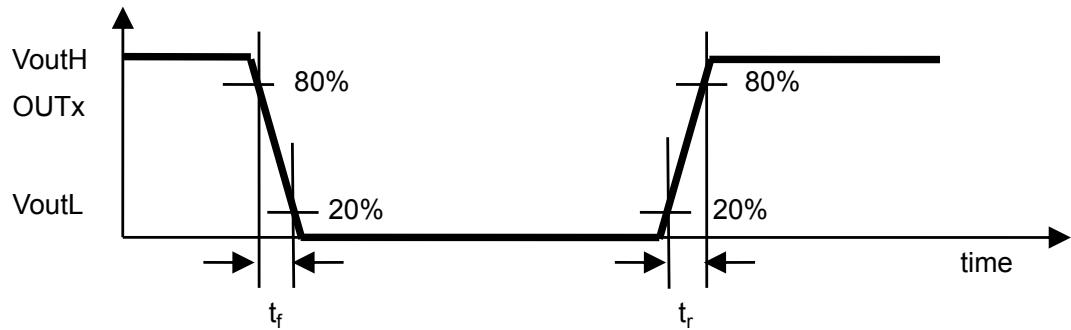

| $t_{r\_HS00\_dcm0}$     | Rise Time HS<br>OUTx 20% → OUTx 80%<br>$V_S = 14$ V; Rload = 14 Ω<br>DCmatching = 0 | SR = 00   | 0.975 | -   | 2.4    | V/μs |

| $t_{r\_HS01\_dcm0}$     | Rise Time HS<br>OUTx 20% → OUTx 80%<br>$V_S = 14$ V; Rload = 14 Ω<br>DCmatching = 0 | SR = 01   | 3.0   | -   | 5.5    | V/μs |

| $t_{r\_HS10\_dcm0}$     | Rise Time HS<br>OUTx 20% → OUTx 80%<br>$V_S = 14$ V; Rload = 14 Ω<br>DCmatching = 0 | SR = 10   | 12.0  | -   | 30.0   | V/μs |

| $t_{r\_HS11\_dcm0}$     | Rise Time HS<br>OUTx 20% → OUTx 80%<br>$V_S = 14$ V; Rload = 14 Ω<br>DCmatching = 0 | SR = 11   | 15.0  | -   | 35.0   | V/μs |

| $t_{r\_HS00\_dcm1}$     | Rise Time HS<br>OUTx 20% → OUTx 80%<br>$V_S = 14$ V; Rload = 14 Ω<br>DCmatching = 1 | SR = 00   | 0.975 | -   | 2.4    | V/μs |

| $t_{r\_HS01\_dcm1}$     | Rise Time HS<br>OUTx 20% → OUTx 80%<br>$V_S = 14$ V; Rload = 14 Ω<br>DCmatching = 0 | SR = 01   | 3     | -   | 5.5    | V/μs |

| $t_{r\_HS10\_dcm1}$     | Rise Time HS<br>OUTx 20% → OUTx 80%<br>$V_S = 14$ V; Rload = 14 Ω<br>DCmatching = 0 | SR = 10   | 12    | -   | 30     | V/μs |

| $t_{r\_HS11\_dcm1}$     | Rise Time HS<br>OUTx 20% → OUTx 80%<br>$V_S = 14$ V; Rload = 14 Ω<br>DCmatching = 0 | SR = 11   | 15.0  | -   | 35.0   | V/μs |

| $t_{f\_HS00\_dcm0}$     | Fall Time HS<br>OUTx 80% → OUTx 20%<br>$V_S = 14$ V; Rload = 14 Ω                   | SR = 00   | -2.4  | -   | -0.975 | V/μs |

| Symbol             | Parameter                                                                                                                        | Condition | Min   | Typ | Max    | Unit       |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------|-------|-----|--------|------------|

|                    | DCmatching = 0                                                                                                                   |           |       |     |        |            |

| $t_f_{HS01\_dcm0}$ | Fall Time HS<br>OUTx 80% → OUTx 20%<br>$V_S = 14 \text{ V}$ ; Rload = 14 $\Omega$<br>DCmatching = 0                              | SR = 01   | -5.5  | -   | -3.0   | V/ $\mu$ s |

| $t_f_{HS10\_dcm0}$ | Fall Time HS<br>OUTx 80% → OUTx 20%<br>$V_S = 14 \text{ V}$ ; Rload = 14 $\Omega$<br>DCmatching = 0                              | SR = 10   | -30.0 | -   | -12.0  | V/ $\mu$ s |

| $t_f_{HS11\_dcm0}$ | Fall Time HS<br>OUTx 80% → OUTx 20%<br>$V_S = 14 \text{ V}$ ; Rload = 14 $\Omega$<br>DCmatching = 0                              | SR = 11   | -35.0 | -   | -15.0  | V/ $\mu$ s |

| $t_f_{HS00\_dcm1}$ | Fall Time HS<br>OUTx 80% → OUTx 20%<br>$V_S = 14 \text{ V}$ ; Rload = 14 $\Omega$<br>DCmatching = 1                              | SR = 00   | -2.4  | -   | -0.975 | V/ $\mu$ s |

| $t_f_{HS01\_dcm1}$ | Fall Time HS<br>OUTx 80% → OUTx 20%<br>$V_S = 14 \text{ V}$ ; Rload = 14 $\Omega$<br>DCmatching = 1                              | SR = 01   | -5.5  | -   | -3     | V/ $\mu$ s |

| $t_f_{HS10\_dcm1}$ | Fall Time HS<br>OUTx 80% → OUTx 20%<br>$V_S = 14 \text{ V}$ ; Rload = 14 $\Omega$<br>DCmatching = 1                              | SR = 10   | -30   | -   | -12    | V/ $\mu$ s |

| $t_f_{HS11\_dcm1}$ | Fall Time HS<br>OUTx 80% → OUTx 20%<br>$V_S = 14 \text{ V}$ ; Rload = 14 $\Omega$<br>DCmatching = 1                              | SR = 11   | -35.0 | -   | -15.0  | V/ $\mu$ s |

| $t_r_{LS00\_dcm0}$ | Rise Time LS<br>OUTx 20% → OUTx 80%<br>$V_S = 14 \text{ V}$ ; Rload = 14 $\Omega$<br>only valid for DIR change<br>DCmatching = 0 | SR = 00   | 0.975 | -   | 2.4    | V/ $\mu$ s |

| $t_r_{LS01\_dcm0}$ | Rise Time LS<br>OUTx 20% → OUTx 80%<br>$V_S = 14 \text{ V}$ ; Rload = 14 $\Omega$<br>only valid for DIR change<br>DCmatching = 0 | SR = 01   | 3.0   | -   | 5.5    | V/ $\mu$ s |

| $t_r_{LS10\_dcm0}$ | Rise Time LS<br>OUTx 20% → OUTx 80%<br>$V_S = 14 \text{ V}$ ; Rload = 14 $\Omega$<br>only valid for DIR change                   | SR = 10   | 12.0  | -   | 30.0   | V/ $\mu$ s |

| Symbol             | Parameter                                                                                                                           | Condition | Min   | Typ | Max   | Unit |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------|-------|-----|-------|------|

|                    | DCmatching = 0                                                                                                                      |           |       |     |       |      |

| $t_r_{LS11\_dcm0}$ | Rise Time LS<br>OUTx 20% → OUTx 80%<br>$V_S = 14 \text{ V}$ ; $R_{load} = 14 \Omega$<br>only valid for DIR change<br>DCmatching = 0 | SR = 11   | 15.0  | -   | 35.0  | V/μs |

| $t_r_{LS00\_dcm1}$ | Rise Time LS<br>OUTx 80% → OUTx 20%<br>$V_S = 14 \text{ V}$ ; $R_{load} = 14 \Omega$<br>only valid for DIR change<br>DCmatching = 1 | SR = 00   | 0.975 | -   | 2.4   | V/μs |

| $t_r_{LS01\_dcm1}$ | Rise Time LS<br>OUTx 80% → OUTx 20%<br>$V_S = 14 \text{ V}$ ; $R_{load} = 14 \Omega$<br>only valid for DIR change<br>DCmatching = 1 | SR = 01   | 3     | -   | 5.5   | V/μs |

| $t_r_{LS10\_dcm1}$ | Rise Time LS<br>OUTx 80% → OUTx 20%<br>$V_S = 14 \text{ V}$ ; $R_{load} = 14 \Omega$<br>only valid for DIR change<br>DCmatching = 1 | SR = 10   | 12    | -   | 3     | V/μs |

| $t_r_{LS11\_dcm1}$ | Rise Time LS<br>OUTx 80% → OUTx 20%<br>$V_S = 14 \text{ V}$ ; $R_{load} = 14 \Omega$<br>only valid for DIR change<br>DCmatching = 1 | SR = 11   | 15    | -   | 35    | V/μs |

| $t_f_{LS00\_dcm0}$ | Fall Time LS<br>OUTx 80% → OUTx 20%<br>$V_S = 14 \text{ V}$ ; $R_{load} = 14 \Omega$<br>DCmatching = 0                              | SR = 00   | -35.0 | -   | -15.0 | V/μs |

| $t_f_{LS01\_dcm0}$ | Fall Time LS<br>OUTx 80% → OUTx 20%<br>$V_S = 14 \text{ V}$ ; $R_{load} = 14 \Omega$<br>DCmatching = 0                              | SR = 01   | -35.0 | -   | -15.0 | V/μs |

| $t_f_{LS10\_dcm0}$ | Fall Time LS<br>OUTx 80% → OUTx 20%<br>$V_S = 14 \text{ V}$ ; $R_{load} = 14 \Omega$<br>DCmatching = 0                              | SR = 10   | -35.0 | -   | -15.0 | V/μs |

| $t_f_{LS11\_dcm0}$ | Fall Time LS<br>OUTx 80% → OUTx 20%<br>$V_S = 14 \text{ V}$ ; $R_{load} = 14 \Omega$<br>DCmatching = 0                              | SR = 11   | -35.0 | -   | -15.0 | V/μs |

| $t_f_{LS00\_dcm1}$ | Fall Time LS                                                                                                                        | SR = 00   | -35.0 | -   | -15.0 | V/μs |

| Symbol             | Parameter                                                                                              | Condition                                           | Min   | Typ | Max   | Unit |

|--------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------|-----|-------|------|

|                    | OUTx 80% → OUTx 20%<br>$V_S = 14 \text{ V}$ ; $R_{load} = 14 \Omega$<br>DCmatching = 1                 |                                                     |       |     |       |      |

| $t_f_{LS01\_dcm1}$ | Fall Time LS<br>OUTx 80% → OUTx 20%<br>$V_S = 14 \text{ V}$ ; $R_{load} = 14 \Omega$<br>DCmatching = 1 | SR = 01                                             | -35.0 | -   | -15.0 | V/μs |

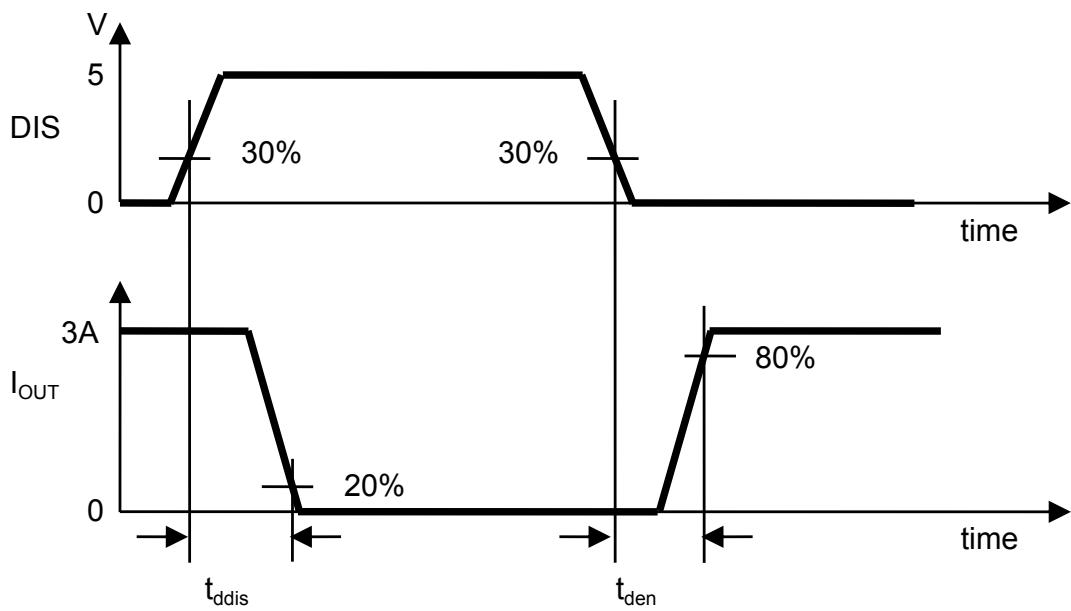

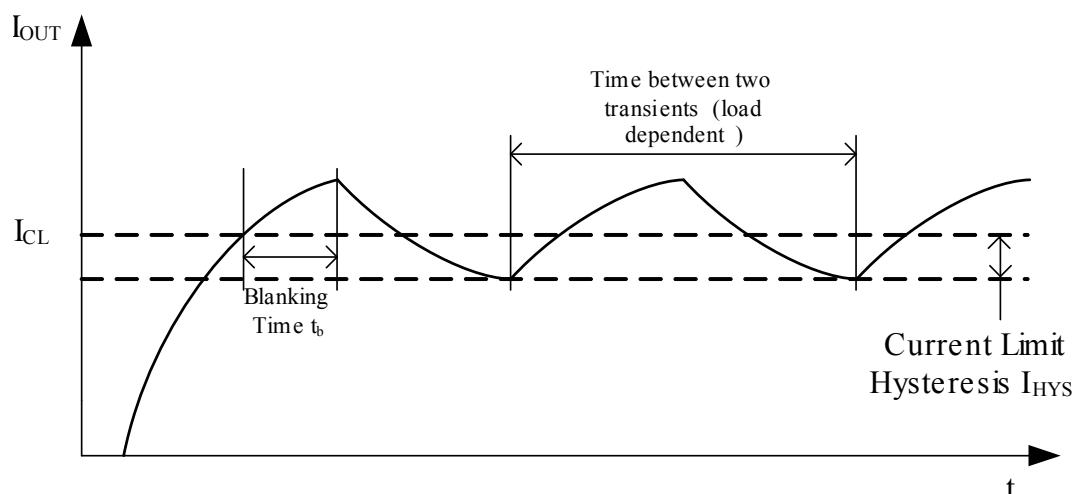

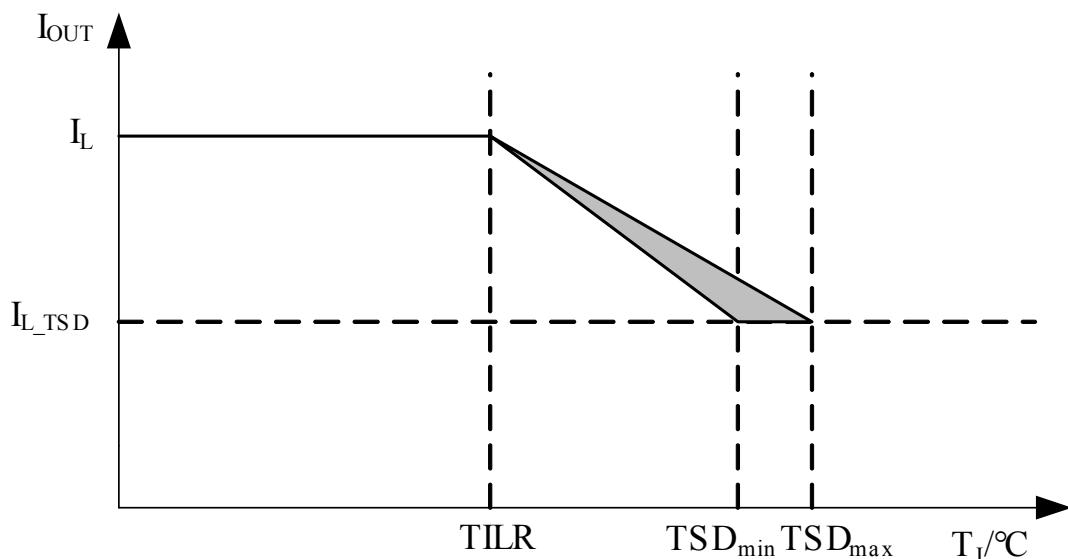

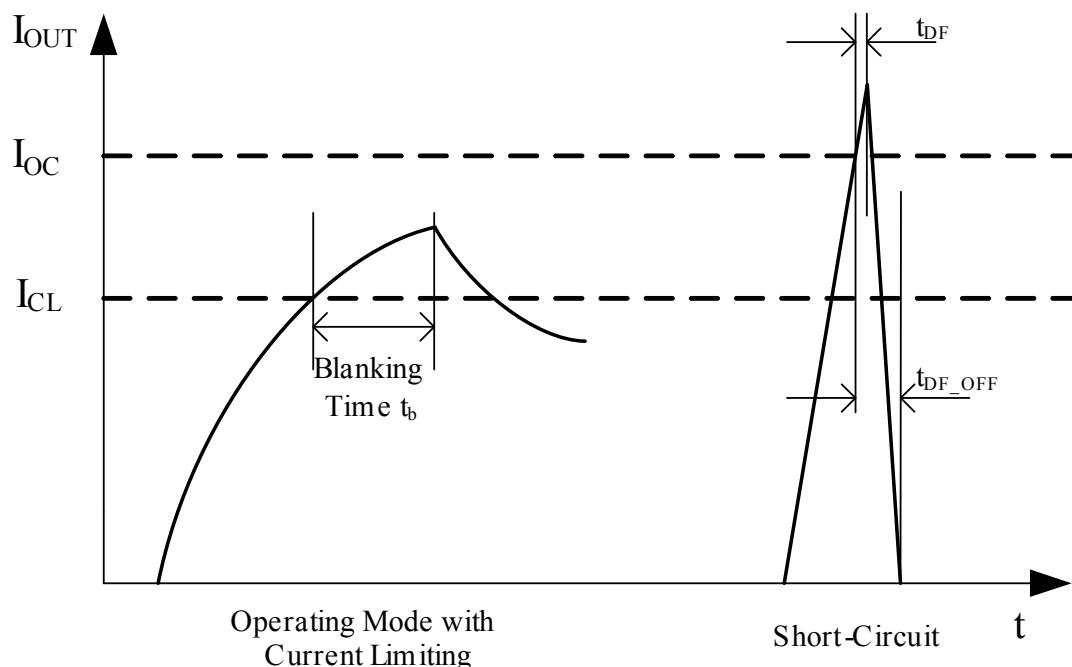

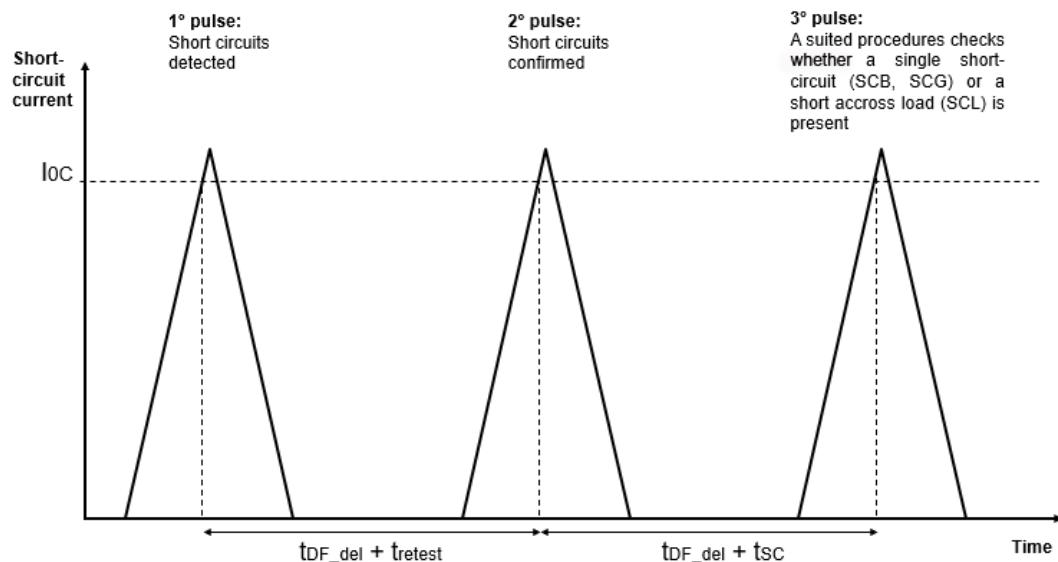

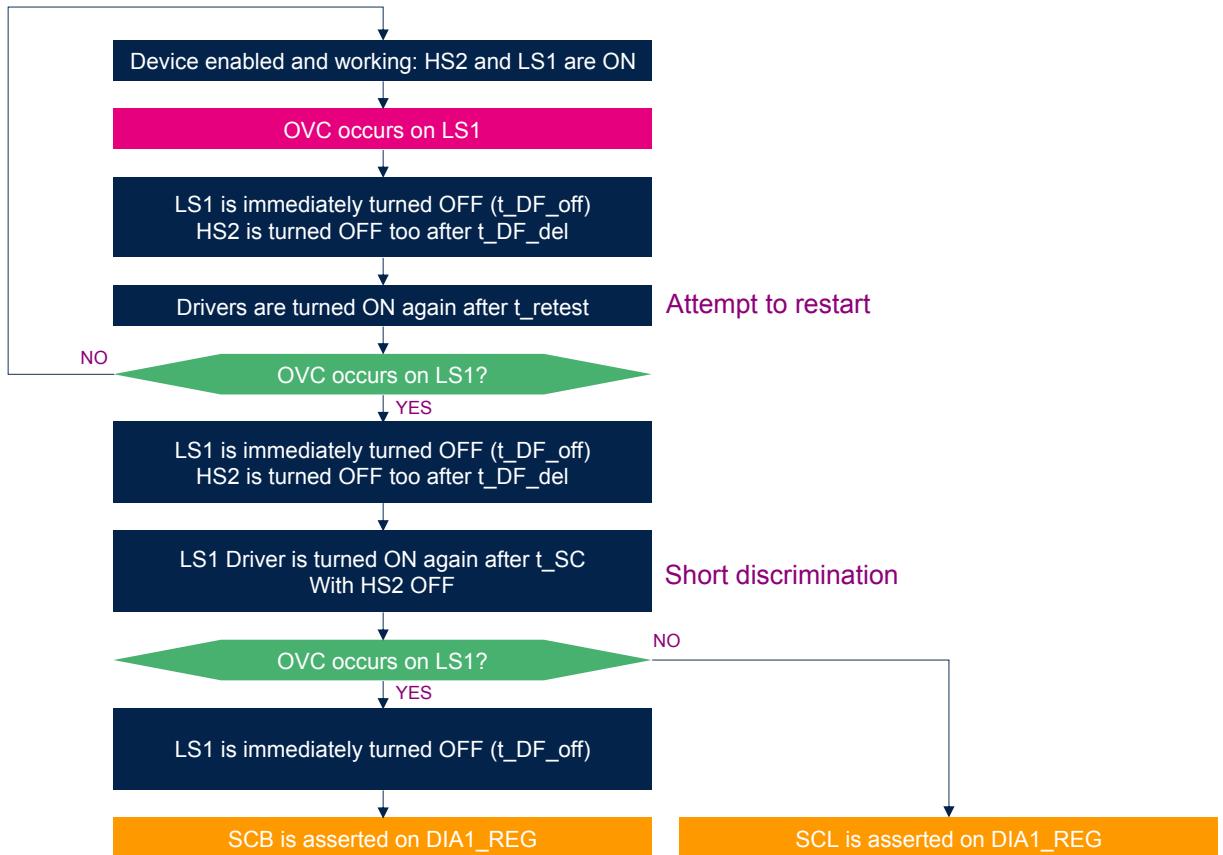

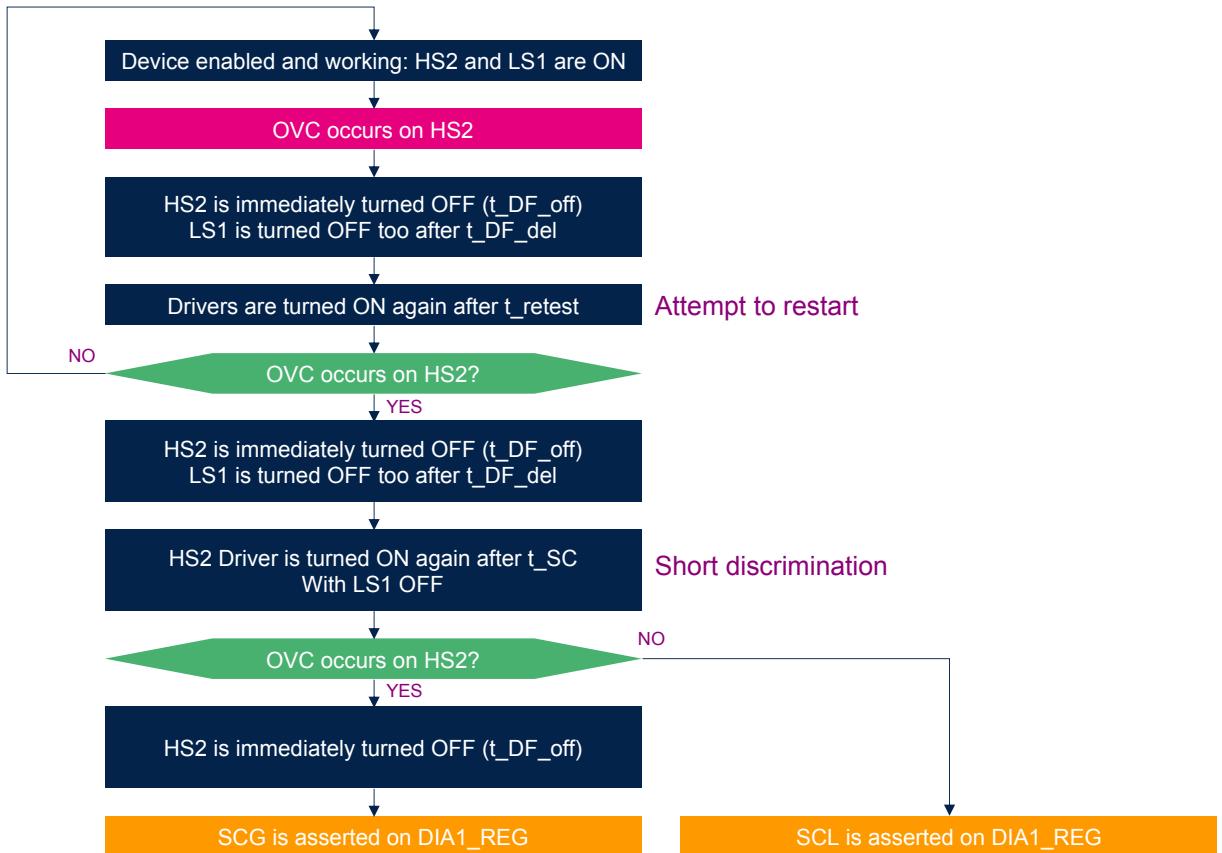

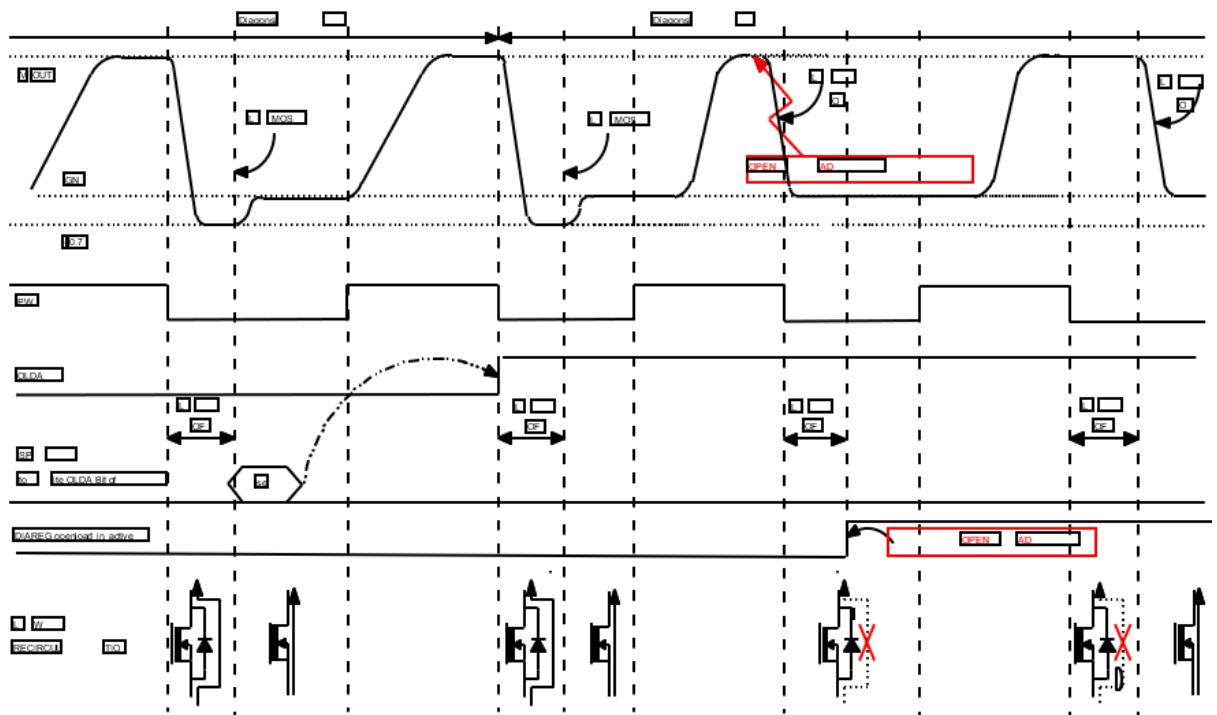

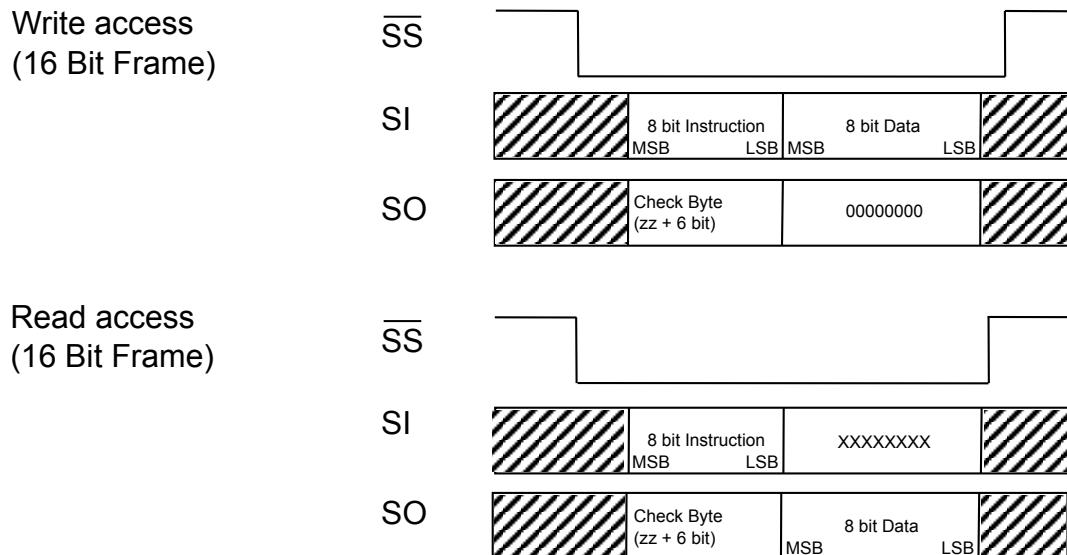

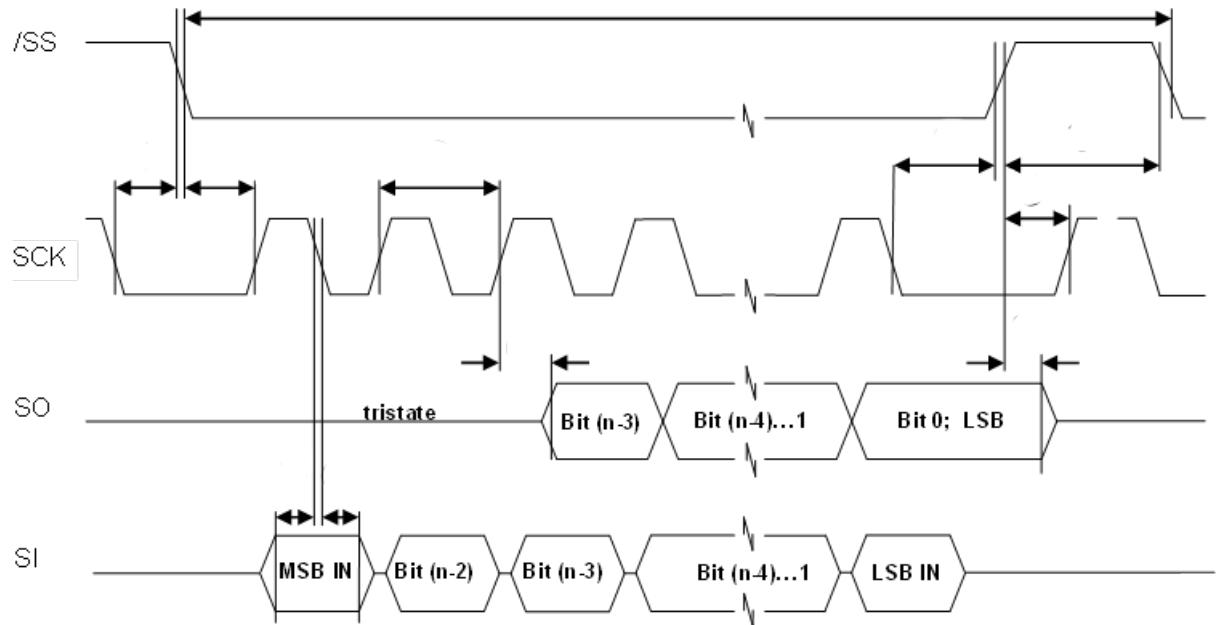

| $t_f_{LS10\_dcm1}$ | Fall Time LS<br>OUTx 80% → OUTx 20%<br>$V_S = 14 \text{ V}$ ; $R_{load} = 14 \Omega$<br>DCmatching = 1 | SR = 10                                             | -35.0 | -   | -15.0 | V/μs |