## Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceed the OCM data sheet.

### **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-35835

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

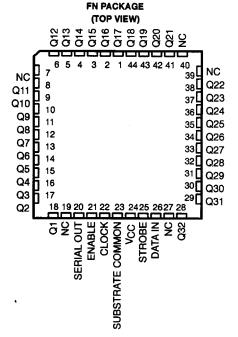

SLDS018B - D2999, DECEMBER 195 - REVISED APRIL 1993

- Each Device Drives 32 Electrodes

- High-Voltage Open-Collector NPN Outputs Using Ramped Supply

- 300-mA Output Current Capability

- CMOS-Compatible Inputs

- Very Low Steady-State Power Consumption

#### description

These devices are monolithic BIDFET<sup>†</sup> integrated circuits designed to drive the row electrodes of an electroluminescent display. All inputs are CMOScompatible, and all outputs are high-voltage open-collector npn transistors.

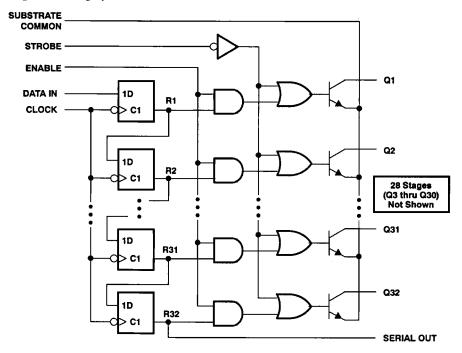

The devices consist of a 32-bit shift register, 32 AND gates, and 32 output OR gates. Typically, a composite row drive signal is externally generated by a high-voltage switching circuit and applied to SUBSTRATE COMMON. Serial data is entered into the shift register on the high-to-low transition of the clock input. A high ENABLE allows those outputs with a high in their associated register to be turned on causing the corresponding row to be connected to the composite row drive signal. When STROBE is low, all output transistors are turned on. The serial data output (SERIAL OUT) from the shift register can be used to cascade additional devices. This output is not affected by the ENABLE or STROBE inputs.

The SN65558 is characterized for operation from -40°C to 85°C. The SN75558 is characterized for operation from 0°C to 70°C.

NC - No internal connection

† BIDFET -- Bipolar, double-diffused, N-channel and P-channel MOS transistors on same chip. This is a patented process.

SLDS018B - D2999, DECEMBER 195 - REVISED APRIL 1993

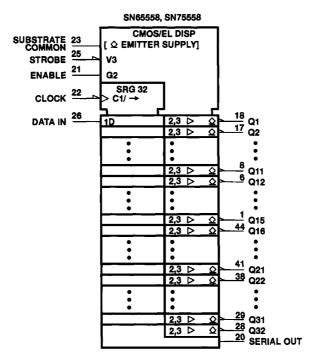

#### logic symbol†

<sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

SLDS018B - D2999, DECEMBER 195 - REVISED APRIL 1993

### logic diagram (positive logic)

#### **FUNCTION TABLE**

| FUNCTION | CONTROL INPUTS |        |        | SHIFT REGISTERS                            | OUTPUTS    |                                                                    |  |  |

|----------|----------------|--------|--------|--------------------------------------------|------------|--------------------------------------------------------------------|--|--|

| TORCTION | CLOCK          | ENABLE | STROBE | R1 THRU R32                                | SERIAL     | Q1 THRU Q32                                                        |  |  |

| Load     | ↓<br>No ↓      | X<br>X | X      | Load and shift <sup>T</sup><br>No change   | R32<br>R32 | Determined by ENABLE and STROBE<br>Determined by ENABLE and STROBE |  |  |

| Enable   | X              | L      | H      | As determined above<br>As determined above | R32<br>R32 | All Q outputs off<br>Determined by R1 through R32                  |  |  |

| Strobe   | Х              | X      | L      | As determined above                        | R32        | All Q outputs on                                                   |  |  |

H = high level, L = low level, X = irrelevant, \( \psi = high-to-low transition \)

<sup>†</sup> Register R32 takes on the state of R31, R31 takes on the state of R30, . . . R2 takes on the state of R1, and R1 takes on the state of the data input.

SLDS018B - D2999, DECEMBER 195 - REVISED APRIL 1993

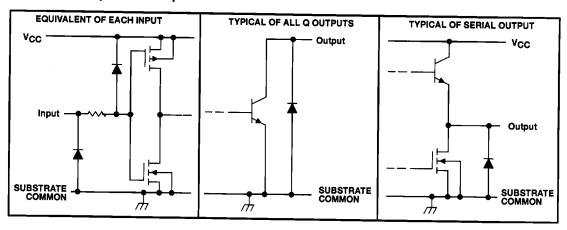

## schematic of inputs and outputs

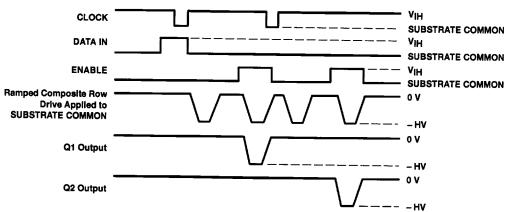

#### typical operating sequence

HV = High voltage

SLDS018B - D2999, DECEMBER 195 - REVISED APRIL 1993

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, V <sub>CC</sub> (see Note 1)                                               | . 18 V  |

|--------------------------------------------------------------------------------------------|---------|

| Off-state output voltage, V <sub>O(off)</sub> (see Note 2)                                 | 110 V   |

| Input voltage, V <sub>I</sub>                                                              | + 0.3 V |

| Substrate common terminal current (see Note 3)                                             | 750 mA  |

| Continuous total power dissipation at (or below) 25°C free-air temperature (see Note 4) 17 | 00 mW   |

| Operating free-air temperature range: SN65558 – 40°C t                                     | o 85°C  |

| SN75558 0°C t                                                                              |         |

| Storage temperature range – 65°C to                                                        |         |

| Case temperature for 10 seconds                                                            | 260°C   |

- NOTE 1: Voltage values are with respect to SUBSTRATE COMMON.

- Data must be clocked into the shift register and Q outputs enabled prior to ramping SUBSTRATE COMMON to -HV (see typical

operating sequence).

- 3. Duty cycle is limited by package dissipation.

- 4. For operation above 25°C free-air temperature, derate linearly to 1088 mW at 70°C, and 884 mW at 85°C at the rate of 13.6 mW/°C.

#### recommended operating conditions

|                                                         |                                                 | ·                        | MIN   | NOM  | MAX  | UNIT                                             |  |

|---------------------------------------------------------|-------------------------------------------------|--------------------------|-------|------|------|--------------------------------------------------|--|

| Supply voltage, V <sub>CC</sub>                         |                                                 | 10.8                     | 12    | 15   | V    |                                                  |  |

| High-level input voltage, VIH (see Figure 1)            | V <sub>CC</sub> = 10.8 V                        | 8.1                      |       | 11.1 |      |                                                  |  |

| riigii-level liiput voii                                | age, VIH (see Figure 1)                         | V <sub>CC</sub> = 15 V   | 11.25 |      | 15.3 | V                                                |  |

| Low-level input voltage, V <sub>IL</sub> (see Figure 1) |                                                 | V <sub>CC</sub> = 10.8 V | -0.3  |      | 2.7  | 1.4                                              |  |

|                                                         |                                                 | V <sub>CC</sub> = 15 V   | -0.3  |      | 3.75 | <b>V</b>                                         |  |

| Off-state Q output v                                    | oltage, VO(off)                                 |                          | -0.3  |      | 100  | V                                                |  |

| On-state Q output of                                    | current, $I_{O(on)}$ , duty cycle $\leq 1\%$ ,  | V <sub>CC</sub> = 15 V   |       |      | 300  | mA                                               |  |

| Rate of rise for SUE                                    | STRATE COMMON, dv/dt                            |                          |       |      | 100  | V/µs                                             |  |

| Clock frequency, fcl                                    | ock                                             | -                        | 0     |      | 4    | MHz                                              |  |

| Pulse duration, CLC                                     | OCK high or low, tw                             |                          | 125   |      |      | ns                                               |  |

| Setup time, t <sub>SU</sub>                             | DATA IN before CLOCK‡ (se                       | ee Figure 2)             | 50    |      |      | <del>                                     </del> |  |

|                                                         | ENABLE before SUBSTRATE COMMON ↓ (see Figure 4) |                          | 500   |      |      | ns                                               |  |

| Hold time, DATA IN                                      | after CLOCK th (see Figure 2)                   |                          | 100   |      |      | ns                                               |  |

| Operating free-air temperature, TA                      |                                                 | SN65558                  | -40   |      | 85   |                                                  |  |

|                                                         |                                                 | SN75558                  | 0     |      | 70   | °C                                               |  |

# electrical characteristics over recommended operating free-air temperature range, $V_{CC}$ = 12 V (unless otherwise noted)

| PARAMETER |                                     |            | TEST CONDITIONS          | SN65558 |     | SN75558 |     |      |

|-----------|-------------------------------------|------------|--------------------------|---------|-----|---------|-----|------|

|           |                                     |            | TEST CONDITIONS          | MIN     | MAX | MIN     | MAX | UNIT |

| IO(off)   | Off-state Q output current          |            | V <sub>O</sub> = 100 V   |         | 20  |         | 10  | μА   |

| Voн       | High-level output voltage           | SERIAL OUT | l <sub>O</sub> = -100 μA | 10.5    |     | 10.5    |     | ٧    |

| VOL       | Low-level output voltage            | Q outputs  | I <sub>OL</sub> = 300 mA |         | 20  |         | 10  | ,,   |

|           |                                     | SERIAL OUT | I <sub>OL</sub> = 100 μA |         | 1   |         | 1   | V    |

| ΊΗ        | High-level input current            |            | V <sub>I</sub> = 12 V    |         | 1   |         | 1   | μА   |

| ll        | Low-level input current             | -          | V <sub>I</sub> = 0       |         | -1  |         | -1  | μА   |

| lcc       | Supply current from V <sub>CC</sub> |            |                          |         | 250 |         | 250 | μА   |

SLDS018B - D2999, DECEMBER 195 - REVISED APRIL 1993

## switching characteristics, $V_{CC} = 12 \text{ V}$ , $T_A = 25 ^{\circ}\text{C}$

| PARAMETER          |                                                                     | TEST CONDITIONS                                                                                 | MIN | MAX | UNIT |

|--------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----|-----|------|

| tPHL               | Propagation delay time, high-to-low-level,<br>SERIAL OUT from CLOCK | C <sub>L</sub> = 20 pF to SUBSTRATE COMMON,                                                     |     | 200 | ns   |

| <sup>†</sup> PLH   | Propagation delay time, low-to-high-level,<br>SERIAL OUT from CLOCK | (see Figure 3)                                                                                  |     | 200 | ns   |

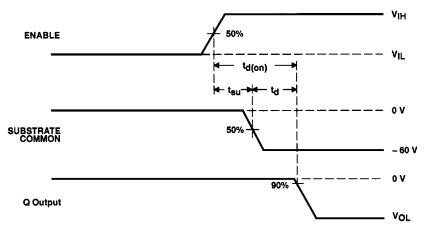

| <sup>t</sup> d(on) | Turn-on delay time, Q outputs from ENABLE                           | $dv/dt = 100 \text{ V/μs, STROBE at V}_{CC}$ , $R_L = 2 \text{ k}\Omega$ to 60 V (see Figure 4) |     | 500 | ns   |

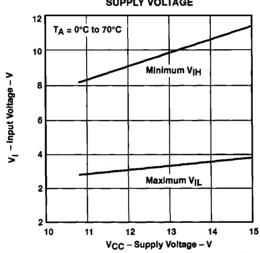

#### RECOMMENDED OPERATING CONDITIONS

# INPUT VOLTAGE LOGIC-LEVEL LIMITS VS SUPPLY VOLTAGE

Figure 1

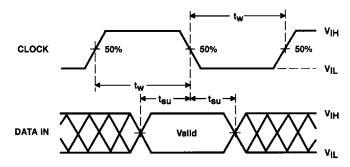

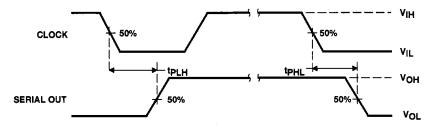

#### PARAMETER MEASUREMENT INFORMATION

Figure 2. Input-Timing Voltage Waveforms

Figure 3. Voltage Waveforms for Propagation Delay Time, CLOCK to SERIAL OUT

Figure 4. Voltage Waveforms for Turn-On Delay Time, SUBSTRATE COMMON to Q Output

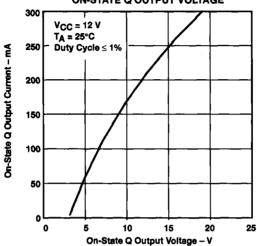

#### TYPICAL CHARACTERISTICS

# ON-STATE Q OUTPUT CURRENT VS ON-STATE Q OUTPUT VOLTAGE

Figure 5