# Dual 8-Bit CMOS D/A Converter with Voltage Output

**DAC8228**

# **FEATURES**

- Two 8-Bit Voltage Out DACs in a Single Chip

- Fits 7528/7628 Sockets

- Adjustment Free Internal CMOS Op Amps

- Single +12V to +15V Operation

- TTL Compatible Over Full V<sub>DD</sub> Range

- Fast Interface Timing ......T<sub>WR</sub> = 50ns

- Improved Resistance to ESD

- · Available in Small Outline Package

- CerDIP and Epoxy Packages Come in the Extended Industrial Temperature Range of -40°C to +85°C

- Available in Die Form

# **APPLICATIONS**

- Disk Drive Systems

- Automatic Test Equipment

- Process/Industrial Controls

- Energy Controls

- Programmable Instrumentation

- Multi-Channel Microprocessor-Controlled Systems

- Servo Control Systems

# ORDERING INFORMATION †

|                                  | PACKAGE: 20-PIN DIP/SOL    |                                                |  |

|----------------------------------|----------------------------|------------------------------------------------|--|

| RELATIVE<br>ACCURACY             | GAIN<br>ERROR              | EXTENDED INDUSTRIAL TEMPERATURE -40°C to +85°C |  |

| ±1/2 LSB<br>±1/2 LSB<br>±1/2 LSB | ±2 LSB<br>±2 LSB<br>±2 LSB | DAC8228FR<br>DAC8228FP<br>DAC8228FS            |  |

<sup>†</sup> All commercial and industrial temperature range parts are available with burning

# **GENERAL DESCRIPTION**

The DAC-8228 is a dual 8-bit, voltage output, CMOS, D/A converter in a single chip. It was designed to drop into AD7528/7628 sockets eliminating two external op amps in applications such as hard disk drives. These applications generally operate the AD7528/7628 with zero volts applied to  $V_{\rm REF}$  and offset AGND to +2.5 or +5 volts. The DAC-8228 is tested under both these conditions

The DAC-8228 can also be used in those applications requiring a unipolar output voltage. It can deliver an output voltage between 0V and +10V with  $V_{\rm DD}$  = +14V (maximum output voltage is  $V_{\rm DD}$  -4V). The DAC-8228's reference input can accept a negative voltage from 0V to –10V (the DAC's internal unity-gain inverting amplifier inverts the input signal). Choose the DAC-8229 for bipolar operation.

Continued

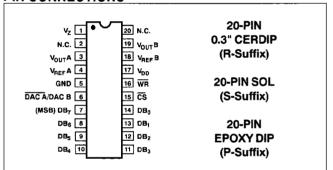

# **PIN CONNECTIONS**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 Fax: 617/326-8703 Twx: 710/394-6577

Telex: 924491 Cable: ANALOG NORWOODMASS

# **GENERAL DESCRIPTION Continued**

The DAC-8228 offers CerDIP and plastic packaged devices in the extended industrial temperature range of –40°C to +85°C. Applications requiring the military temperature range should use the DAC-8229. To make the DAC-8229 pin and functionally compatible with the DAC-8228, AGND A and AGND B should be tied together to function as  $\rm V_{z}$ , and  $\rm V_{SS}$  connected to GND.

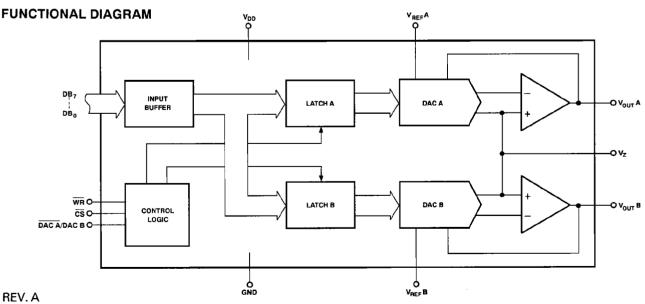

The DAC-8228 consists of two CMOS voltage output amplifiers, two high-accuracy R-2R resistor ladder networks, interface control logic, and two 8-bit registers. An internal regulator maintains TTL logic compatibility and fast microprocessor interface timing over the full  $\mbox{V}_{\rm DD}$  range.

The DAC-8228 dissipates only 90mW in the space saving 20-pin 0.3" DIP or the 20-lead SO surface mount package. Its compact size, low power, and economical cost per channel, makes it attractive for applications requiring multiple D/A converters without sacrificing circuit-board space. Reduced parts count also improves system reliability.

Using PMI's advanced oxide-isolated, silicon-gate CMOS process, coupled with its highly-stable thin-film resistor ladder, allows the DAC-8228 to offer superior matching and temperature tracking between DACs.

# **ABSOLUTE MAXIMUM RATINGS**

| $(T_{\Delta} = +25^{\circ}C, \text{ unless otherwise noted.})$                      |                        |

|-------------------------------------------------------------------------------------|------------------------|

| $(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$<br>$V_{DD}$ to $V_Z$ or GND | 0.3V, +17V             |

| V <sub>z</sub> to GND                                                               | 0.3V, V <sub>DD</sub>  |

| Digital Input Voltage to GND                                                        | –0.3V, V <sub>D</sub>  |

| V <sub>BEE A</sub> , V <sub>BEE B</sub> to GND                                      | –17V, Ŭ,               |

| V <sub>REF A</sub> , V <sub>REF B</sub> to GND                                      | –0.3V, V <sub>DD</sub> |

| Operating Temperature Range                                                         |                        |

| FR/FP/FS Versions                                                                   | 40°C to +85°C          |

| Junction Temperature                                                                | +150°C                 |

| Storage Temperature                                                                 | 65°C to +150°C         |

| Lead Temperature (Soldering, 60 sec)                                                |                        |

| PACKAGE TYPE            | Θ <sub>jA</sub> (NOTE 3) | $\Theta_{jC}$ | UNITS |

|-------------------------|--------------------------|---------------|-------|

| 20-Pin Hermetic DIP (R) | 76                       | 11            | °C/W  |

| 20-Pin Plastic DIP (P)  | 69                       | 27            | °C/W  |

| 20-Pin SOL (S)          | 88                       | 25            | °C/W  |

### NOTES:

- Outputs may be shorted to any terminal provided the package power dissipation is not exceeded. Typical output short-circuit current to GND is 50mA.

- 2. Use proper anti-static handling procedures when handling these devices.

- Θ<sub>jA</sub> is specified for worst case mounting conditions, i.e., Θ<sub>jA</sub> is specified for device in socket for CerDIP and P-DIP packages; Θ<sub>jA</sub> is specified for device soldered to printed circuit board for SOL package.

**ELECTRICAL CHARACTERISTICS** at  $V_{DD}$  = +12V ±5%,  $V_{REF}$  = 0V,  $V_{Z}$  = +2.5V and  $V_{DD}$  = +15V ±5%,  $V_{REF}$  = 0V,  $V_{Z}$  = +5V. T<sub>A</sub> = Full Temperature Range specified under Absolute Maximum Ratings, unless otherwise noted.

| PARAMETER                                                         | SYMBOL            | CONDITIONS                        | MIN | DAC-8228 | MAX    | UNITS |

|-------------------------------------------------------------------|-------------------|-----------------------------------|-----|----------|--------|-------|

| STATIC ACCURACY (Note 1)                                          |                   |                                   |     |          |        |       |

| Resolution                                                        | N                 |                                   | 8   |          | -      | Bits  |

| Relative Accuracy<br>(Note 2)                                     | INL               |                                   | -   | <b></b>  | ±1     | LSB   |

| Differential Nonlinearity (Note 3)                                | DNL               |                                   | -   | -        | ±1     | LSB   |

| Gain Error                                                        | G <sub>FSE</sub>  | DAC Latches Loaded with 1111 1111 |     | _        | ±2     | LSB   |

| Gain Error Temperature Coefficient (Note 4)                       | TCG <sub>FS</sub> |                                   | _   | ±0.0003  | ±0.002 | %/°C  |

| Zero Code Error                                                   | V <sub>ZSE</sub>  |                                   | _   | ates     | ±15    | mV    |

| Zero Code Error<br>Temperature Coefficient<br>(Note 4)            | TCV <sub>zs</sub> |                                   | · - | ±10      | _      | μV/°C |

| REFERENCE INPUT (Note 8)                                          |                   |                                   |     |          | ·      |       |

| Input Resistance<br>(Note 5)                                      | R <sub>IN</sub>   | Pin 4 and Pin 18                  | 7   | _        | 15     | kΩ    |

| Input Resistance Match<br>(V <sub>REF</sub> A/V <sub>REF</sub> B) | AR <sub>IN</sub>  |                                   | _   | ±0.1     | ±1     | %     |

| Input Capacitance<br>(Note 4)                                     | C <sub>IN</sub>   |                                   | _   | 9        | 20     | pF    |

| V <sub>Z</sub> Input Resistance<br>(Note 10)                      | R <sub>VZ</sub>   | Digital Inputs = 0V               | 2   |          | _      | kΩ    |

**ELECTRICAL CHARACTERISTICS** at  $V_{DD}$  = +12V ±5%,  $V_{REF}$  = 0V,  $V_{Z}$  = +2.5V and  $V_{DD}$  = +15V ±5%,  $V_{REF}$  = 0V,  $V_{Z}$  = +5V.  $T_{A}$  = Full Temperature Range specified under Absolute Maximum Ratings, unless otherwise noted. *Continued*

| PARAMETER                                                          | SYMBOL           | CONDITIONS                                                                                                                    | MIN | DAC-8228<br>TYP | MAX  | UNITS  |

|--------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------|-----|-----------------|------|--------|

| DIGITAL INPUTS                                                     | 31MBOL           | CONDITIONS                                                                                                                    |     |                 | WIAA | 011110 |

| Digital Input High                                                 | V <sub>INH</sub> |                                                                                                                               | 2.4 | _               | _    | V      |

| Digital Input Low                                                  | V <sub>INL</sub> |                                                                                                                               | -   | _               | 0.8  | V      |

| Input Current                                                      | I <sub>IN</sub>  | V <sub>IN</sub> = 0V or V <sub>DD</sub>                                                                                       | _   | -               | ±1   | μΑ     |

| Input Capacitance<br>(Note 4)                                      | C <sub>IN</sub>  |                                                                                                                               | -   | 4               | 8    | pF     |

| POWER SUPPLIES                                                     |                  |                                                                                                                               |     |                 |      |        |

| Supply Current<br>(Note 6)                                         | I <sub>DD</sub>  |                                                                                                                               | _   | -               | 7    | mA     |

| Power                                                              | P <sub>D</sub>   | V <sub>DD</sub> = +12V<br>12 x 7mA                                                                                            | -   | -               | 84   | mW     |

| Dissipation                                                        | Ь                | V <sub>D D</sub> = +15V<br>15 x 7mA                                                                                           | _   | -               | 105  |        |

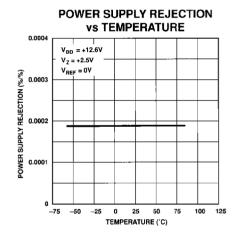

| DC Power Supply Rejection Ratio $(\Delta Gain/\Delta V_{DD})$      | PSRR             | $\Delta V_{DD} = \pm 5\%$                                                                                                     | _   | _               | 0.01 | %/%    |

| DYNAMIC PERFORMANCE                                                |                  |                                                                                                                               |     |                 |      |        |

| Slew Rate (V <sub>OUT</sub> )<br>(Note 4)                          | SR               | T <sub>A</sub> = +25°C<br>Digital Inputs = 0V to +5V                                                                          | _   | 2.5             |      | V/μs   |

| Settling Time (V <sub>OUT</sub> ) Positive or Negative (Note 4, 7) | t <sub>s</sub>   | Digital Inputs = 0V to +5V                                                                                                    | -   | 2               | 5    | μs     |

| Channel-to-Channel<br>Isolation (Note 4)                           | CCI              | $T_A = +25^{\circ}C$<br>$V_{REF}B$ to $V_{OUT}A$ or $V_{REF}A$ to $V_{OUT}B$<br>$V_{REF}B = V_{REF}A = 20V_{p.p} @ f = 10kHz$ | _   | -80             | -    | dB     |

| Digital Crosstalk<br>(Notes 4, 9)                                  | Q                | T <sub>A</sub> = +25°C<br>For Code Transition<br>0000 0000 to 1111 1111                                                       | -   | 4               | 10   | nVs    |

| Digital Charge<br>Injection                                        | Q                | T <sub>A</sub> = +25°C<br>For Code Transition<br>0000 0000 to 1111 1111                                                       | -   | 100             | -    | nVs    |

| AC Feedthrough (Notes 4, 11)                                       | FT               |                                                                                                                               |     | 10AA            | -70  | dB     |

| Harmonic Distortion                                                | THD              | $T_A = +25^{\circ}C$<br>$V_{IN} = 6V_{RMS} @ f = 1kHz$                                                                        |     | -85             | -    | dB     |

**ELECTRICAL CHARACTERISTICS** at  $V_{DD}$  = +12V ±5%,  $V_{REF}$  = 0V,  $V_{Z}$  = +2.5V and  $V_{DD}$  = +15V ±5%,  $V_{REF}$  = 0V,  $V_{Z}$  = +5V. T<sub>A</sub> = Full Temperature Range specified under Absolute Maximum Ratings, unless otherwise noted. *Continued*

|                                     |                  |            |     | DAC-8228 |     |       |

|-------------------------------------|------------------|------------|-----|----------|-----|-------|

| PARAMETER                           | SYMBOL           | CONDITIONS | MIN | TYP      | MAX | UNITS |

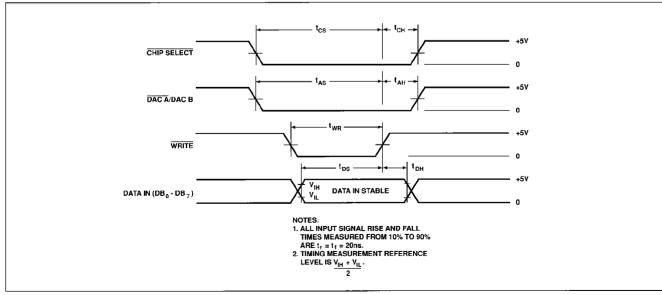

| SWITCHING CHARACTER                 | RISTICS (Note 4) |            |     |          |     |       |

| Chip Select to<br>Write Set-Up Time | t <sub>cs</sub>  |            | 60  | -        | -   | ns    |

| Chip Select to<br>Write Hold Time   | t <sub>CH</sub>  |            | 10  |          | _   | ns    |

| DAC Select to<br>Write Set-Up Time  | t <sub>AS</sub>  |            | 60  | -        | -   | ns    |

| DAC Select to<br>Write Hold Time    | t <sub>AH</sub>  |            | 10  | -        | -   | ns    |

| Data Valid to<br>Write Set-Up Time  | t <sub>DS</sub>  |            | 60  | -        | _   | ns    |

| Data Valid to<br>Write Hold Time    | t <sub>DH</sub>  |            | 10  | -        | -   | ns    |

| Write Pulse Width                   | t <sub>w B</sub> |            | 50  |          | _   | ns    |

### NOTES:

- 1. Specifications apply to both DAC A and DAC B.

- 2. This is an endpoint linearity specification.

- All devices are guaranteed to be monotonic over the full operating temperature

- These characteristics are for design guidance only and not subject to production test.

- 5. Input resistance temperature coefficient =  $+300 ppm/^{\circ}C$ .

- 6.  $V_{IN} = V_{INL}$  or  $V_{INH}$ ; outputs unloaded. 7.  $V_{REF} = \pm 2.5V$ ; to where output settles to  $\pm 1/2$  LSB.

- V<sub>REF</sub> voltage range is 0V to -10V; the absolute maximum negative value is: |V<sub>REF</sub>| = V<sub>DD</sub>-4V.

Digital crosstalk is a measure of the amount of digital input pulse appearing at

- the analog output of the unselected DAC while applying it to the digital inputs

- 10. Resistance looking into the V<sub>Z</sub> terminal.

11. V<sub>REF</sub>A, V<sub>REF</sub>B = 20V<sub>p-p</sub> Sinewave @ f = 10kHz; V<sub>REF</sub>A to V<sub>OUT</sub>A or V<sub>REF</sub>B to V<sub>OUT</sub>B, both DAC latches loaded with 0000 0000.

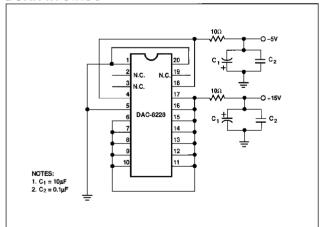

# **BURN-IN CIRCUIT**

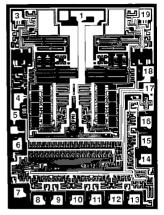

# **DICE CHARACTERISTICS**

DIE SIZE 0.082x 0.111 inch, 9,102 sq. mils (2.08 x 2.82 mm, 5.87 sq. mm)

- 1. AMPLIFIER REFERENCE (V<sub>2</sub>)

- 2. N.C.

- 3. VOLTAGE OUTPUT (V<sub>OUT</sub>A)

4. DAC A REFERENCE INPUT (V<sub>REF</sub>A)

- 5. GROUND (GND)

- 6. DAC SELECTION (DAC A/DAC B)

- 7. DIGITAL INPUT DB, (MSB)

- 8. DIGITAL INPUT DB

- 9. DIGITAL INPUT DB

- 10. DIGITAL INPUT DB

- 11. DIGITAL INPUT DB.

- 12. DIGITAL INPUT DB,

- 13. DIGITAL INPUT DB.

- 14. DIGITAL INPUT DB (LSB)

- 15. CHIP SELECT (CS)

- 16. WRITE (WR)

- 17. POSITIVE POWER SUPPLY (VDD)

- 18. DAC B REFERENCE INPUT (VREFB)

- 19. VOLTAGE OUTPUT (V<sub>OLIT</sub>B)

- 20. N.C.

Substrate (die backside) is internally connected to V<sub>pp</sub>.

# **WAFER TEST LIMITS** at $V_{DD} = V_{DD} = +12V \pm 5\%$ , $V_{REF} = 0V$ , $V_{Z} = 2.5V$ or $V_{DD} = +15V \pm 5\%$ , $V_{REF} = 0V$ , $V_{Z} = +5V$ , $T_{A} = +25^{\circ}C$ .

| PARAMETER                                                       | SYMBOL                              | CONDITIONS                        | DAC-8228GBC<br>LIMITS | UNITS         |

|-----------------------------------------------------------------|-------------------------------------|-----------------------------------|-----------------------|---------------|

| Relative Accuracy<br>(Note 3)                                   | INL                                 | Endpoint Linearity Error          | ±1                    | LSB MAX       |

| Differential Nonlinearity (Notes 1, 3)                          | DNL                                 |                                   | ±1                    | LSB MAX       |

| Gain Error                                                      | G <sub>FSE</sub>                    | DAC Latches Loaded with 1111 1111 | ±2                    | LSB MAX       |

| Zero Code Error                                                 | V <sub>ZSE</sub>                    |                                   | ±15                   | mV MAX        |

| Input Resistance                                                | R <sub>IN</sub>                     | Pad 4 and 18                      | 7/15                  | kΩ ΜΙΝ/kΩ ΜΑΧ |

| V <sub>REF</sub> A/V <sub>REF</sub> B Input<br>Resistance Match | ΔR <sub>IN</sub><br>R <sub>IN</sub> |                                   | 1                     | % MAX         |

| V <sub>Z</sub> Input Resistance<br>(Note 3)                     | R <sub>VZ</sub>                     | Digital Inputs = 0V               | 2                     | kΩ MIN        |

| Digital Input High                                              | V <sub>IH</sub>                     |                                   | 2.4                   | V MIN         |

| Digital Input Low                                               | V <sub>IL</sub>                     |                                   | 0.8                   | V MAX         |

| Input Current                                                   | I <sub>IN</sub>                     | $V_{IN} = 0V \text{ or } V_{DD}$  | ±1                    | μА МАХ        |

| DC Supply Rejection (ΔGain/ΔV <sub>D D</sub> )                  | PSRR                                | V <sub>DD</sub> = ±5%             | 0.01                  | %/% MAX       |

| Positive Supply Current (Note 2)                                | I <sub>DD</sub>                     |                                   | 7                     | mA MAX        |

- 1. All dice guaranteed monotonic over the full operating temperature range.

- V<sub>IN</sub> = V<sub>INL</sub> or V<sub>INH</sub>; output unloaded.

Resistance looking into the V<sub>Z</sub> terminal.

Electrical tests are performed at wafer probe to the limits shown. Due to variations in assembly methods and normal yield loss, yield after packaging is not guaranteed for standard product dice. Consult factory to negotiate specifications based on dice lot qualifications through sample lot assembly and testing.

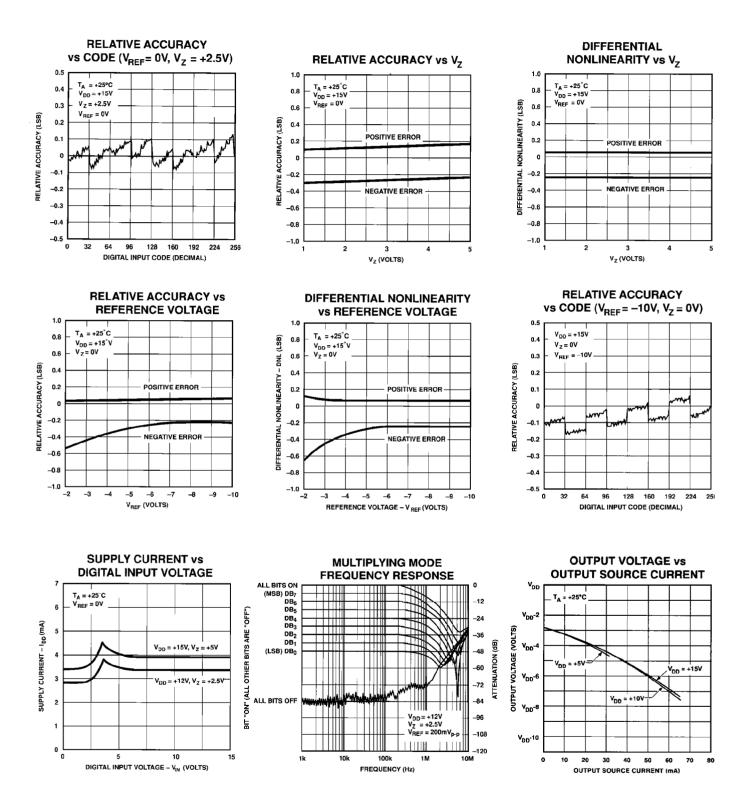

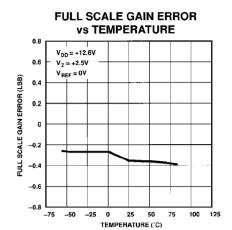

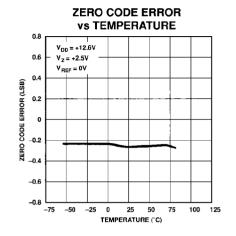

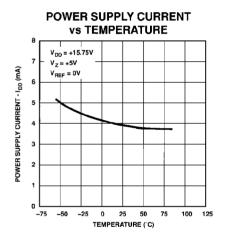

# TYPICAL PERFORMANCE CHARACTERISTICS

# TYPICAL PERFORMANCE CHARACTERISTICS Continued

# WRITE CYCLE TIMING DIAGRAM

# **PARAMETER DEFINITIONS**

# **RESOLUTION (N)**

The resolution of a DAC is the number of states (2<sup>n</sup>) that the fullscale range (FSR) is divided (or resolved) into; where n is equal to the number of bits.

# **RELATIVE ACCURACY (INL)**

Relative accuracy, or integral nonlinearity, is the maximum deviation of the analog output (from the ideal) from a straight line drawn between the end points. It is expressed in terms of least significant bits (LSB), or as a percent of full-scale.

## DIFFERENTIAL NONLINEARITY (DNL)

Differential nonlinearity is the worst case deviation of any adiacent analog output from the ideal 1 LSB step size. The deviation of the actual "step size" from the ideal step size of 1 LSB is called the differential nonlinearity error or DNL. DACs with DNL greater than ±1 may be non-monotonic. ±1/2 LSB INL guarantees monotonicity and ±1 LSB maximum DNL.

GAIN ERROR ( $G_{\rm FSE}$ ) Gain error is the difference between the actual and the ideal analog output range, expressed as a percent of full-scale or in terms of LSB value. It is the deviation in slope of the DAC transfer characteristic from ideal. Zero code error is not included in this measurement.

**ZERO CODE ERROR (V<sub>ZSE</sub>)**Zero Code Error means, for the DAC-8228 specification table, the amount of offset voltage referenced to  $V_7$ , i.e.,  $V_7 = +2.5V$ , ±10mV offset is equal to +2.490V to +2.510V referenced to ground.

See Orientation in Digital-to-Analog Converters Section of the current data book, for additional parameter definitions.

# **GENERAL CIRCUIT DESCRIPTION**

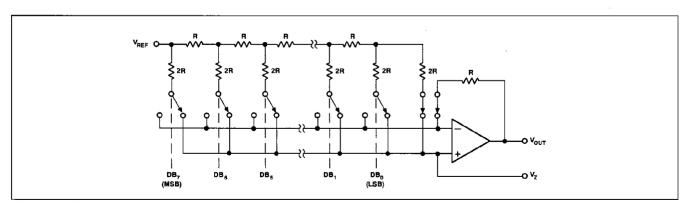

The DAC-8228 consists of two voltage output amplifiers, two high accuracy R-2R resistor ladder networks, an 8-bit input buffer, two 8-bit DAC registers, and interface control logic circuitry.

Also included are 16 single-pole, double-throw NMOS transistor switches. These switches, which are controlled by the digital input code, were designed to switch each 2R resistor leg between the amplifier inverting input and V2, see Figure 1. This configuration inverts the reference input voltage, and also allows biasing V<sub>2</sub> above digital ground simplifying many applica-

### REFERENCE INPUT

The DAC-8228's reference input voltage range is limited by the internal amplifier voltage swing. The amplifier output can swing from 0V to +10V when  $V_{\rm DD}$  = +14V; note that the output voltage is 4 volts less than  $V_{\rm DD}$ .  $V_{\rm DD}$  –4V sets the maximum voltage that the reference input can accept (but in the negative direction due to the inverting amplifier, see Figure 1).  $V_{\rm REF}$  voltage range is 0V to  $-|V_{DD}-4V|$ ; in equation form:  $-V_{BEF}(max) = |V_{DD}-4V|$ .

# **BUFFER AMPLIFIER SECTION**

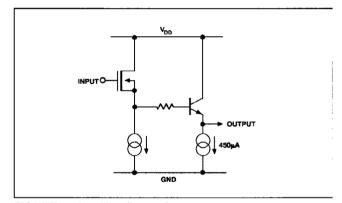

The DAC-8228 internal amplifier's output stage is an NPN bipolar transistor connected to a 450µA current source, see Figure 2. This transistor provides a low output impedance that can drive 5mA across a 2k load. In fact, it can drive up to 65mA, but with a reduced output amplitude. See the Output Voltage vs. Output Source Current graph under the typical electrical characteristics curves. The user must use caution that the package power dissipation is not exceeded when driving low impedances and high currents.

FIGURE 2: Amplifier Output Stage

FIGURE 1: Simplified single DAC configuration (switches shown for all digital inputs at logic "0").

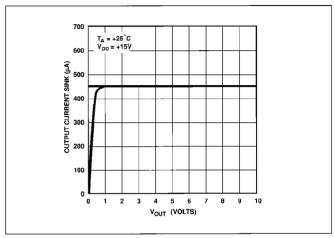

Figure 3 depicts a typical output current-sink versus voltage graph for the amplifier's output stage. It shows the output coming out of its saturation region and starting to appear resistive as the output approaches zero volts.

The amplifier's internal gain stages were designed to maintain sufficient gain over its common mode range. This results in good offset performance over the specified voltage range. In addition, the amplifier's offset voltage is laser-trimmed during manufacturing. This eliminates user offset trimming.

FIGURE 3: DAC Output Current Sink

# **DIGITAL SECTION**

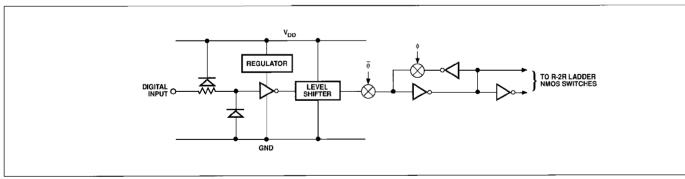

Figure 4 shows one digital input structure of the DAC-8228. A built-in 5V regulator and level shifter converts TTL digital input signals into CMOS levels to drive the internal circuitry. This provides full TTL compatibility over a V<sub>DD</sub> range of 5 to 15V.

As shown in Figure 4, each digital input is protected from electrostatic-discharge with two internal diodes connected between  $V_{\rm DD}$  and GND. Each input has a typical input current of less than 1nA.

# INTERFACE CONTROL INFORMATION

# DAC SELECTION

DAC A and DAC B both share a common 8-bit input port. The control input, DAC A/DAC B, selects which DAC can accept data from the input port. A logic low selects DAC A and a logic high selects DAC B.

# **DAC OPERATION**

Inputs  $\overline{CS}$  and  $\overline{WR}$  control the operation of the selected DAC. See Mode Selection Table below.

### WRITE MODE

When  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  are both low, the selected DAC is in the write mode. The input buffer and DAC register of the selected DAC are transparent and its analog output responds to the codes on the digital input pins.

### HOLD MODE

The selected DAC register latches the data present on the digital input pins just prior to  $\overline{CS}$  and  $\overline{WR}$  assuming a high state. Both analog outputs remain at the values corresponding to the data in their respective registers.

# **MODE SELECTION TABLE**

| DAC A/<br>DAC B | <u>CS</u> | WR | DAC A | DAC B |

|-----------------|-----------|----|-------|-------|

| L               | L         | L  | WRITE | HOLD  |

| Н               | L         | L  | HOLD  | WRITE |

| Χ               | Н         | Χ  | HOLD  | HOLD  |

| X               | Χ         | Н  | HOLD  | HOLD  |

L = Low State H = High State X = Don't Care

FIGURE 4: Simplified Digital Input Structure

# **APPLICATIONS INFORMATION**

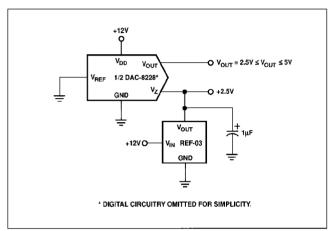

Figure 5 shows the DAC-8228 configured to operate with  $\rm V_Z$  biased above ground. Note how the reference source is connected between  $\rm V_Z$  and ground; also note how the DAC's  $\rm V_{REF}$  pin is connected directly to ground. Not shown but equally important is that the reference voltage source at  $\rm V_Z$  is common to both DAC A and DAC B.

**FIGURE 5**: Single Supply Configuration  $(+2.5V \le V_{OUT} \le +5V)$

The +2.5V reference voltage is obtained from PMI's REF-03; if greater accuracy is desired, use the REF-43. The REF-02 or REF-05, depending on accuracy required, can be used for +5V applications.

The transfer equation for the circuit of Figure 5 is:

$$V_{OLIT} = V_{Z} (1 + D/256)$$

where

V<sub>Z</sub> = Reference voltage applied to V<sub>Z</sub> D = whole number binary digital input

With all 1s on the digital inputs for the circuit of Figure 5,  $\rm V_{OUT}$  results in:

$$V_{OUT} = 2.5(1 + 255/256)$$

= +5V

And with all 0s on all digital inputs:

$$V_{OUT} = +2.5V$$

Note that this configuration's output voltage range is determined by the input reference voltage and  $V_Z$ . A digital zero input provides an output voltage equal to  $V_Z$ . An all ones digital input provides an output voltage equal to:  $2(V_Z - V_{REF})$ .

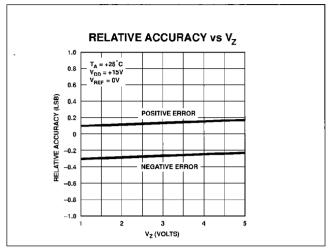

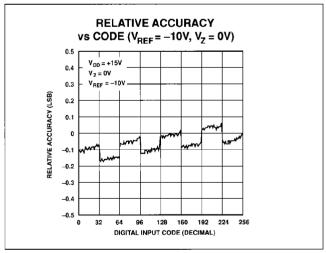

Figure 6 shows a plot of Relative Accuracy versus  $V_7$  voltage.

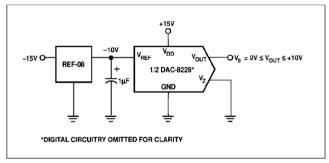

Figure 7 shows the DAC-8228 in another single supply configuration. In this circuit, a PMI REF-08 is used for the reference voltage source and  $\rm V_Z$  is grounded. The output swings from 0V to +10V, see Figure 8.

FIGURE 6: Relative Accuracy vs. AGND

**FIGURE 7**: Single Supply Configuration ( $V_O \le V_{OUT} \le +10V$ )

**FIGURE 8**: Relative Accuracy vs.  $V_{RFF}(V_7 = 0V)$

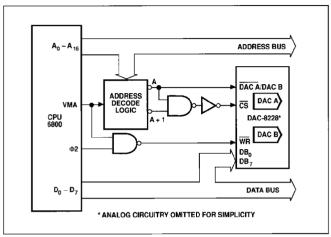

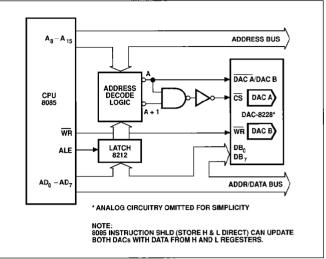

# MICROPROCESSOR INTERFACE CIRCUITS

The DAC-8228's versatile input structure allows direct interface to 8- or 16-bit microprocessors. Its simplicity reduces the number of required glue logic components. Figures 9 and 10 show the DAC-8228 interface configurations with the 6800 and 8085 microprocessors.

FIGURE 9: DAC-8228 Interface to 6800 Microprocessor

FIGURE 10: DAC-8228 Interface to 8085 Microprocessor

REV. A --11-