# CMOS 12-Bit Multiplying D/A Converter "With Memory"

DAC-8012

#### **FEATURES**

- Data Readback Capability for System Self Check

- Fast TTL/CMOS Compatible Data Register

- ±1/2 LSB Max Linearity Error Over the Full Operating Temperature Range

- ±1 LSB Max Gain Error No User Adjustment Required

- Less Than 0.04 LSB Max Zero Scale Error (10nA)

- Single +5V to +15V Supply

- Small 20-Pin 0.3" Wide DIP

- Improved ESD Resistance

- Latch-Up Resistant

- Adds Data Readback Feature to PM-7545 Pinout

- Available in Die Form

# **GENERAL DESCRIPTION**

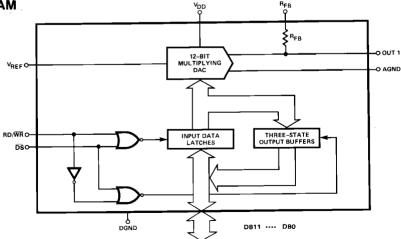

The DAC-8012 is a monolithic 12-bit CMOS multiplying DAC with internal data latches and three-state data readback buffers. The latches and readback buffers perform like a "memory" location. Data loads into the latches as a single 12-bit wide word allowing direct connection to 12-bit and 16-bit busses.

Four-quadrant multiplying capability and 12-bit linearity simplifies wide-bandwidth, low-distortion, digitally-controlled precision attenuator and filter applications.

The powerful data readback function allows users to perform data path verification between the controlling processor and the DAC-8012. System self check results after writing a data word to the DAC-8012, then reading it back to the processor, verifying no change in data takes place. The readback function simplifies the design of automatic test equipment, industrial automation, robotics, and processor-controlled instrumentation. Reduction of software coding results with processors using direct memory execution instructions. In remote systems, data set-points are held in the DAC register which can be interrogated upon system fault recovery.

# ORDERING INFORMATION 1

| RELATIVE<br>ACCURACY | MAXIMUM<br>GAIN ERROR<br>T <sub>A</sub> = +25°C<br>V <sub>DD</sub> = +5V | MILITARY* TEMPERATURE -55°C to +125°C | EXTENDED<br>INDUSTRIAL<br>TEMPERATURE<br>-40°C to +85°C | COMMERCIAL<br>TEMPERATURE<br>0°C to<br>+70°C |

|----------------------|--------------------------------------------------------------------------|---------------------------------------|---------------------------------------------------------|----------------------------------------------|

| ±1/2 LSB             | ±1 LSB                                                                   | DAC8012AR                             | DAC8012ER                                               | DAC8012GP                                    |

| ±1 LSB               | ±3 LSB                                                                   | DAC8012BR                             | DAC8012FR                                               | DAC8012HP                                    |

| ±1 LSB               | ±3 LSB                                                                   | -                                     | DAC8012FP                                               | _                                            |

| ±1 LSB               | ±3 LSB                                                                   |                                       | DAC8012FPC                                              |                                              |

- For devices processed in total compliance to MIL-STD-883, add/883 after part number. Consult factory for 883 data sheet.

- † Burn-in is available on commercial and industrial temperature range parts in CerDIP, plastic DIP, and TO-can packages.

- for availability and burn-in information on SO and PLCC packages, contact your local sales office.

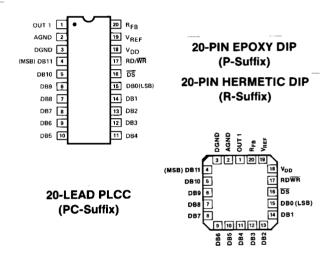

# PIN CONNECTIONS

## **FUNCTIONAL DIAGRAM**

#### REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 Fax: 617/326-8703 Twx: 710/394-6577

Telex: 924491 Cable: ANALOG NORWOODMASS

| ABSOLUTE MAXIMUM RATINGS                                                     |                        |

|------------------------------------------------------------------------------|------------------------|

| (T <sub>A</sub> = +25°C, unless otherwise noted.)<br>V <sub>DD</sub> to DGND |                        |

| V <sub>DD</sub> to DGND                                                      | 0.3V, +17V             |

| Digital Input Voltage to DGND                                                | –0.3V, V <sub>nn</sub> |

| AGND to DGND                                                                 | –0.3, V <sub>DD</sub>  |

| V <sub>DEB</sub> , V <sub>DEE</sub> to DGND                                  | ±25V                   |

| V <sub>PIN 1</sub> to DGND                                                   | 0.3V, V <sub>DD</sub>  |

| Operating Temperature Range                                                  |                        |

| Military (AR, BR) Grades                                                     | 55°C to +125°C         |

| Industrial (ER, FR, FP, FPC) Grades                                          | 40°C to +85°C          |

| Commercial (GP, HP) Grades                                                   | 0°C to +70°C           |

| Junction Temperature                                                         | +150°C                 |

| Storage Temperature                                                          | 65°C to +150°C         |

| Lead Temperature (Soldering, 60 sec)                                         | +300°C                 |

| PACKAGE TYPE            | Θ <sub>jA</sub> (Note 1) | Θ <sub>jc</sub> | UNITS |

|-------------------------|--------------------------|-----------------|-------|

| 20-Pin Hermetic DIP (R) | 76                       | 11              | °C/W  |

| 20-Pin Plastic DIP (P)  | 69                       | 27              | °C/W  |

| 20-Contact PLCC (PC)    | 73                       | 33              | °C/W  |

#### NOTE:

<del>O</del>

<sub>|A</sub> is specified for worst case mounting conditions, i.e., <del>O</del>

<sub>|A</sub> is specified for device in socket for CerDIP and P-DIP packages; <del>O</del>

<sub>|A</sub> is specified for device soldered to printed circuit board for SO package.

#### CAUTION:

- Stresses above those listed under "Absolute Maximum Ratings" may cause

permanent damage to the device. This is a stress rating only and functional

operation at or above this specification is not implied. Exposure to above

maximum rating conditions for extended periods may affect device reliability.

- Do not apply voltages higher than V<sub>DD</sub> or less than GND potential on any terminal except V<sub>REF</sub>.

The digital inputs are zener protected, however, permanent damage may

- The digital inputs are zener protected, however, permanent damage may occur on unprotected units from high-energy electrostatic fields. Keep units in conductive foam at all times until ready to use. Use proper antistatic handling procedures.

- 4. Remove power before inserting or removing units from their sockets.

**ELECTRICAL CHARACTERISTICS** at  $V_{DD}$  = +5V or +15V,  $V_{REF}$  = +10V,  $V_{OUT.1}$  = 0V, AGND = DGND = 0V,  $T_A$  = -55°C to +125°C apply for DAC-8012AR/BR,  $T_A$  = -40°C to +85°C apply for DAC-8012ER/FR/FP/FPC,  $T_A$  = 0°C to +70°C apply for DAC-8012GP/HP, unless otherwise noted.

|                                                                       |                    |                                                                                        | DAC-8012A/E/G |              |                | DAC-8012B/F/H |        | /F/H           |                   |

|-----------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------|---------------|--------------|----------------|---------------|--------|----------------|-------------------|

| PARAMETER                                                             | SYMBOL             | CONDITIONS                                                                             | MIN           | TYP          | MAX            | MIN           | TYP    | MAX            | UNITS             |

| STATIC ACCURACY                                                       |                    |                                                                                        |               |              |                |               |        |                |                   |

| Resolution                                                            |                    |                                                                                        | 12            | _            | _              | 12            | _      |                | Bits              |

| Relative<br>Accuracy                                                  | INL                | T <sub>A</sub> = Full Temp. Range                                                      | _             | _            | ±1/2           | -             | _      | ±1             | LSB               |

| Differential Nonlinearity (Note 1)                                    | DNL                | T <sub>A</sub> = Full Temp. Range                                                      | _             | _            | ±1             | _             | _      | ±1             | LSB               |

| Gain Error<br>(Notes 2, 3)                                            | G <sub>FSE</sub>   | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = Full Temp. Range                            | _             | _            | ±1<br>±2       |               | _<br>_ | ±3<br>±4       | LSB               |

| Gain Temperature<br>Coefficient<br>ΔGain/ΔTemperature<br>(Notes 4, 5) | TCG <sub>FS</sub>  |                                                                                        | _             | _            | ±5             | -             | _      | ±5             | ppm/°C            |

| DC Supply Rejection<br>∆Gain/∆V <sub>DD</sub> (Note 4)                | PSR                | $T_A = +25^{\circ}C$<br>$T_A = Full Temp. Range (\Delta V_{DD} = \pm 5\%)$             | , <u> </u>    | _            | 0.002<br>0.004 |               | _<br>_ | 0.002<br>0.004 | 0/0/0/0           |

| Output Leakage                                                        | ,                  | $T_A = +25$ °C, RD/WR = $\overline{DS}$ = 0V,<br>All Digital Inputs = 0V               | _             | _            | 10             | _             | _      | 10             |                   |

| Current at OUT 1                                                      | I <sub>LKG</sub> — | T <sub>A</sub> = Full Temp. Range<br>A/B Versions<br>E/F/G/H Versions                  | _             | <del>-</del> | 200<br>25      | _<br>_        | _<br>_ | 200<br>25      | — nA              |

| DYNAMIC PERFORMANCE                                                   |                    |                                                                                        |               |              |                |               |        |                |                   |

| Propagation Delay<br>(Notes 4, 6, & 7)                                | t <sub>pD</sub>    | $T_A = +25$ °C (OUT 1 Load = 100Ω, $C_{EXT} = 13$ pF)                                  | _             | _            | 300            | _             | _      | 300            | ns                |

| Current Settling Time<br>(Notes 4, 7)                                 | ts                 | T <sub>A</sub> = Full Temp. Range<br>(To 1/2 LSB)<br>I <sub>OUT 1</sub> Load = 100Ω    | _             | _            | 1              | _             | _      | 1              | μS                |

| Glitch Energy<br>(Note 4)                                             | Q                  | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = Full Temp. Range<br>V <sub>REF</sub> = AGND | _             | _            | 400<br>500     | _<br>_        | _      | 400<br>500     | nVs               |

| AC Feedthrough<br>at I <sub>OUT 1</sub><br>(Note 4)                   | FT                 | $T_A =$ Full Temp. Range $V_{REF} = \pm 10V$ , $f = 10kHz$                             | _             | _            | 5              |               | _      | 5              | mV <sub>p-p</sub> |

| REFERENCE INPUT                                                       |                    |                                                                                        | _             |              |                |               |        |                |                   |

| Input Resistance<br>(Pin 19 to GND)                                   | R <sub>REF</sub>   | T <sub>A</sub> = Full Temp. Range<br>Input Resistance                                  | 7             | 11           | 15             | 7             | 11     | 15             | kΩ                |

**ELECTRICAL CHARACTERISTICS** at  $V_{DD} = +5V$ ,  $V_{REF} = +10V$ ,  $V_{OUT 1} = 0V$ , AGND = DGND = 0V,  $T_A = -55$ °C to +125°C apply for DAC-8012AR/BR,  $T_A = -40$ °C to +85°C apply for DAC-8012ER/FR/FP/FPC,  $T_A = 0$ °C to +70°C apply for DAC-8012GP/HP, unless otherwise noted.

|                                       |                  |                                                             | DAC    | C-8012A/ | E/G | DA  | C-8012B  | /F/H       |       |

|---------------------------------------|------------------|-------------------------------------------------------------|--------|----------|-----|-----|----------|------------|-------|

| PARAMETER                             | SYMBOL           | CONDITIONS                                                  | MIN    | TYP      | MAX | MIN | TYP      | MAX        | UNITS |

| ANALOG OUTPUTS                        |                  |                                                             |        |          | -   |     |          |            |       |

|                                       |                  | V <sub>DD</sub> = +5V or +15V                               |        |          |     |     |          |            |       |

| Output Capacitance                    |                  | T <sub>A</sub> = Full Temp. Range                           |        |          |     |     |          |            |       |

| (Note 4)                              | •                | DB0-DB11 = 0V, RD/ $\overline{WR} = \overline{DS} = 0$      | ov —   | _        | 70  | _   | _        | 70         |       |

| C <sub>OUT 1</sub>                    | C <sub>OUT</sub> | $DB0-DB11 = V_{DD}, RD/\overline{WR} = \overline{DS} =$     | = 0V — | _        | 150 | _   | _        | 150        | pF    |

| DIGITAL INPUTS                        |                  |                                                             |        |          |     |     |          |            |       |

| Input High Voltage                    | VINH             | T - Full Town Bonce                                         | 2.4    | _        | _   | 2.4 | _        | _          | ٧     |

| Input Low Voltage                     | VINL             | T <sub>A</sub> = Full Temp. Range                           | -      | _        | 0.8 | _   | _        | 0.8        | v     |

| Innut Current                         | 1.               | T <sub>A</sub> = +25°C                                      |        | _        | 1   | _   | _        | 1          | μА    |

| Input Current                         | I <sub>IN</sub>  | T <sub>A</sub> = Full Temp. Range                           | _      | _        | 10  | _   |          | 10         | μ^    |

| Input Capacitance                     |                  |                                                             |        |          |     |     |          |            |       |

| DB0-DB11                              | CIN              | T <sub>A</sub> = Full Temp. Range                           | _      | _        | 12  | _   | _        | 12         | рF    |

| RD/WR, DS                             | OIN              | TA Tun tomp. Hange                                          | _      | _        | 6   | -   | -        | 6          | F.    |

| (Note 4)                              |                  |                                                             |        |          |     |     |          |            |       |

| DIGITAL OUTPUTS                       |                  |                                                             |        |          |     |     |          |            |       |

| Output High Voltage                   | V <sub>OH</sub>  | Ι <sub>Ο</sub> = 400μΑ                                      | 4.0    |          |     | 4.0 |          |            | V     |

| Output Low Voltage                    | V <sub>OL</sub>  | I <sub>O</sub> = -1.6mA                                     | _      | _        | 0.4 | -   | _        | 0.4        | ٧     |

| Three-State Output<br>Leakage Current |                  |                                                             | _      | _        | 10  | _   | <u> </u> | 10         | μΑ    |

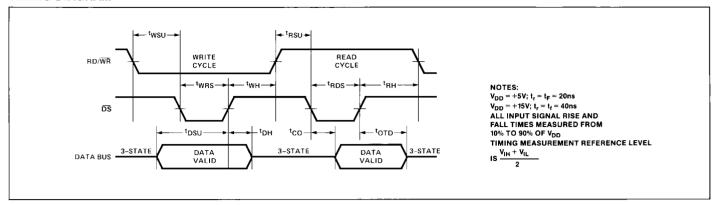

| SWITCHING CHARACTERIS (Note 8)        | STICS            | See Timing Diagram                                          |        |          |     |     |          |            |       |

| Write to Data Strobe                  |                  | T <sub>A</sub> = +25°C                                      | 0      | _        |     | 0   |          | <u> </u>   |       |

| Setup Time                            | t <sub>wsu</sub> | T <sub>A</sub> = Full Temp. Range                           | 0      | _        | _   | 0   | _        | _          | ns    |

| Data Strobe to                        |                  | T <sub>A</sub> = +25°C                                      | 0      | _        | _   | 0   | _        | _          |       |

| Write Hold Time                       | t <sub>WH</sub>  | T <sub>A</sub> = Full Temp. Range                           | 0      | _        | _   | 0   | _        | _          | ns    |

| Read to Data Strobe                   |                  | T <sub>A</sub> = +25°C                                      | 0      | _        |     | 0   | _        | _          |       |

| Setup Time                            | t <sub>RSU</sub> | T <sub>A</sub> = Full Temp. Range                           | 0      | _        | _   | 0   | _        | _          | ns    |

| Data Strobe to                        |                  | T <sub>A</sub> = +25°C                                      | 0      | _        | _   | 0   | _        | _          |       |

| Read Hold Time                        | t <sub>RH</sub>  | T <sub>A</sub> = Full Temp. Range                           | 0      | _        | _   | 0   | _        | _          | ns    |

| Write Mode Data Strobe                |                  | T <sub>A</sub> = +25°C                                      | 180    | _        | _   | 180 | _        | _          |       |

| Width                                 | twrs             | T <sub>A</sub> = Full Temp. Range                           | 250    | _        | _   | 250 | _        | _          | ns    |

| Read Mode Data Strobe                 |                  | T <sub>A</sub> = +25°C                                      | 220    |          | _   | 220 | _        | _          |       |

| Width                                 | t <sub>RDS</sub> | T <sub>A</sub> = Full Temp. Range                           | 290    | _        | _   | 290 | _        | _          | ns    |

| Data Catao Tima                       |                  | T <sub>A</sub> = +25°C                                      | 210    | _        | _   | 210 | _        | _          |       |

| Data Setup Time                       | tosu             | T <sub>A</sub> = Full Temp. Range                           | 250    | _        | _   | 250 | _        | _          | ns    |

|                                       |                  | T <sub>A</sub> = +25°C                                      | 0      | _        |     | 0   |          |            |       |

| Data Hold Time                        | t <sub>DH</sub>  | T <sub>A</sub> = Full Temp. Range                           | 0      | _        | _   | 0   | _        | _          | ns    |

| Data Strobe to                        |                  | T = 1059C                                                   |        |          | 300 |     |          | 300        |       |

| Data Valid Time                       | tco              | T <sub>A</sub> = +25°C                                      | _      | _        | 400 | _   | _        | 300<br>400 | ns    |

| (Notes 4, 9)                          |                  | T <sub>A</sub> = Full Temp. Range                           |        |          |     |     |          |            |       |

| Output Active Time                    |                  | T <sub>A</sub> = +25°C                                      |        |          | 215 | _   |          | 215        |       |

| from Deselection                      | t <sub>OTD</sub> | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = Full Temp. Range | _      | _        | 375 | _   | _        | 375        | ns    |

| (Notes 4, 9)                          | _                |                                                             |        |          |     |     |          | 3,3        |       |

| POWER SUPPLY                          |                  |                                                             |        |          |     |     |          |            |       |

|                                       |                  | T <sub>A</sub> = Full Temp. Range                           |        | _        | 2   | _   | _        | 2          | mA    |

|                                       | IDD              | (All Digital Inputs V <sub>INL</sub> or V <sub>INH</sub> )  | _      | _        | 4   | _   | _        | 2          | mA    |

| Supply Current -                      |                  |                                                             |        |          |     |     |          |            |       |

| • • •                                 |                  | T <sub>A</sub> = Full Temp. Range                           |        | 10       | 100 |     | 10       | 100        | μА    |

**ELECTRICAL CHARACTERISTICS** at  $V_{DD} = \pm 15V$ ,  $V_{REF} = +10V$ ,  $V_{OUT,1} = 0V$ , AGND = DGND = 0V,  $T_A = -55^{\circ}C$  to  $+125^{\circ}C$  apply for DAC-8012AR/BR,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$  apply for DAC-8012ER/FR/FP/FPC,  $T_A = 0^{\circ}C$  to  $+70^{\circ}C$  apply for DAC-8012GP/HP, unless otherwise noted.

| <u> </u>                                          |                                      |                                                                                                 | DAC         | -8012A/  | E/G               | DA         | C-8012B/      | F/H        |       |

|---------------------------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------|-------------|----------|-------------------|------------|---------------|------------|-------|

| PARAMETER                                         | SYMBOL                               | CONDITIONS                                                                                      | MIN         | TYP      | MAX               | MIN        | TYP           | MAX        | UNITS |

| DIGITAL INPUTS                                    |                                      |                                                                                                 |             |          |                   |            |               |            |       |

| Input High Voltage<br>Input Low Voltage           | V <sub>INH</sub><br>V <sub>INL</sub> | T <sub>A</sub> = Full Temp. Range                                                               | 13.5<br>—   | _        | <br>1.5           | 13.5<br>—  |               | —<br>1.5   | V     |

| Input Current                                     | I <sub>IN</sub>                      | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = Full Temp. Range                                     |             | _<br>_   | 1<br>10           | _          |               | 1<br>10    | μΑ    |

| Input Capacitance DB0-DB11 RD/WR, DS (Note 4)     | C <sub>IN</sub>                      | T <sub>A</sub> = Full Temp. Range                                                               | _           | _<br>_   | 12<br>10          | -          | _             | 12<br>10   | pF    |

| DIGITAL OUTPUTS                                   |                                      |                                                                                                 |             |          |                   |            |               |            |       |

| Output High Voltage                               | V <sub>OH</sub>                      | $I_O = 3mA$                                                                                     | 13.5        | _        | _                 | 13.5       | _             |            | V     |

| Output Low Voltage                                | V <sub>OL</sub>                      | I <sub>O</sub> = -3mA                                                                           | _           | _        | 1.5               |            |               | 1.5        | V     |

| Three-State Output<br>Leakage Current             |                                      |                                                                                                 |             | -        | 10                | _          |               | 10         | μΑ    |

| SWITCHING CHARACTERI<br>(Note 8)                  | STICS                                | See Timing Diagram                                                                              |             |          |                   |            |               |            |       |

| Write to Data Strobe<br>Setup Time                | t <sub>wsu</sub>                     | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = Full Temp. Range                                     | 0           | _        |                   | 0          | _<br>_        |            | ns    |

| Data Strobe to<br>Write Hold Time                 | t <sub>WH</sub>                      | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = Full Temp. Range                                     | 0           |          | _<br>             | 0          |               |            | ns    |

| Read to Data Strobe<br>Setup Time                 | t <sub>RSU</sub>                     | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = Full Temp. Range                                     | 0           | <u> </u> |                   | 0<br>0     | _             |            | ns    |

| Data Strobe to<br>Read Hold Time                  | t <sub>RH</sub>                      | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = Full Temp. Range                                     | 0           |          | <u> </u>          | 0          |               |            | ns    |

| Write Mode Data Strobe<br>Width                   | t <sub>was</sub>                     | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = Full Temp. Range                                     | 100<br>120  | <u>-</u> |                   | 100<br>120 |               | _          | ns    |

| Read Mode Data Strobe<br>Width                    | t <sub>RDS</sub>                     | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = Full Temp. Range                                     | 110<br>150  | _<br>    |                   | 110<br>150 |               | _          | ns    |

| Data Setup Time                                   | t <sub>DSU</sub>                     | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = Full Temp. Range                                     | 90<br>120   |          |                   | 90<br>120  |               |            | ns    |

| Data Hold Time                                    | t <sub>DH</sub>                      | $T_A = +25$ °C<br>$T_A = Full Temp. Range$                                                      | 0           |          | <del>-</del><br>- | 0          |               |            | ns    |

| Data Strobe to<br>Output Valid Time<br>(Note 9)   | tco                                  | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = Full Temp. Range                                     | <u>-</u>    | -        | 180<br>220        | _<br>      | <u>-</u><br>- | 180<br>220 | ns    |

| Output Active Time<br>for Deselection<br>(Note 9) | t <sub>ОТР</sub>                     | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = Full Temp. Range                                     | _           |          | 180<br>250        | <u>-</u>   | _<br>_        | 180<br>250 | ns    |

| POWER SUPPLY                                      |                                      |                                                                                                 | · · · · · · |          |                   |            |               |            |       |

| Committee Course - 1                              | IDD                                  | T <sub>A</sub> = Full Temp. Range<br>(All Digital Inputs V <sub>INL</sub> or V <sub>INH</sub> ) | _           | _        | 2                 | _          | _             | 2          | mA    |

| Supply Current                                    | I <sub>DD</sub>                      | T <sub>A</sub> = Full Temp. Range<br>(All Digital Inputs 0V or V <sub>DD</sub> )                | _           | 10       | 100               |            | 10            | 100        | μΑ    |

## NOTES:

- 1. 12-bit monotonic over full temperature range.

- 2. Includes the effects of 5ppm max. gain T.C.

- 3. Using internal R<sub>FB</sub>. DAC register loaded with 1111 1111 1111. Gain error is adjustable using the circuits of Figures 4 and 5.

- 4. GUARANTEED but NOT TESTED.

- 5. Typical value is 2ppm/°C for  $V_{DD} = +5V$ .

- 6. From digital input change to 90% of final analog output.

- 7. All digital inputs = 0V to  $V_{DD}$ ; or  $V_{DD}$  to 0V.

- 8. Sample tested at +25°C to ensure compliance.

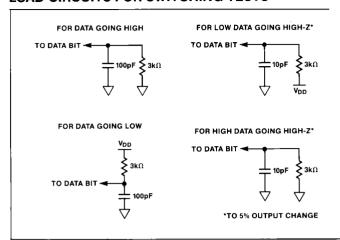

- 9. See load circuits for switching tests.

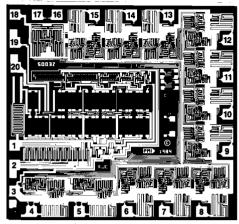

# **DICE CHARACTERISTICS**

1. OUT 1 11. DB4 2. AGND 12. DB3 3. DGND 13. DB2 4. DB11 (MSB) 14. DB1 5. DB10 15. DB0 (LSB) 6. DB9 16. DS 7. DB8 17. RD/WR 8. DB7 18. V<sub>DD</sub> 9. DB6 19. V<sub>REF</sub> 10. DB5 20. R<sub>FB</sub>

DIE SIZE  $0.121 \times 0.112$  inch, 13,552 sq. mils (3.07  $\times$  2.85 mm, 8.75 sq. mm)

**WAFER TEST LIMITS** at  $V_{DD} = +5V$  or +15V,  $V_{REF} = +10V$ ,  $V_{OUT 1} = 0V$ , AGND = DGND = 0V,  $T_A = 25$ °C, unless otherwise noted.

|                                                  |                  |                                                                                                     | DAC-8012G   | <u>.</u> .        |

|--------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------|-------------|-------------------|

| PARAMETER                                        | SYMBOL           | CONDITIONS                                                                                          | LIMIT       | UNITS             |

| Relative Accuracy                                | INL              | Endpoint Linearity Error                                                                            | ±1/2        | LSB MAX           |

| Differential Nonlinearity                        | DNL              |                                                                                                     | ±1          | LSB MAX           |

| Gain Error                                       | G <sub>FSE</sub> | DAC Latches Loaded with 1111 1111 1111                                                              | ±3          | LSB MAX           |

| Output Leakage                                   | lkG              | DAC Latches Loaded with 0000 0000 0000<br>Pad 1                                                     | ±10         | nA MAX            |

| Input Resistance                                 | R <sub>REF</sub> | Pad 19                                                                                              | 6/15        | kΩ MIN/<br>kΩ MAX |

| Output High Voltage                              | V <sub>OH</sub>  | $V_{DD} = 5V, I_{O} = 400 \mu A$                                                                    | 4.0         | V MIN             |

| Output Low Voltage                               | V <sub>OL</sub>  | V <sub>DD</sub> = 5V, I <sub>O</sub> = -1.6mA                                                       | 0.4         | V MAX             |

| Digital Input<br>Hìgh                            | V <sub>INH</sub> | $V_{DD} = 5V$ $V_{DD} = 15V$                                                                        | 2.4<br>13.5 | V MIN             |

| Digital Input<br>Low                             | V <sub>INL</sub> | $V_{DD} = 5V$ $V_{DD} = 15V$                                                                        | 0.8<br>1.5  | V MAX             |

| Input Current                                    | $1_{IN}$         | V <sub>IN</sub> = 0V or V <sub>DD</sub>                                                             | ±1          | μΑ MAX            |

| Supply Current                                   | IDD              | All Digital Inputs V <sub>INL</sub> or V <sub>INH</sub><br>All Digital Inputs 0V or V <sub>DD</sub> | 2<br>0.1    | mA MAX            |

| DC Supply Rejection<br>(AGain/AV <sub>DD</sub> ) | PSRR             | V <sub>DD</sub> = ±5%                                                                               | 0.004       | %/% MAX           |

#### NOTE

Electrical tests are performed at wafer probe to the limits shown. Due to variations in assembly methods and normal yield loss, yield after packaging is not guaranteed for standard product dice. Consult factory to negotiate specifications based on dice lot qualification through sample lot assembly and testing.

# $\textbf{TYPICAL ELECTRICAL CHARACTERISTICS} \text{ at V}_{DD} = +5 \text{V or} + 15 \text{V}, \text{V}_{REF} = +10 \text{V}, \text{V}_{OUT\,1} = 0 \text{V}; \text{T}_{A} = 25^{\circ}\text{C}, \text{unless otherwise noted}.$

| PARAMETER                 | SYMBOL             | CONDITIONS                             | DAC-8012G<br>TYPICAL | UNITS |

|---------------------------|--------------------|----------------------------------------|----------------------|-------|

| Digital Input Capacitance | C <sub>IN</sub>    |                                        | 12                   | pF    |

| Output Canaditana         | C <sub>OUT 1</sub> | DAC Latches Loaded with 0000 0000 0000 | 70                   | pF    |

| Output Capacitance        | C <sub>OUT 1</sub> | DAC Latches Loaded with 1111 1111 1111 | 150                  | pF    |

| Propagation Delay         | t <sub>pD</sub>    | $V_{DD} = 15V$ $V_{DD} = 5V$           | 300                  | ns    |

# LOAD CIRCUITS FOR SWITCHING TESTS

# PARAMETER DEFINITIONS

#### **RELATIVE ACCURACY**

Sometimes referred to as endpoint nonlinearity, and is a measure of the maximum deviation from a straight line passing through the endpoints of the DAC transfer function. Relative Accuracy is measured after the zero and full-scale points have been adjusted, and is normally expressed in LSB or as a percentage of full scale.

# **DIFFERENTIAL NONLINEARITY**

This is the difference between the measured change and the ideal change between any two adjacent codes. A differential nonlinearity of  $\pm 1$  LSB maximum over the full operating temperature range will ensure that a device is monotonic (the output will not decrease for an increase in digital code applied).

# **GAIN ERROR**

Gain or full scale error is the amount of output error between the ideal output and the actual output. The ideal output is  $V_{REF}$  minus 1 LSB. The gain error is adjustable to zero using external resistance.

#### **OUTPUT CAPACITANCE**

The capacitance from OUT1 to AGND.

## **PROPAGATION DELAY**

This is measured from the digital input change to the analog output current reaching 90% of its final value.

# FEEDTHROUGH GLITCH ENERGY

This is a measure of the amount of charge injected to the analog output from the digital inputs, when the digital inputs change states. It is the area of the glitch and is specified in nVsec; it is measured with  $V_{REF}$  = AGND.

## LOGIC INFORMATION

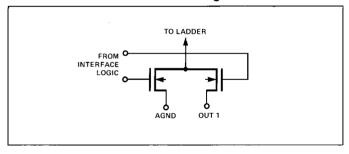

#### D/A CONVERTER SECTION

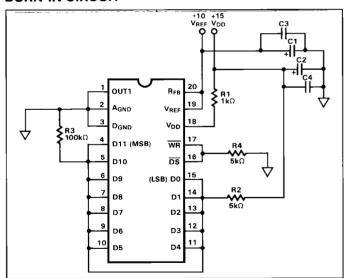

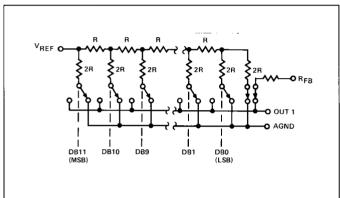

Figure 1 shows a simplified circuit of the D/A Converter section of the DAC-8012, and Figure 2 gives an approximate equivalent switch circuit. R is typically  $11k\Omega$ .

The binary-weighted currents are switched between OUT 1 and AGND by N-channel switches, thus maintaining a constant current in each ladder leg independent of the switch state.

The capacitance at the OUT 1 terminal,  $C_{OUT\ 1}$ , is code dependent and varies from 70pF (all switches to AGND) to 150pF (all switches to OUT 1). One of the current switches is shown in Figure 2.

The input resistance at  $V_{REF}$  (Figure 1) is always equal to  $R_{LDR}$  ( $R_{LDR}$  is the R/2R ladder characteristics resistance and is equal to value "R"). Since the input resistance at the  $V_{REF}$  pin is constant, the reference terminal can be driven by a reference voltage or a reference current, ac or dc, of positive or negative polarity. (If a current source is used, a low-temperature-coefficient external  $R_{FB}$  is recommended to define scale factor.)

The internal feedback resistor (R<sub>FB</sub>) has a normally closed switch in series as shown in Figure 1. This switch improves performance over temperature and power supply rejection; however, when the circuit is not powered up the switch assumes an open state.

## **BURN-IN CIRCUIT**

## **TIMING DIAGRAM**

FIGURE 1: Simplified D/A Circuit of DAC-8012

FIGURE 2: N-Channel Current Steering Switch

## **DIGITAL SECTION**

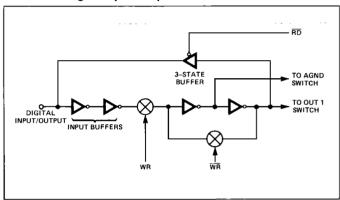

Figure 3 shows the digital I/O structure for one bit. When the data strobe ( $\overline{DS}$ ) and the RD/WR lines are held low, data at the digital input is fed through the input buffers and the data latches which control the DAC current output switches are transparent. Data is latched when either  $\overline{DS}$  or RD/WR go high. When the data strobe  $\overline{DS}$  is held low and the RD/WR line is held high, the three-state buffer becomes active and the data from the latches is

FIGURE 3: Digital Input/Output Structure

fed through the three-state buffers to the digital input/output lines. This is known as the Read Cycle, or data readback.

The input buffers are simple CMOS inverters designed such that when the DAC-8012 is operated with  $V_{DD}$  = +5V, the buffers convert TTL input levels (2.4V and 0.8V) into CMOS logic levels. When the digital input is in the region of 1.0V to 3.0V, the input buffers operate in their linear region and draw current from the power supply. To minimize power supply currents, it is recommended that the digital input voltages be as close to the supply rails ( $V_{DD}$  and  $D_{GND}$ ) as is practically possible. The DAC-8012 may be operated with any supply voltage in the range  $5V \leq V_{DD} \leq 15V$ . With  $V_{DD}$  =+15V, the input logic levels are CMOS compatible only, i.e., 1.5V and 13.5V.

The three-state output buffers, in the active mode, provide TTL-compatible digital outputs with a fan-out of one TTL load when the DAC-8012 is operated with +5V power supply. When powered from +15V, the output buffers provide output logic levels of 1.5V and 13.5V. Three-state output leakage is typically 10nA.

REV. A \_\_7\_

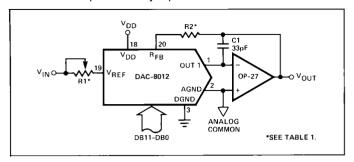

FIGURE 4: Unipolar Binary Operation

**BASIC APPLICATIONS**

Figures 4 and 5 show simple unipolar and bipolar circuits using the DAC-8012. Resistor R1 is used to trim for full scale. The following versions: DAC-8012AR, DAC-8012ER, DAC-8012GP, have a guaranteed maximum gain error of  $\pm 1$  LSB at +25°C and  $V_{DD}$  = +5V, and in many applications the gain trim resistors are not required. Capacitor C1 provides phase compensation and helps prevent overshoot and ringing when using high speed op amps. The circuits of Figures 4 and 5 have constant input impedance at the  $V_{\rm RFF}$  terminal.

The circuit of Figure 4 can either be used as a fixed reference D/A converter so that it provides an analog output voltage in the range 0 to  $-V_{IN}$  (the inversion is introduced by the op amp); or  $V_{IN}$  can be an ac signal in which case the circuit behaves as an attenuator (2-Quadrant Multiplier).  $V_{IN}$  can be any voltage in the range  $-20V \le V_{IN} \le +20V$  (provided the op amp can handle such voltages) since  $V_{REF}$  is permitted to exceed  $V_{DD}$ . Table II shows the code relationship for the circuit of Figure 4.

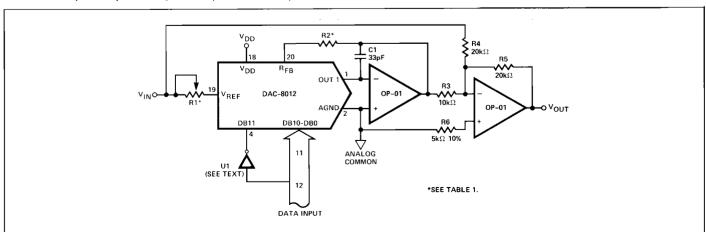

Figure 5 and Table III illustrate the recommended circuit and code relationship for bipolar operation. The D/A function itself uses offset binary code, and inverter  $U_1$  on the MSB line, converts 2's-complement input code to offset binary code. The inverter  $U_1$  may be omitted if the inversion is done in software, using an exclusive OR instruction.

R3, R4 and R5 must match within 0.01% and should be the same type of resistors (preferably wire-wound or metal foil), so that their temperature coefficients match. Mismatch of R3 value to R4 causes both offset and full scale error. Mismatch of R5 to R4 and R3 causes full scale error.

TABLE I: Recommended Trim Resistor Value vs. Grades

| HP/FR/BR | GP/ER/AR |

|----------|----------|

| 100Ω     | 20Ω      |

| 33Ω      | 6.8Ω     |

|          | 100Ω     |

TABLE II: Unipolar Binary Code Table for Circuit of Figure 4

|      | RY NUMB<br>C REGIST |      | ANALOG OUTPUT                                                          |

|------|---------------------|------|------------------------------------------------------------------------|

| 1111 | 1111                | 1111 | $-V_{IN} \cdot \left(\begin{array}{c} 4095 \\ 4096 \end{array}\right)$ |

| 1000 | 0000                | 0000 | $-V_{IN} \cdot \left(\frac{2048}{4096}\right) = -1/2 V_{IN}$           |

| 0000 | 0000                | 0001 | $-V_{IN} \cdot \left(\frac{1}{4096}\right)$                            |

| 0000 | 0000                | 0000 | 0 Volts                                                                |

TABLE III: 2's Complement Code Table for Circuit of Figure 5

|      | DATA INPU | Т    | ANALOG OUTPUT                                  |  |  |  |  |  |

|------|-----------|------|------------------------------------------------|--|--|--|--|--|

| 0111 | 1111      | 1111 | $+V_{IN} \cdot \left(\frac{2047}{2048}\right)$ |  |  |  |  |  |

| 0000 | 0000      | 0001 | $+V_{IN} \cdot \left(\frac{1}{2048}\right)$    |  |  |  |  |  |

| 0000 | 0000      | 0000 | 0 Volts                                        |  |  |  |  |  |

| 1111 | 1111      | 1111 | $-V_{1N} \cdot \left(\frac{1}{2048}\right)$    |  |  |  |  |  |

| 1000 | 0000      | 0000 | $-V_{1N} \cdot \left(\frac{2048}{2048}\right)$ |  |  |  |  |  |

|      |           |      |                                                |  |  |  |  |  |

FIGURE 5: Bipolar Operation (2's Complement Code)

## **APPLICATIONS HINTS**

**Output Offset:** CMOS D/A converters exhibit a code-dependent output resistance that causes a code-dependent error voltage at the output of the amplifier. The maximum amplitude of this offset, which adds to the D/A converter nonlinearity, is 0.67  $V_{OS}$  where  $V_{OS}$  is the amplifier input-offset voltage. To maintain monotonic operation, it is recommended that  $V_{OS}$  be no greater than 10% of 1 LSB over the temperature range of operation.

General Ground Management: AC or transient voltages between AGND and DGND can cause noise injection into the analog output. The simplest method of ensuring that voltages at AGND and DGND are equal is to tie AGND and DGND together at the DAC-8012. It is recommended that two diodes (1N914 or equivalent) be connected in inverse parallel between AGND and DGND pins in complex systems where AGND and DGND tie on the backplane.

**Digital Glitches:** When RD/ $\overline{WR}$  and  $\overline{DS}$  are both low, the latches are transparent and the D/A converter inputs follow the data inputs. Some bus systems do not always have data valid for the whole period during which RD/ $\overline{WR}$  is low. This will allow invalid data to briefly appear at the DAC inputs during the write cycle. This can cause unwanted glitches at the DAC output. Retiming the write pulse RD/ $\overline{WR}$ , so that it only occurs when data is valid, will eliminate the problem.

# INTERFACING THE DAC-8012 TO MICROPROCESSORS

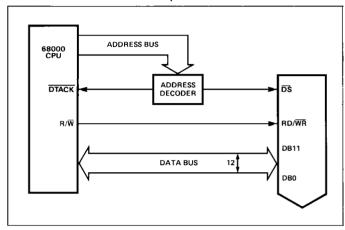

Figure 6 shows the interface configuration for the 68000 16-bit microprocessor. No external logic is required to write data into the DAC or to readback data from the DAC-8012 latches. Analog circuitry has been removed for clarity.

FIGURE 6: 68000 16-Bit Microprocessor to DAC-8012 Interface

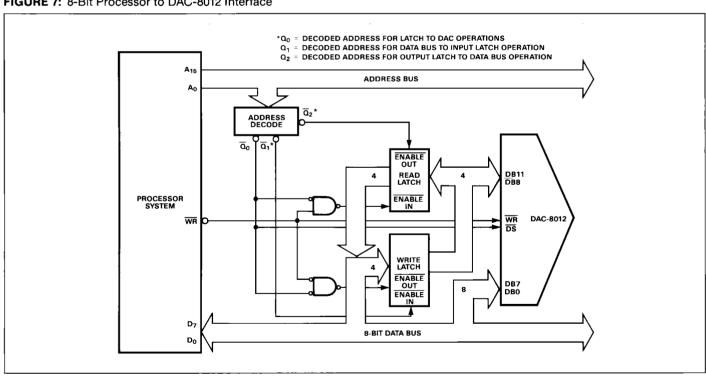

FIGURE 7: 8-Bit Processor to DAC-8012 Interface