# TMS38021 PROTOCOL HANDLER

NOVEMBER 1986

- Compatible with IEEE Std 802.5-1985

Token Ring Access Method and Physical Layer Specifications

- Differential Manchester Code Conversion on 4M-Bit per Second Serial Data Stream

- Address Recognition (Functional, Group and Specific)

- Manchester Code Violation Detection

- Starting and Ending Delimiter Generation and Detection

- CRC Generation and Checking

- High-Speed Frame Repeat Path Minimizes Ring Latency (2-Bit Times)

- Token Transmit and Priority Control

- Monitor Functions

- Separate Pairs of DMA Channels for Receive and Transmit

- Supports Both Universal and Local Ring Addressing

- Automatic Frame Buffer Management

- External Hardware Interface for User-Defined External Checker Logic

- On-Chip 16K-Byte ROM for Adapter Software

- 8K x 18-Bit ROM with Byte Parity Protection

- Single Word Prefetch

- Plug Compatible with the TMS38020

- Test Pin for Hi-Z, Module-in-Place Testing

- 48-Pin, 600-Mil, Ceramic Dual-in-Line Packaging

- Low-Power Scaled-NMOS Technology

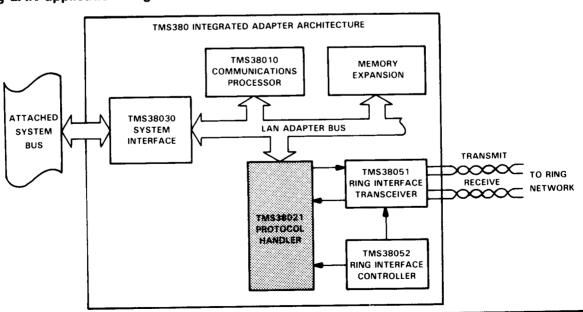

# token ring LAN application diagram

ADVANCE INFORMATION documents contain information on new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

Copyright © 1986, Texas Instruments Incorporated

# TMS38021 PROTOCOL HANDLER

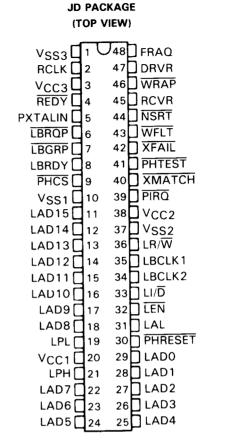

# pin descriptions

| NAME            | I/O | DESCRIPTION                                                                             |  |  |

|-----------------|-----|-----------------------------------------------------------------------------------------|--|--|

|                 |     | LAN ADAPTER BUS INTERFACE PINS                                                          |  |  |

| LBCLK1, LBCLK2  | 1   | Bus Clocks                                                                              |  |  |

| LAL             | 1/0 | Address Latch Enable                                                                    |  |  |

| TÉN             | 1/0 | Data Enable                                                                             |  |  |

| LBRDY           | 1/0 | Bus Ready                                                                               |  |  |

| PIRO            | 0   | PH Interrupt Request                                                                    |  |  |

| LBROP           | 0   | Bus Request                                                                             |  |  |

| LBGRP           | 1 1 | Bus Grant                                                                               |  |  |

| LAD0-LAD15      | 1/0 | Address/Data bus. LADO is the most-significant bit, LAD15 is the least-significant bit. |  |  |

| LPH, LPL        | 1/0 | Parity High/Parity Low                                                                  |  |  |

| LI/D            | 1/0 | Instruction/Data Bus Status Code                                                        |  |  |

| LR/W            | 1/0 | Read/Not Write                                                                          |  |  |

| PHRESET         | 1 1 | Reset                                                                                   |  |  |

| PHCS            |     | Chip Select                                                                             |  |  |

|                 |     | RING INTERFACE PINS                                                                     |  |  |

| DRVR            | 0   | Transmitter Data                                                                        |  |  |

| FRAQ            | 0   | Frequency Acquisition Select                                                            |  |  |

| NSRT            | 0   | Insert Control                                                                          |  |  |

| RCLK            |     | Recovered Data Clock                                                                    |  |  |

| RCVR            |     | Received Data                                                                           |  |  |

| REDY            |     | Ring Interface Ready                                                                    |  |  |

| WFLT            |     | Wire Fault Detect                                                                       |  |  |

| WRAP            | 0   | Wrap Select                                                                             |  |  |

| PXTALIN         | 1   | Ring Frequency Reference Clock                                                          |  |  |

|                 |     | MISCELLANEOUS PINS                                                                      |  |  |

| PHTEST          | 1   | Module-in-Place Test Mode Select. This pin should be left unconnected.                  |  |  |

| Vcc             | ]   | 5-V supply pins.                                                                        |  |  |

| V <sub>SS</sub> |     | Ground pins.                                                                            |  |  |

| XMATCH          | 1/0 | External frame match select.                                                            |  |  |

| XFAIL           | 1/0 | External frame fail select.                                                             |  |  |

### description

The TMS38021 Protocol Handler integrates onto a single chip the hardware-based protocol functions for a 4 megabit per second token ring Local Area Network (LAN). An on-chip ROM contains 16K bytes of software used by the TMS38010 Communications Processor for implementation of a complete token ring Adapter function. The TMS38021 provides Differential Manchester encoding and decoding, frame address recognition, and includes state machine functions which capture free tokens, transmit and receive frames, manage the Adapter RAM buffers and provide token transmit and priority controls. Four DMA channels, two for transmit and two for receive, insure high-speed transfer of frames between the Adapter's buffer RAM and the ring. Integrity of transmitted and received data is provided by CRC generation and checking, detection of Differential Manchester code violations, and parity on internal data paths and at the LAN Adapter bus interface.

The TMS38021 is pin-compatible with the TMS38020. The TMS38021 defines two pins which were not used on the TMS38020, the XMATCH (pin 40) and XFAIL (pin 42) pins. These pins allow user-defined external hardware to be implemented which can provide a frame copy/frame not copy decision on all receive frames in parallel with the normal address compare capabilities of the TMS38021. Using these pins, the designer can implement extensions to the normal address recognition capability of the TMS38021 for such applications as source routing bridges.

The TMS38021 also differs from the TMS38020 in that both universal and local ring station specific addresses are supported. Thus, bit 1 of byte 0 of the specific address register high (SAH) may be set to either a one or a zero.

The TMS38021, when coupled with the TMS38010 Communications Processor, the TMS38030 System Interface, and the TMS38051 and TMS38052 Ring Interface chips, forms a highly integrated token ring LAN Adapter.

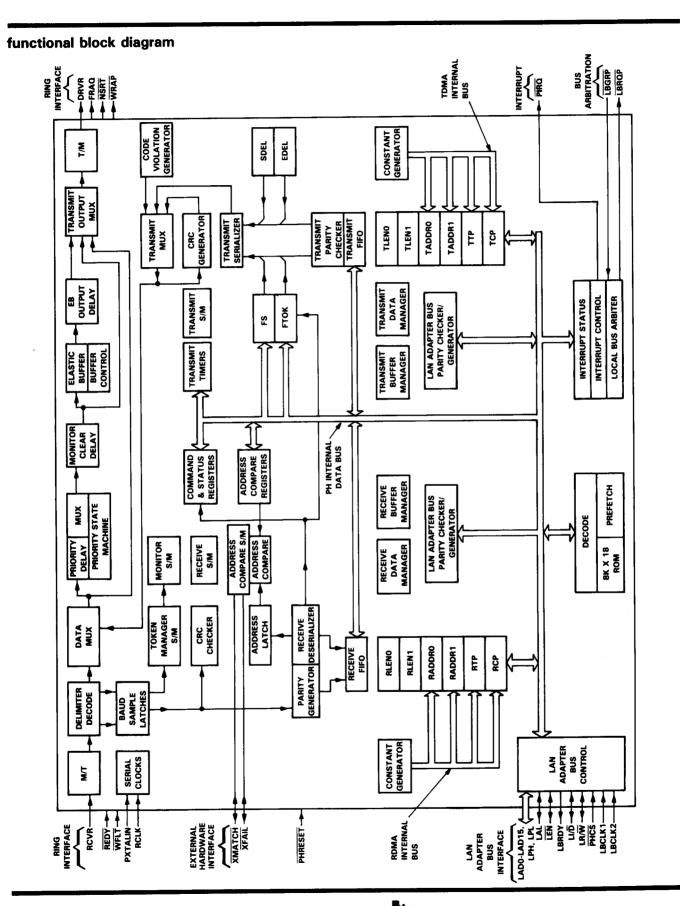

#### architecture

The TMS38021 Protocol Handler contains a bus master interface to the LAN Adapter bus for transfer of frame data between itself and LAN Adapter bus memory, a bus slave interface to the LAN Adapter bus for control by an external CPU, an interface to the Ring Interface circuit, and a 16K-byte ROM. Internal to the TMS38021 are several finite-state machine-implemented functions which provide bit-and frame-level processing of token protocols as well as control the flow of DMA data to and from buffer RAM resident on the LAN Adapter bus. The following paragraphs describe the blocks shown in the functional block diagram.

### address compare state machine

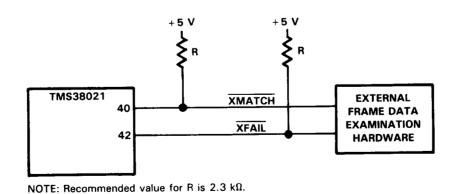

The address compare state machine controls the recognition of addresses in a received frame (including stripped frames). In addition to normal frame address recognition capabilities, the TMS38021 provides an External Copy Hardware Option (ECHO) interface which provides a medium for the TMS38021 to signal to external hardware the presence of receive data on the LAN Adapter bus, and for external hardware to signal the results of its data check, selecting to copy or not to copy the frame. The External Copy Hardware Option (ECHO) interface is implemented via two pins on the TMS38021: the XMATCH pin and the XFAIL pin. The electrical and switching characteristics of these pins are described in the electrical specifications. A description of the ECHO Interface may be found below. A description of frame addressing methodology may be found in the Communications Services section of the User's Guide.

#### external copy hardware option (ECHO)

The external copy hardware interface consists of the XMATCH and XFAIL pins and makes use of the recoverable buffering technique used by the TMS38021. The TMS38021 writes a frame to memory while it is checking the address of the frame, and then recovers the buffer if the frame is not to be copied. Thus, the frame data is available to external hardware on the LAN Adapter bus for capture and examination.

In order to let the external hardware know which bus cycles carry data, the TMS38021 indicates the first data transfer of a frame. Following cycles are "traced" in the manner described below. The "pass," "fail," and "first-data" signals share the same two TMS38021 pins.

The first data transfer of a frame (AC/FC bytes) is indicated to the external logic by both the XMATCH and XFAIL pins being driven low by the TMS38021 (see Table 1). The external hardware must latch the address of this transfer so that succeeding receive DMA cycles may be traced. Data is stored sequentially into memory, so incrementing this latched address gives the address of the next data write. By comparing this new address to the address/data bus, the transfer of the next word of the frame can be recognized. The latch is incremented again, and the process continues until completion of the external check.

Until both the internal address check and some indication from the external hardware is received, the TMS38021 does not know whether to accept or reject the frame. It cannot assume that the external hardware timing is the same as its own. So the TMS38021 must buffer data until explicitly signalled that the external check has been completed. This is indicated by either the  $\overline{XMATCH}$  or  $\overline{XFAIL}$  pin being driven low by external hardware to indicate that the frame should be copied or not be copied respectively. The TMS38021 will not chain past the first buffer it is given. Therefore, the external hardware must give some indication at least four bytes before the end of the first buffer.

| <b>XMATCH</b> | XFAIL | FUNCTION                                                                                                                    |

|---------------|-------|-----------------------------------------------------------------------------------------------------------------------------|

| Hi            | Hi    | Default state of the interface                                                                                              |

| Lo            | Lo    | Asserted by TMS38021 to indicate start of frame and that the AC/FC word of the frame will be transferred on this bus cycle. |

| Lo            | Hi    | Asserted by the external hardware to indicate it has completed its frame check and that the frame should be copied.         |

| Hi            | Lo    | Asserted by the external hardware to indicate it has completed its frame check and the check failed.                        |

TABLE 1. XMATCH, XFAIL PIN FUNCTIONS

Figure 1 illustrates the TMS38021 connection to external hardware. The interface consists of two wire-AND signal lines XMATCH and XFAIL. External pullups are required as these signals are only driven low.

FIGURE 1. EXTERNAL COPY HARDWARE INTERFACE

As the buffer recovery decision is delayed until both the internal address checker and the external hardware check are complete, the external hardware must finish its check in time to allow the buffer to be recovered. Therefore, the result of an external check should be posted by the time of the transfer of the frame word which is two words before the end of the frame.

The TMS38021 has internal pulldowns on XMATCH and XFAIL. However, the XFAIL indication takes precedence over the XMATCH indication. Thus, if no external hardware is present, the TMS38021 will copy frames based only upon its internal address compare. This allows the TMS38021 to plug into existing TMS38020 sockets.

Externally matched frames will not be copied when the ROPT bits of the RINGCMD1 register are set to "COPY ONLY EXPRESS BUFFERS". The ARI bits will be set however if a external match is indicated.

Under normal adapter operation there may be times when the TMS38021 has no buffer available for copying a frame, so data cannot be written to memory, and its transfer monitored by the external hardware. Therefore, data must be given directly to the external hardware so that the Address Recognized bits (ARI) of the frame can be correctly set.

The TMS38021 does this by writing frame data to address >0200 on the LAN Adapter bus whenever there is no buffer available. Data will be written to >0200 until the external hardware checker signals its results.

#### **CRC** checker

This block contains a 32-bit feedback shift register for calculation of the cyclic redundancy code of frames received. The TMS38021 calculates the CRC for each frame that the TMS38021 receives. If the calculated CRC does not agree with the CRC value of the received frame, the TMS38021 sets an error indicator bit within the frame to flag the occurrence of the error. If the TMS38021 was copying the frame at the time the CRC error was detected (due to an address match), the TMS38021 notifies the LAN Adapter CPU of the error. Mathematically, the CRC is calculated by considering the checked bytes as a polynomial and dividing it modulo 2 by the following polynomial:

$$G(X) = X^{32} + X^{26} + X^{23} + X^{22} + X^{16} + X^{12} + X^{11} + X^{10} + X^{8} + X^{7} + X^{5} + X^{4} + X^{2} + X^{1} + 1$$

#### **CRC** generator

The cyclic redundancy code (CRC) generator generates the CRC field to be inserted by the TMS38021 when transmitting. The procedure for generating CRC is identical to that described for the CRC checker.

### data multiplexer

The data multiplexer selects the source of the data to be transmitted. The source may be received ring data (repeat mode), a constant of zeros (idles), or data to be transmitted by the TMS38021.

#### delimiter decode

This block detects the Start Delimiter (SDEL) and End Delimiter (EDEL) sequences defined for the protocol.

#### elastic buffer

The elastic buffer absorbs the accumulated phase jitter in the ring. During normal operation, only one station (the Active Monitor) inserts its elastic buffer on the ring. As the accumulated phase delay around the ring varies, it is "absorbed" by the elastic buffer. The elastic buffer can absorb  $\pm$  3 bits of accumulated jitter.

The total delay through the elastic buffer is 3  $\pm$  3 bits. When the elastic buffer is not inserted on the ring, it permits the TMS38021 to detect when the incoming data frequency falls outside acceptable bounds by detecting overrun and underrun conditions.

The overrun and underrun conditions are defined to occur within a specific number of bit times. To minimize the possibility of overrun and underrun over longer periods of time, the PH re-initializes the elastic buffer every 512 bit times when in standby monitor mode and whenever the PH detects a token when in active monitor mode.

### fire token register (FTOK)

The fire token register is used to hold the access control (AC) field that will be used in transmitting a token on the ring.

### interrupt status logic

The interrupt status logic contains a register with information concerning TMS38021 interrupts. This logic provides interrupt vectoring, masking, and prioritization.

### LAN Adapter bus parity checker

The LAN Adapter bus parity checker checks all data placed on the internal TMS38021 data bus from the LAN Adapter bus. This includes data written to the TMS38021 by an external bus master, data read by the TMS38021 receive or transmit buffer manager, and data read by the TMS38021 transmit DMA unit for transmission on the ring.

### LAN Adapter bus parity generator

The parity generator generates the parity to be placed on the LAN Adapter bus when any TMS38021 register is read by an external bus master. However, received data which has parity generated by the serial parity generator has no parity generated by the bus parity generator.

### manchester-to-transitional decoder (M/T)

This functional block converts the Differential Manchester code received from th ring into an internal format called "transitional" code. Transitional code is so named because baud are encoded based upon their transition from the previous baud. The receive data sampled on pin RCVR is sampled by the recovered data clock input on pin RCLK.

#### monitor delay

The token ring protocol calls for a ring function called an Active Monitor. Each ring will have one Active Monitor which is chosen during a contention process. One function of an Active Monitor is to introduce enough delay in a ring to provide a minimum length ring sufficient to circulate a free token. When the TMS38021 is configured as an Active Monitor [the CXMT bit of the Ring Command 1 (RINGCMD1) register is set], it inserts additional monitor delay to meet the effective ring length requirement. The monitor delay consists of a 7.5-baud (half-bit times) delay preceding the elastic buffer and a 22.5-baud delay succeeding it. The total delay through the TMS38021 when the Active Monitor mode is selected is 4-baud normal delay plus 19-baud for the priority delay plus 30-baud for the monitor delay plus 6-baud average elastic buffer delay. This delay totals  $59 \pm 6$  baud.

#### monitor state machine

The monitor state machine controls the setting of the Monitor Count bit of busy or priority tokens which are repeated on the ring and the detection of token activity on the ring. This state machine is active when the TMS38021 is configured as an Active Monitor [MON bit of Ring Command 1 Register (RINGCMD1) is set].

<sup>†</sup>Two baud equals one bit of Differential Manchester encoding.

#### priority delay and state machine

The TMS38021 provides control of seven levels of token priority. The priority state machine is responsible for controlling the token priority as defined by the protocol. The priority delay of 19 half-bit times is inserted when a station releases a token to allow the station to modify the token according to the priority protocol.

#### receive buffer manager

The receive buffer manager controls the receive buffer chaining operations on the LAN Adapter bus.

#### receive data manager

The receive data manager requests and acknowledges LAN Adapter bus cycles for DMA to write the received frame into memory on the LAN Adapter bus.

#### receive deserializer

The receive descrializer block is a 16-bit serial-in parallel-out shift register. The input is the sampled data from the ring. A serial parity generator unit calculates the parity for each eight bits shifted in and stores this parity with the parallel data. The 18 bits of data and parity are then loaded in parallel into the receive FIFO buffer.

#### receive DMA registers

The receive DMA registers are indicated in the functional block diagram by the names RCP, RTP, RADDRO, RADDR1, RLENO, and RLEN1. These registers are managed by the receive buffer manager. Only the register RCP (receive chain pointer) may be accessed by external LAN Adapter bus masters. The remaining registers are not accessible by external bus masters. A brief description of these registers follows.

#### receive chain pointer (RCP)

This register contains the address of the buffer currently being filled with data from the ring.

#### receive temporary pointer (RTP)

The receive temporary pointer register contains the starting address of the buffer into which the receive DMA channel will store data when the buffer being used is full.

#### channel address registers (RADDR0, RADDR1)

The TMS38021 maintains two DMA channels for receive operations. The channel address register for both receive DMA channels contains the LAN Adapter bus address of the word being accessed by that channel.

#### channel length registers (RLENO, RLEN1)

The channel length register for each of the two receive DMA channels contains the number of empty bytes left in the buffer currently being filled by that channel.

#### receive FIFO

The receive first-in, first-out (FIFO) buffer stores up to two words (16 bits) of deserialized data before it is transferred via DMA onto the LAN Adapter bus. Data is transferred onto the LAN Adapter bus under control of the receive data manager block.

#### serial receive state machine

This state machine controls operation of the receiver portion of the serial data path.

#### serial transmit state machine

This state machine controls the operation of the serial transmit data path.

#### transitional-to-manchester decoder (T/M)

This functional block converts the internal transitional code representation of transmit data to Differential Manchester code.

#### transmit buffer manager

The transmit buffer manager performs the automatic buffer changing of transmit buffers contained in LAN Adapter bus memory.

#### transmit data manager

The transmit data manager requests and acknowledges LAN Adapter bus cycles for DMA to read data to be transmitted on the ring.

#### transmit DMA registers

The transmit DMA registers (TCP, TTP, TADDRO, TADDR1, TLENO, and TLEN1) are managed by the transmit buffer manager. Of these, only the transmit chain pointer (TCP) may be loaded by external LAN Adapter bus masters. The remaining registers are not accessible by external bus masters. The transmit DMA registers are described briefly below.

#### transmit chain pointer (TCP)

The transmit chain pointer contains the address of the buffer currently being read for transmit data.

#### transmit temporary pointer (TTP)

The transmit temporary pointer register contains the starting address of the buffer from which transmit data will be read by the DMA channel when the present buffer had been read.

#### channel address registers (TADDR0, TADDR1)

The TMS38021 maintains two DMA channels for transmit operations. The channel address register for both transmit DMA channels contains the LAN Adapter bus address of the word being read by that channel.

#### channel length registers (TLENO, TLEN1)

The channel length register for each of the two transmit DMA channels contains the number of bytes yet to be transmitted from the current buffer.

### transmit FIFO

The transmit FIFO buffers two 16-bit words, allowing the TMS38021 to maintain a constant flow of transmitted data into the transmit serializer. The parity from the LAN Adapter bus is maintained within the FIFO.

### transmit multiplexer

The transmit multiplexer selects either the CRC generator or transmit serializer output onto the transmit data path.

#### transmit parity checker

The transmit parity checker checks the parity of data transferred from the top of the transmit FIFO to the transmit serializer. It performs the final check of data before it is placed in the serializer.

#### transmit serializer

The transmit serializer is a 16-bit parallel-in, serial-out shift register. The shift register is loaded from the data at the top of the transmit FIFO, from the concatenation of the Start Delimiter (SDEL) and the fire token register (FTOK) or from a concatenation of the End Delimiter (EDEL) and the frame status (FS) register.

#### transmit timer

The TMS38021 contains a physical trailer timer (PTT). This timer provides a watchdog timer function for halting the frame strip process after transmitting a frame.

#### command and status registers

The command and status registers of the TMS38021 are registers which may be read/written through memory-mapped I/O by an external bus master on the LAN Adapter bus. These registers are mapped to LAN Adapter bus addresses as shown in Figure 2.

| ADDRESS | BITS            |                 | DESCRIPTION                  |

|---------|-----------------|-----------------|------------------------------|

|         | 0 7             | 8 15            |                              |

| >0100   | RINGCMD0        |                 | RING COMMAND 0               |

| >0102   | RING            | CMD1            | RING COMMAND 1               |

| >0104   | RINGSTS         |                 | RING STATUS                  |

| >0106   | INTSTAT         |                 | INTERRUPT STATUS             |

| >0108   | 00 <sup>†</sup> | PTTLATCH        | PHYSICAL TRAILER TIMER LATCH |

| >010A   | RCP             |                 | RECEIVE CHAIN POINTER        |

| >010C   | TCP             |                 | TRANSMIT CHAIN POINTER       |

| >010E   | FTOK            | 00 <sup>‡</sup> | FIRE TOKEN                   |

|         |                 |                 |                              |

<sup>&</sup>lt;sup>†</sup>Most-significant bits are reserved.

FIGURE 2. TMS38021 COMMAND AND STATUS REGISTERS

### ring command 0 (RINGCMD0)

The RINGCMD0 register enables specific receive and transmit modes of the TMS38021 including idle insertion between frames and stripping of transmitted data from the ring. The bits of RINGCMD0 are defined in Table 2.

TABLE 2. RING COMMAND 0 (RINGCMD0) REGISTER BIT FUNCTIONS

| BIT | NAME    | DESCRIPTION                      |

|-----|---------|----------------------------------|

| 0   | XMTIMM  | Transmit Imediate Mode           |

| 1   | BDM     | Baud Data Mode                   |

| 2   | NOSTRIP | No Strip Mode                    |

| 3   | XMTCRC  | Transmit CRC                     |

| 4   | RNFT    | Release No Free Token            |

| 5   | XMTIDLE | Transmit Idles Mode              |

| 6   | ETO     | Enable Transmitter Output        |

| 7   | PTEST   | Parity Test                      |

| 8   | GAP0    | Interframe Gap Bit O             |

| 9   | GAP1    | Interframe Gap Bit 1             |

| 10  | GAP2    | Interframe Gap Bit 2             |

| 11  |         | Reserved. This bit must be zero. |

| 12  |         | Reserved. This bit must be zero. |

| 13  |         | Reserved. This bit must be zero. |

| 14  |         | Reserved. This bit must be zero. |

| 15  | NOCHAIN | No Receive Chaining              |

<sup>‡</sup>Least-significant bits are reserved.

### ring command 1 (RINGCMD1)

The RINGCMD1 register is the master control register of the TMS38021. This register controls such functions as reset, clock sourcing, ring insertion, and address recognition. The bits of RINGCMD1 are defined in Table 3. The functions of receive options, ROPT0 and ROPT1, are presented in Table 4.

TABLE 3. RING COMMAND 1 (RINGCMD1) REGISTER BIT FUNCTIONS

| BIT | NAME   | DESCRIPTION                             |

|-----|--------|-----------------------------------------|

| 0   | NRESET | Not Reset                               |

| 1   | NFRAQ  | Not Frequency Acquisition               |

| 2   | INSERT | Insert Into Ring                        |

| 3   | NWRAP  | Not internal Wrap                       |

| 4   | CXMT   | Crystal Transmit Mode Select            |

| 5   | MON    | Active Monitor Mode Select              |

| 6   |        | Reserved. This bit must be set to zero. |

| 7   |        | Reserved. This bit must be set to one.  |

| 8   |        | Reserved. This bit must be set to zero. |

| 9   | IGN0   | Ignore Control 0                        |

| 10  | IGN1   | Ignore Control 1                        |

| 11  | IGN2   | Ignore Control 2                        |

| 12  | IGN3   | Ignore Control 3                        |

| 13  | ROPTO  | Receive Option 0                        |

| 14  | ROPT1  | Receive Option 1                        |

| 15  |        | Reserved.                               |

**TABLE 4. RECEIVE OPTION BIT DECODE**

| ROPTO ROPT1 |   | DESCRIPTION                                               |  |

|-------------|---|-----------------------------------------------------------|--|

| 0           | 0 | Normal frame recognition                                  |  |

| 0           | 1 | Copy only express buffer MAC frames.                      |  |

| 1           | 1 | Line Monitor Mode. (Externally matched frames are copied, |  |

|             |   | but ARI/FCI are not set.)                                 |  |

| 1           | 0 | Copy all frames                                           |  |

### ring status register (RINGSTS)

The RINGSTS register provides general ring status information, including ring interface status, error logging, and token validation. The bits of RINGSTS are defined in Table 5.

TABLE 5. RING STATUS (RINGSTS) REGISTER BIT FUNCTIONS

| BIT | NAME   | DESCRIPTION                    |

|-----|--------|--------------------------------|

| 0   | NGO    | Not Go (Signal Loss)           |

| 1   | GTDET  | Good Token Detect              |

| 2   | ATDET  | Any Token Detect               |

| 3   | WFAULT | Wire Fault                     |

| 4   | EBOUF  | Elastic Buffer Over/Under Flow |

| 5-9 |        | Reserved                       |

| 10  | MACO   | MAC Attention Code Bit 0       |

| 11  | MAC1   | MAC Attention Code Bit 1       |

| 12  | MAC2   | MAC Attention Code Bit 2       |

| 13  | MAC3   | MAC Attention Code Bit 3       |

| 14  | RIDERO | FS Rider Control Bit 0         |

| 15  | RIDER1 | FS Rider Control Bit 2         |

### interrupt status (INSTAT)

The INSTAT register contains information concerning TMS38021 interrupts. This register provides interrupt vectoring, masking, and prioritization. The bits of INSTAT are defined in Table 6. Table 7 lists the decode for bits 11 through 14 (INTCODE0 through INTCODE3).

TABLE 6. INTERRUPT STATUS (INTSTAT) REGISTER BIT FUNCTIONS

| BIT | NAME     | DESCRIPTION                             |

|-----|----------|-----------------------------------------|

| 0   | MIE      | Master Interrupt Enable                 |

| 1   |          | Reserved                                |

| 2   | EORBE    | End of Receive Buffer Interrupt Enable  |

| 3   | EOTBE    | End of Transmit Buffer Interrupt Enable |

| 4   | SLIE     | Signal Loss Interrupt Enable            |

| 5-7 |          | Reserved                                |

| 8   | IDO      | Interrupt Source ID Bit 0               |

| 9   | ID1      | Interrupt Source ID Bit 1               |

| 10  | ID2      | Interrupt Source ID Bit 2               |

| 11  | INTCODE0 | Interrupt Code Bit 0                    |

| 12  | INTCODE1 | Interrupt Code Bit 1                    |

| 13  | INTCODE2 | Interrupt Code Bit 2                    |

| 14  | INTCODE3 | Interrupt Code Bit 3                    |

| 15  | "0"      | Always zero                             |

TABLE 7. INTERRUPT CODE 0 (INTCODE0) THROUGH INTERRUPT CODE 3 (INTCODE3) DECODE

| INTCODEO | INTCODE1 | INTCODE2 | INTCODE3 | DEFINITION                   |

|----------|----------|----------|----------|------------------------------|

| 0        | 0        | 0        | 0        | Reserved                     |

| 0        | 0        | 0        | 1        | LAN Adapter Bus Parity Error |

| 0        | 0        | 1        | 0        | Token Error                  |

| 0        | 0        | 1        | 1        | Signal Loss                  |

| 0        | 1        | 0        | 0        | BURST5 Error in Frame        |

| 0        | 1        | 0        | 1        | Log Error                    |

| 0        | 1        | 1        | 0        | No Buffer Available          |

| 0        | 1        | 1        | 1        | Attention                    |

| 1        | 0        | 0        | 0        | Reserved                     |

| 1        | 0        | 0        | 1        | Receive Frame Error          |

| 1        | 0        | 1        | 0        | Transmit Frame Error         |

| 1        | 0        | 1        | 1        | Receive End of Buffer        |

| 1        | 1        | 0        | 0        | Transmit End of Buffer       |

| 1        | 1        | 0        | 1        | Receive End of Frame         |

| 1        | 1        | 1        | 0        | Transmit End of Frame        |

| 1        | 1        | 1        | 1        | No Interrupt Pending         |

#### physical trailer timer latch (PTTLATCH)

The PTTLATCH register is an 8-bit control register containing a ring-speed-specific time constant. This value is the starting value of a timer which is started following the transmission of a frame so that a lost frame condition may be detected.

#### receive chain pointer (RCP)

The RCP register contains the starting address of the buffer into which the receive DMA channel, if active, stores receive data.

#### transmit chain pointer (TCP)

The TCP register contains the starting address of the buffer into which the transmit DMA channel, if active, reads data for transmission.

### fire free token register (FTOK)

The FTOK register is used to hold the Access Control Field (AC) to be included in a token that will be generated by the TMS38021 and transmitted on the ring. Writing to the FTOK register causes a token to be released.

#### address compare registers

The TMS38021 contains 15 registers for use in comparing frame addresses. These registers are shown with their corresponding LAN Adapter bus addresses in Figure 3.

| ADDRESS       | NAME    | DESCRIPTION                   |

|---------------|---------|-------------------------------|

| >0110         | SAH     | SPECIFIC ADDRESS BITS 0-15    |

| >0112         | SAM     | SPECIFIC ADDRESS BITS 16-31   |

| >0114         | SAL     | SPECIFIC ADDRESS BITS 32-47   |

| >0116         |         | RESERVED. ALWAYS READ AS ZERO |

| >0118         | STRIPHI | STRIP ADDRESS BITS 16-31      |

| >011A         | STRIPLO | STRIP ADDRESS BITS 32-47      |

| >011C         | GNAM1   | GROUP ADDRESS BITS 16-31      |

| >011E         | GNAL    | GROUP ADDRESS BITS 32-47      |

| >0120         | GNAH    | GROUP ADDRESS BITS 0-15       |

| >0122         | >0000   | RESERVED                      |

| >0124         | >0000   | RESERVED                      |

| >0126         | >0000   | RESERVED                      |

| >0128         | >0000   | RESERVED                      |

| >012 <b>A</b> | >0000   | RESERVED                      |

| >012C         | FNAHI   | FUNCTIONAL ADDRESS BITS 0-15  |

| >012E         | FNALO   | FUNCTIONAL ADDRESS BITS 16-31 |

FIGURE 3. ADDRESS COMPARE REGISTERS

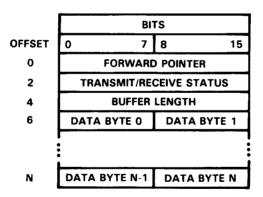

# buffer management

The TMS38021's buffer managers move frame data in and out of buffer RAM, located on the LAN Adpater bus, through one or more singly-linked buffers. These buffers are aligned on 8-byte boundaries and have the organization for transmit and receive as shown in Figure 4.

FIGURE 4. BUFFER ORGANIZATION

The forward pointer contains the address of the next buffer in a chain. The transmit/receive status field is used to report frame status. The length field contains the number of bytes in the data field of the buffer. This field is initialized by the LAN Adapter bus CPU.

#### transmit buffers

When the buffer organization shown in Figure 4 is used for transmit frames, the status field has the bit functions shown in Table 8 in the last buffer in a chain used to transmit the frame.

**TABLE 8. TRANSMIT STATUS FIELD BIT FUNCTIONS**

| BIT | NAME  | FUNCTION                          |

|-----|-------|-----------------------------------|

| 0   | INUSE | In Use Indicator                  |

| 1   | LFED  | Local Frame Error Detect          |

| 2   | RTEDI | Returned Error Detected Indicator |

| 3   | TCC0  | Transmit Completion Code Bit 0    |

| 4   | TCC1  | Transmit Completion Code Bit 1    |

| 5   | TCC2  | Transmit Completion Code Bit 2    |

| 6   | тссз  | Transmit Completion Code Bit 3    |

| 7   | EOF   | End Of Frame Indicator            |

| 8   | FS0   | Stripped Frame Status Bit 0 (ARI) |

| 9   | FS1   | Stripped Frame Status Bit 1 (FCI) |

| 10  | FS2   | Stripped Frame Status Bit 2       |

| 11  | FS3   | Stripped Frame Status Bit 3       |

| 12  | FS4   | Stripped Frame Status Bit 4 (ARI) |

| 13  | FS5   | Stripped Frame Status Bit 5 (FCI) |

| 14  |       | Reserved. This bit is zero.       |

| 15  | _     | Reserved. This bit is zero.       |

The decode function of the transmit completion code bits (TCC) is presented in Table 9.

TABLE 9. TRANSMIT COMPLETION CODE (TCC) BIT DECODE

#### PARALLEL LAN ADAPTER BUS PATH

| TCC0 | TCC1 | DESCRIPTION             |

|------|------|-------------------------|

| 0    | 0    | Normal                  |

| 0    | 1    | Parity Error            |

| 1    | 0    | DMA Underrun            |

| 1    | 1    | Next Buffer Unavailable |

### **SERIAL RING DATA PATH**

| TCC2 | тссз | DESCRIPTION            |

|------|------|------------------------|

| 0    | 0    | Normal Completion      |

| 0    | 1    | PTT Timeout            |

| 1    | 0    | Invalid Free Token     |

| 1    | 1    | Invalid Abort on Strip |

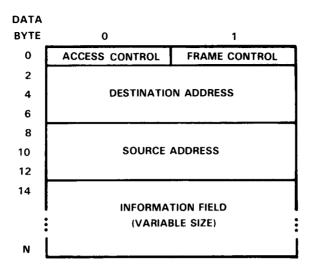

For frames to be transmitted on the ring, the data portion of a transmit buffer has the format shown in Figure 5.

FIGURE 5. TRANSMIT DATA FORMAT

#### receive buffers

When the buffer organization shown in Figure 4 is used for receive frames, the status field has the bit functions shown in Table 10 in the last buffer in a chain used to receive the frame.

TABLE 10. RECEIVE STATUS FIELD BIT FUNCTIONS

| BIT | NAME  | FUNCTION                       |

|-----|-------|--------------------------------|

| 0   | INUSE | In Use                         |

| 1   | LFED  | Local Frame Error Detect       |

| 2   | REDI  | Receive Error Detect Indicator |

| 3   | RCC0  | Receive Completion Code Bit 0  |

| 4   | RCC1  | Receive Completion Code Bit 1  |

| 5   | RCC2  | Receive Completion Code Bit 2  |

| 6   | RCC3  | Receive Complation Code Bit 3  |

| 7   | EOF   | End of Frame Indicator         |

| 8   | FS0   | Receive Frame Status Bit 0     |

| 9   | FS1   | Receive Frame Status Bit 1     |

| 10  | FS2   | Receive Frame Status Bit 2     |

| 11  | FS3   | Receive Frame Status Bit 3     |

| 12  | FS4   | Receive Frame Status Bit 4     |

| 13  | FS5   | Receive Frame Status Bit 5     |

| 14  |       | Reserved                       |

| 15  |       | Reserved                       |

The decoded function of the receive completion code bits (RCC) is presented in Table 11.

#### TABLE 11. RECEIVE COMPLETION CODE (RCC) BIT DECODE

### PARALLEL LAN ADAPTER BUS PATH

### **SERIAL RING DATA PATH**

| RCC0 | RCC1 | DESCRIPTION             |

|------|------|-------------------------|

| 0    | 0    | Normal Completion       |

| 0    | 1    | Parity Error            |

| 1    | 0    | DMA Overrun             |

| 1    | 1    | Next Buffer Unavailable |

| RCC2 | RCC3 | DESCRIPTION        |

|------|------|--------------------|

| 0    | 0    | Normal Completion  |

| 0    | 1    | Error: FCI not set |

| 1    | 0    | Implicit Abort     |

| 1    | 1    | Explicit Abort     |

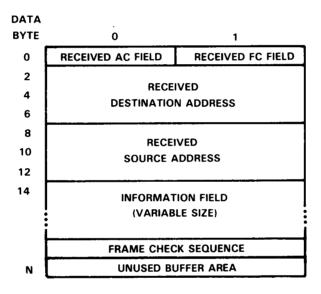

For frames received from the ring, the data portion of a receive buffer has the format shown in Figure 6.

FIGURE 6. RECEIVE DATA FORMAT

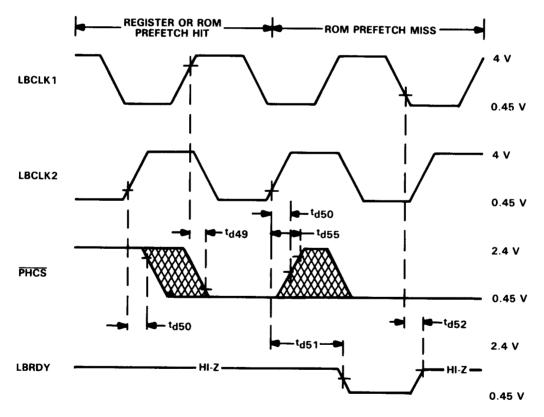

#### TMS38021 ROM

The TMS38021 contains a 16K-byte ROM organized as 8K x 18 bits. Each byte contains an odd parity bit. The ROM is not used by internal TMS38021 logic but is accessed by the LAN Adapter bus CPU for program storage. This ROM contains object code for the TMS38010 Communications Processor. This ROM contains software which provides media access protocols compatible with IEEE Std 802.5-1985, protocol services for network management servers, and diagnostics which verify proper functionality of the TMS380 Token Ring Adapter.

Access to this ROM from the TMS38010 Communications Processor is in one or two LAN Adapter bus read cycles. A prefetch unit reads the word sequentially following the last word read so that sequential accesses occur with no wait states forced on the TMS38010. When access is nonsequential, the TMS38021 deasserts LBRDY in the first cycle to force the CPU to accept a wait state. On the second cycle, the TMS38021 asserts LBRDY and places the ROM data on the bus.

When the TMS38021 is a bus slave, it will also respond if external circuitry deasserts LBRDY; it will continuously drive its output data (on reads) or delay modifying its internal register (on writes) until LBRDY is asserted high.

### address decoding

The TMS38021 performs decoding of LAN Adapter bus addresses as shown in Table 13. Note that not all addresses are strictly decoded. For example, the TMS38021 does not decode address line A1 for ROM accesses at >C000. Thus, a memory read at address location >8000 is identical to an address read at location >C000. For this reason, expansion RAM on the LAN Adapter bus should negate PHCS whenever expansion RAM overlays memory addresses >8000 through >BFFF.

| PHCS | AO | A1 | A2 | А3 | A4 | A5 | A6 | A7     | A8     | A9   | A10 | A11 | A12  | A13  | A14 | SELECTED TMS38021 LOCATION |

|------|----|----|----|----|----|----|----|--------|--------|------|-----|-----|------|------|-----|----------------------------|

| Н    | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х      | Х      | Х    | Х   | Х   | Х    | Х    | х   | TMS38021 not selected      |

| L    | L  | L  | L  | L  | L  | L  | Ł  | L      | X      | Х    | X   | Х   | X    | X    | ×   | TMS38021 not selected      |

| L    | L  | L  | L  | L  | L  | L  | L  | Н      | Х      | Х    | L   | L   | Int' | Deco | ode | Command/Status Registers   |

| L    | L  | L  | L  | L  | L  | L  | L  | Н      | X      | Х    | L   | Н   | Int' | Deco | ode | Address Compare Registers  |

| L    | L  | L  | L  | L  | L  | L  | L  | Н      | X      | Х    | Н   | L   | Int' | Dec  | ode | Compare Address Registers  |

| L    | L  | L  | L  | L  | L  | L  | L  | Н      | Х      | Х    | Н   | Н   | Int' | Dec  | ode | Internal Test Registers    |

| L    | L  | Х  | Х  | X  | Х  | X  | Н  | X      | Х      | X    | X   | X   | X    | Χ    | х   | TMS38021 not selected      |

| L    | L  | Х  | Х  | Х  | Х  | Н  | X  | Х      | Х      | Х    | X   | Х   | X    | X    | х   | TMS38021 not selected      |

| L    | L  | Х  | Х  | Х  | Н  | X  | X  | Х      | Х      | Х    | X   | Х   | X    | Х    | х   | TMS38021 not selected      |

| L    | L  | X  | Х  | Н  | Х  | X  | Х  | Х      | Х      | Х    | Х   | X   | X    | Х    | х   | TMS38021 not selected      |

| L    | L  | Х  | Н  | Х  | Х  | X  | Х  | Х      | Х      | Х    | Х   | Х   | Х    | Х    | х   | TMS38021 not selected      |

| L    | L  | Н  | X  | Х  | Х  | Х  | Х  | Х      | Х      | Х    | Х   | Х   | Х    | Х    | х   | TMS38021 not selected      |

| Ĺ    | Н  | Х  | •  |    |    |    |    | Interr | nal De | code |     |     |      |      | -   | TMS38021 ROM               |

TABLE 13. TMS38021 ADDRESS DECODING

### test mode

The TMS38021 features a module-in-place test mode for board-level testing with the TMS38021 in-circuit. This facilitates testing by bed-of-nails testers. This test mode is enabled by tying the PHTEST pin (pin 41) to ground. This has the effect of driving all outputs of the TMS38021 to a high-impedance state. When not used for testing purposes, this pin should be left unconnected. An internal pullup drives this pin high when not externally connected.

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted) $^{\dagger}$

| Supply voltage, VCC (see Note 1)                  | 7 V              |

|---------------------------------------------------|------------------|

| Input voltage range                               | -0.3~V to $20~V$ |

| Output voltage range                              | 2 V to 7 V       |

| Operating free-air temperature range (see Note 2) | 0°C to 70°C      |

| Storage temperature range                         | -65°C to 150°C   |

<sup>†</sup>Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the "Recommended Operating Conditions" section of this specification is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. Voltage values are with respect to VSS.

2. Devices are tested in an environment in excess of 70 °C to guarantee operation at 70 °C. Case temperatures should be maintained at or below 80 °C.

## recommended operating conditions

|     |                                         |                               | MIN | NOM | MAX   | UNIT |

|-----|-----------------------------------------|-------------------------------|-----|-----|-------|------|

| Vcc | Supply voltage                          |                               | 4.5 | 5   | 5.5   | V    |

| Vss | Supply voltage (Note 3)                 |                               |     | 0   |       | V    |

|     |                                         | LBCLK1, LBCLK2                | 3.8 |     |       | V    |

|     | Nich lavel inner valence                | RCVR, RCLK                    | 2.6 |     |       | ٧    |

| VIH | High-level input voltage                | PHTEST                        | Vcc |     |       | ٧    |

|     |                                         | All other inputs              | 2   |     |       | V    |

| V   | V <sub>IL</sub> Low-level input voltage | LBCLK1, LBCLK2,<br>RCVR, RCLK |     |     | 0.6   | ٧    |

| ۷ĮĽ |                                         | PHTEST                        |     | -   | VSS   | V    |

|     |                                         | All other inputs              |     |     | 0.8   | V    |

| ЮН  | High-level output current               | All outputs                   |     |     | 0.15  | mA   |

|     |                                         | DRVR                          |     |     | -1.2  | mA   |

| lOL | Low-level output current                | LBRDY                         |     |     | - 2.4 | mA   |

|     |                                         | All other outputs             |     |     | - 1.7 | mA   |

|     | 1 4                                     | DRVR                          |     |     | 30    | pF   |

| CL  | Load capacitance                        | All other outputs             |     |     | 100   | pF   |

| TA  | Operating free-air temperature (        | Note 2)                       | 0   |     | 70    | °C   |

- NOTES: 2. Devices are tested in an environment in excess of 70 °C to guarantee operation at 70 °C. Case temperatures should be maintained at or below 80 °C.

- 3. Care should be taken by PC board designers to provide a minimum inductance path between the VSS pins and system ground in order to minimize VSS noise.

# electrical characteristics over full range of recommended operating conditions (unless otherwise noted)

|      | PAR                                                                             | AMETER                                  | TEST<br>CONDITIONS                                       | MIN | ТҮР | MAX           | UNIT     |

|------|---------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------------------------|-----|-----|---------------|----------|

| Vон  | High-level<br>output voltage                                                    | All outputs                             | $V_{CC} = 4.5 \text{ V},$ $I_{OH} = 0.15 \text{ mA}$     | 2.4 |     |               | ٧        |

| VOL  | Low-level output voltage                                                        | All outputs                             | $V_{CC} = 4.5 V$ , $I_{OL} = Max$                        |     |     | 0.45          | ٧        |

| ЮН   | High-level output current                                                       | All outputs                             | $V_{CC} = 4.5 \text{ V},$<br>$V_{OH} = 2.4 \text{ V}$    |     |     | 0.15          | mA       |

| lOL  | Low-level output current                                                        | DRVR<br>LBRDY                           | V <sub>CC</sub> = 4.5 V,<br>V <sub>OL</sub> = 0.45 V     |     |     | -1.2<br>-2.4  | mA<br>mA |

| lOZL | Off-state (high-impedance output current with low-levoltage applied, outputs a  | evel                                    | V <sub>O</sub> = 0.45 V                                  |     |     | - 1.7<br>- 50 | mA<br>μA |

| lozh | Off-state (high-impedance output current with high-livoltage applied, outputs a | state)<br>evel                          | V <sub>O</sub> = 2.4 V                                   |     |     | 50            | μΑ       |

| IIL  | Low-level                                                                       | PHTEST (Note 4)                         | V <sub>I</sub> = V <sub>SS</sub> ,<br>V <sub>CC</sub> at |     |     | - 700         | μΑ       |

|      | input current                                                                   | All other inputs                        | 4.75 V - 5.25 V                                          |     |     | - 20          | μΑ       |

| ΉΗ   | High-level input current                                                        | All other inputs except PHTEST (Note 5) | V <sub>CC</sub> at<br>4.5 V - 5.5 V                      |     |     | 20            | μΑ       |

|      |                                                                                 |                                         | $V_{CC} = 5 V,$ $T_A = 25 ^{\circ}C$                     |     | 110 |               | μΑ       |

| Icc  | Supply current                                                                  |                                         | $V_{CC} = 5.5 \text{ V},$ $T_A = 0 ^{\circ}C$            |     |     | 175           | μΑ       |

|      |                                                                                 |                                         | $V_{CC} = 5.5 \text{ V},$ $T_{C} = 80 ^{\circ}\text{C}$  |     | 125 | μΑ            |          |

|      | Innut                                                                           | LBCLK1, LBCLK2                          | f = 1 MHz,                                               |     |     | 20            | pF       |

| Cį   | Input<br>capacitance                                                            | RCVR, RCLK                              | all other                                                |     |     | 10            | pF       |

|      | capacitanice                                                                    | All other inputs                        | inputs at 0 V                                            |     |     | 15            | pF       |

NOTES: 4. PHTEST has an internal pullup resistor implemented. It may be left unconnected; in this case it is interpreted as high.

<sup>5.</sup> I<sub>IH</sub> for PHTEST is not specified because it will never be driven.

# LAN ADAPTER BUS CLOCK PARAMETERS

timing requirements over recommended supply voltage range and operating free-air temperature range (see Figure 7)

|                     |                                                              | MIN     | MAX           | UNIT |

|---------------------|--------------------------------------------------------------|---------|---------------|------|

| t <sub>C</sub> (LA) | LAN Adapter bus cycle time (Note 6)                          | 333     | 333.7         |      |

| t <sub>d1</sub>     | Delay time, LBCLK2 low to LBCLK2 no longer low in next cycle | 4Q 2    | 4Q + 2        |      |

| t <sub>d2</sub>     | Delay time, LBCLK2 rise to LBCLK2 high in next cycle         |         | 4Q + 9        |      |

| t <sub>d</sub> 3    | Delay time, LBCLK2 no longer low to LBCLK1 no longer low     | Q-3     | Q+3           |      |

| t <sub>d4</sub>     | Delay time, LBCLK2 rise to LBCLK1 high                       |         | Q+9           |      |

| <sup>t</sup> d5     | Delay time, LBCLK2 no longer low to LBCLK2 no longer high    | 20 – 2  | 2Q + 7        |      |

| td6                 | Delay time, LBCLK2 rise to LBCLK2 low                        |         | 20+12         | ns   |

| td7                 | Delay time, LBCLK2 no longer low to LBCLK1 no longer high    | 3Q – 15 | <b>3Q</b> – 1 |      |

| t <sub>d</sub> 8    | Delay time, LBCLK2 rise to LBCLK1 low                        |         | 30            |      |

| t <sub>d</sub> 9    | Delay time, LBCLK1 low to LBCLK2 high                        | Q       |               |      |

| td10                | Delay time, LBCLK2 high to LBCLK1 high                       | Q-4     |               |      |

| td11                | Delay time, LBCLK1 high to LBCLK2 low                        | Q-4     |               |      |

| td12                | Delay time, LBCLK2 low to LBCLK1 low                         | Q-16    |               |      |

NOTES: 6. The LAN Adapter bus cycle time is 333.3 ns ± 0.1%. This value shall be used for calculations requiring the time between successive rising edges of LBCLK2.

7. Q = 0.25  $t_{c(LA)}$ .

# LAN ADAPTER BUS READ AND WRITE PARAMETERS

timing requirements/switching characteristics over recommended supply voltage range and operating free-air temperature range (see Figure 7)  $^{\dagger}$

|                   |                                                                                   | MIN    | MAX     | U |

|-------------------|-----------------------------------------------------------------------------------|--------|---------|---|

| td13              | Delay time, LBCLK2 rise to LI/D valid                                             |        | 47      |   |

| t <sub>d14</sub>  | Delay time, LBCLK2 rise to LAL high                                               |        | 47      | 1 |

| <sup>t</sup> d15  | Delay time, LBCLK2 rise to address valid                                          |        | 47      |   |

| <sup>t</sup> d16  | Delay time, LBCLK2 rise to LR/W valid                                             |        | 47      | ] |

| twH1              | Pulse duration, LAL high                                                          | Q - 50 |         |   |

| td17              | Delay time, address valid to LAL no longer high                                   | Q - 50 |         | 1 |

| <sup>t</sup> d18  | Delay time, LAL fall to 1.3 V to address no longer valid                          | 7      |         |   |

| t <sub>d19</sub>  | Delay time, LBCLK1 high to address no longer valid                                | 7      |         |   |

| <sup>t</sup> d20  | Delay time, LBCLK2 rise to LAD, LPH, LPL high impedance in read cycle             |        | Q + 74  |   |

| <sup>t</sup> d21  | Delay time, LAD, LPH, LPL high impedance to LEN no longer high in read cycle      | 0      |         |   |

| t <sub>d22</sub>  | Delay time, LBCLK2 rise to LEN low in read cycle                                  |        | Q + 84  |   |

| t <sub>d23</sub>  | Delay time, LBCLK2 rise to LEN low in write cycle                                 |        | Q+47    |   |

| t <sub>d24</sub>  | Delay time, LBCLK1 low to LEN no longer low in read cycle                         | 0      |         |   |

| td25              | Delay time, LBCLK2 rise to LEN high in read cycle                                 |        | 3Q + 47 | ĺ |

| td26              | Delay time, LBCLK2 rise to LAL low                                                |        | 2Q - 12 |   |

| td27              | Delay time, LBCLK1 low to LAD, LPH, LPL no longer high impedance in next cycle    | 80     |         |   |

| <sup>t</sup> d28  | Delay time, LBCLK2 rise to write data valid                                       |        | 3Q - 70 |   |

| td29              | Delay time, LBCLK1 low to LI/ $\overline{D}$ , LR/ $\overline{W}$ no longer valid | 20     |         |   |

| td30              | Delay time, LBCLK1 low to write data no longer valid                              | 20     |         |   |

| <sup>t</sup> d31  | Delay time, LBCLK1 low to LEN no longer low in write cycle                        | 20     |         |   |

| t <sub>d32</sub>  | Delay time, LBCLK1 low to LEN high in write cycle                                 |        | 80      |   |

| t <sub>d</sub> 33 | Delay time, LBCLK2 rise to LEN no longer high in write cycle                      | Q-4    |         |   |

| t <sub>su</sub> 1 | Setup time, read data valid to LBCLK1 no longer high                              | 20     |         |   |

| t <sub>h1</sub>   | Hold time, read data valid after LBCLK1 low if th2 not met                        | 15     |         |   |

| th2               | Hold time, read data valid after LEN no longer low if th1 not met                 | 0      |         |   |

| <sup>t</sup> d34  | Delay time, LBCLK2 rise to LBRDY high                                             |        | 2Q - 41 |   |

| t <sub>d</sub> 35 | Delay time, LBCLK2 rise to LBRDY low                                              |        | 2Q – 21 |   |

| th3               | Hold time, LBRDY valid after LBCLK2 low                                           | 80     |         |   |

<sup>&</sup>lt;sup>†</sup>This table is entitled switching characteristics/timing requirements because several of the parameters specified can be classified as characteristics or requirements depending on the mode of operation: bus slave or bus master (DMA). The values given are valid for both modes. NOTE 7: Q = 0.25t<sub>C</sub>(LA).

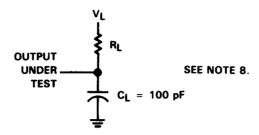

# PARAMETER MEASUREMENT INFORMATION

NOTE 8: RL and VL are chosen as follows:

$$R_{L} = \frac{V_{OH} - V_{OL}}{|I_{OL} - I_{OH}|} V_{L} = V_{OH} - (I_{OH}) (R_{L})$$

FIGURE 7. LOAD CIRCUIT

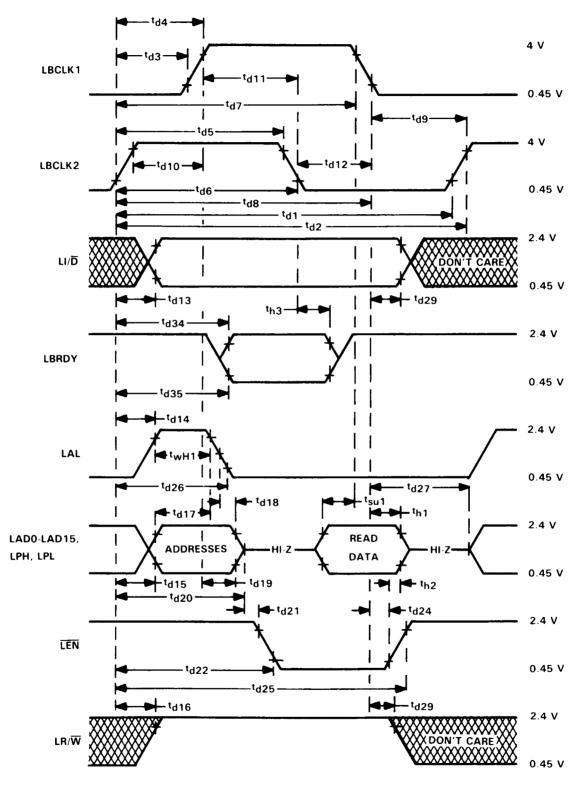

# LAN Adapter bus read timing

NOTE 9: The timing reference points for LBCLK1 and LBCLK2 are 3 V and 0.8 V. The timing reference points for the other waveforms are 2 V and 0.8 V. The intermediate reference point for LAL is 1.3 V.

# LAN Adapter bus write timing

NOTE 9: The timing reference points for LBCLK1 and LBCLK2 are 3 V and 0.8 V. The timing reference points for the other waveforms are 2 V and 0.8 V. The intermediate reference point for LAL is 1.3 V.

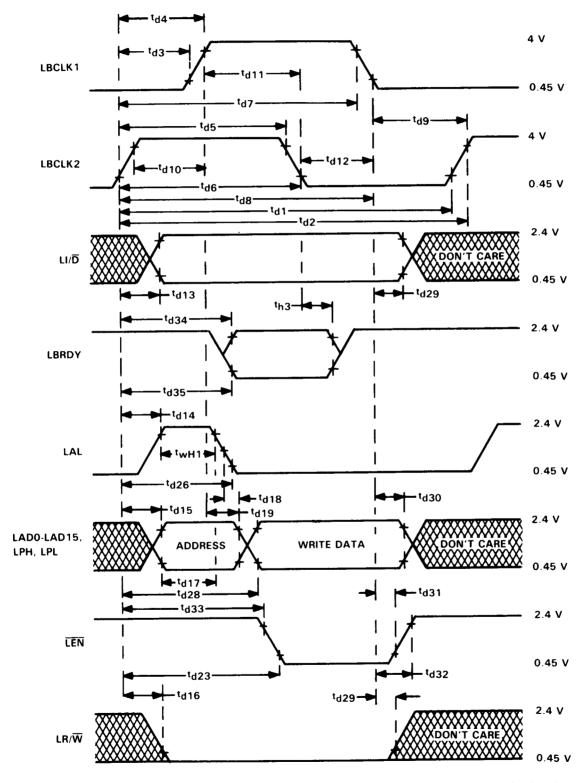

# LAN ADAPTER BUS ARBITRATION PARAMETERS

# switching requirements over recommended supply voltage range and operating free-air temperature range (see Figure 7)

|                   | PARAMETER                                                                     | MIN  | MAX     | UNIT |

|-------------------|-------------------------------------------------------------------------------|------|---------|------|

| t <sub>d</sub> 36 | Delay of LBRQP from LBCLK1 low                                                |      | 48      |      |

| td37              | Delay of LBRQP after LBCLK1 high                                              | 0    |         |      |

| t <sub>d</sub> 38 | Delay time, LBCLK2 rise to LAL no longer high impedance by TMS38021           | 20-9 |         |      |

| td39              | Delay time, LBCLK2 rise to LAL driven low by TMS38021                         |      | 3Q - 15 | ns   |

| <sup>t</sup> d40  | Delay time, LBCLK1 low to LEN no longer high impedance by TMS38021            | 80   |         |      |

| t <sub>d41</sub>  | Delay time, LBCLK2 rise to LEN driven high by TMS38021                        |      | 74      |      |

|                   | Delay time, LBCLK1 low to LR/W, LI/D, LADO-LAD15, LPH, and LPL no longer high |      |         |      |

| <sup>t</sup> d42  | impedance by TMS38021                                                         | 80   |         |      |

NOTE 7:  $Q = 0.25t_{C(LA)}$

# timing requirements over recommended supply voltage range and operating free-air temperature range

|                   |                                                                               | MIN     | MAX     | UNIT |

|-------------------|-------------------------------------------------------------------------------|---------|---------|------|

| <sup>t</sup> d43  | Delay time, LBCLK2 rise to LBGRP valid                                        |         | 2Q - 73 |      |

| td44              | Delay time, LBCLK2 rise to LBGRP no longer valid                              | -6      |         |      |

| t <sub>d</sub> 45 | Delay time, LBCLK2 rise to LAL no longer driven low from old bus master       | 3Q - 15 |         |      |

| t <sub>d46</sub>  | Delay time, LBCLK2 rise to LAL high impedance from old bus master             |         | 4Q - 2  | ns   |

| <sup>t</sup> d47  | Delay time, LBCLK2 rise to LEN high impedance from old bus master             |         | 74      |      |

| *                 | Delay time, LBCLK1 low to LR/W, LI/D, LADO-LAD15, LPH, and LPL high impedance |         |         |      |

| td48              | from old bus master                                                           |         | 80      |      |

NOTE 7: Q =  $0.25t_{c(LA)}$ .

# LAN Adapter bus arbitration

NOTE 10: The timing reference points for LBCLK1 and LBCLK2 are 3 V and 0.8 V. The timing reference points for the other waveforms are 2 V and 0.8 V.

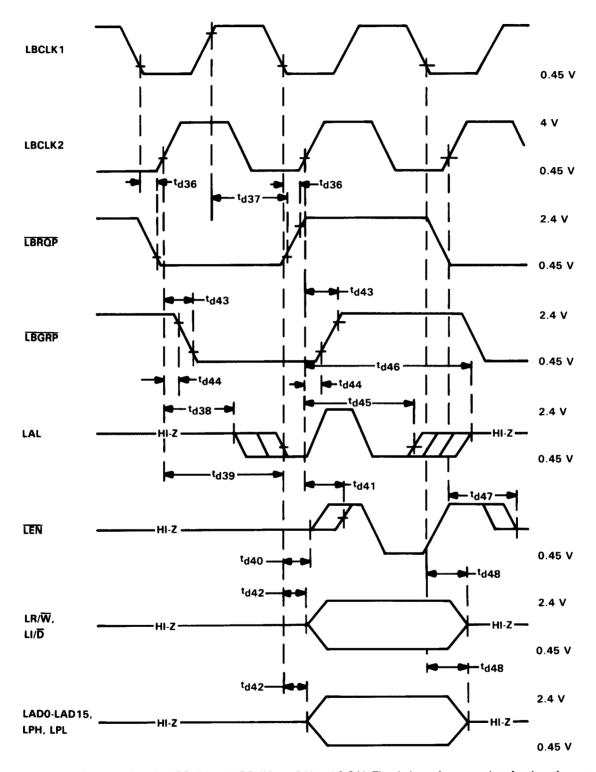

# MISCELLANEOUS LAN ADAPTER BUS PARAMETERS

# timing requirements over recommended supply voltage range and operating free-air temperature range

|                   |                                                                        | MIN | MAX | UNIT |

|-------------------|------------------------------------------------------------------------|-----|-----|------|

| t <sub>d</sub> 49 | Delay time, LBCLK1 high to PHCS low                                    |     | 10  |      |

| <sup>t</sup> d50  | Delay time, LBCLK2 rise to PHCS no longer valid                        | 0   |     |      |

| <sup>t</sup> d51  | Delay time, LBCLK2 rise to LBRDY driven low in ROM prefetch miss       |     | 145 |      |

| <sup>t</sup> d52  | Delay time, LBCLK1 low to LBRDY high impedance after ROM prefetch miss |     | 45  | ns   |

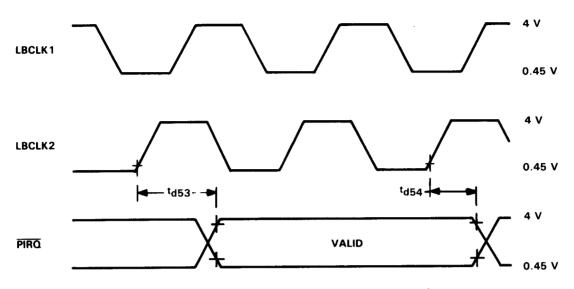

| t <sub>d53</sub>  | Delay time, LBCLK2 rise to PIRQ valid                                  |     | 60  |      |

| <sup>t</sup> d54  | Delay time, LBCLK2 rise to PIRQ no longer valid                        | 0   |     |      |

| <sup>t</sup> d55  | Delay time, LBCLK2 rise to PHCS high                                   |     | Q-3 |      |

NOTE 7: Q =  $0.25 t_{C(LA)}$

# **PHCS** and LBRDY timing

NOTE 10: The timing reference points for LBCLK1 and LBCLK2 are 3 V and 0.8 V. The timing reference points for the other waveforms are 2 V and 0.8 V.

# interrupt timing

**MISCELLANEOUS TIMING PARAMETERS**

# timing requirements over recommended supply voltage range and operating free-air temperature range

|                  |                                                                                         | MIN | MAX | UNIT |

|------------------|-----------------------------------------------------------------------------------------|-----|-----|------|

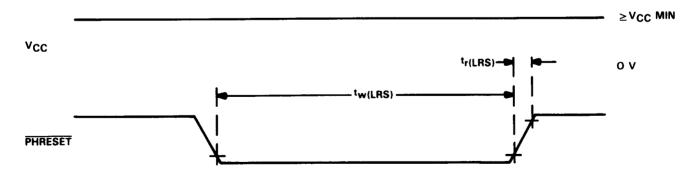

| tw(LRS)          | PHRESET pulse duration, asserted with minimum V <sub>CC</sub> or greater applied        | 14  |     | μS   |

| tr(LRS)          | PHRESET rise time                                                                       |     | 100 | nş   |

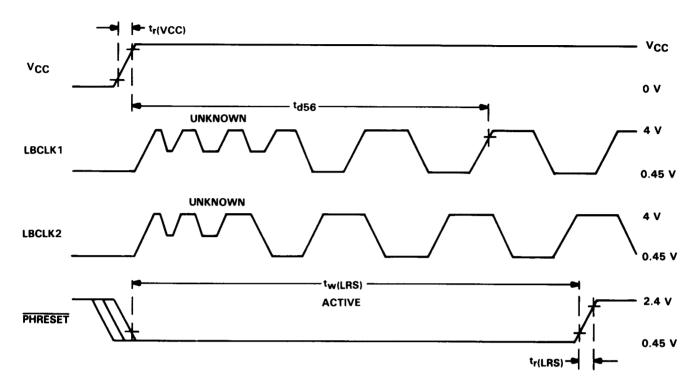

| tr(VCC)          | V <sub>CC</sub> rise time from 1.2 V to V <sub>CC</sub> minimum                         | 1   |     | ms   |

| <sup>t</sup> d56 | Delay from reading minimum V <sub>CC</sub> during power-up to valid LBCLK1, LBCLK2 with |     | 90  | ms   |

|                  | PHRESET active                                                                          |     |     |      |

# **PHRESET** timing

# power-up, LBCLK, and PHRESET timing

NOTE 11: The timing reference points for V<sub>CC</sub> are 4.5 V and 1.2 V. The timing reference points for LBCLK1 and LBCLK2 are 3 V and 0.8 V. The timing reference points for PHRESET are 2 V and 0.8 V

# EXTERNAL COPY HARDWARE INTERFACE (XMATCH, XFAIL)

# timing requirements over recommended supply voltage range and operating free-air temperature range

|       |                                                                            | MIN | NOM | MAX | UNIT |

|-------|----------------------------------------------------------------------------|-----|-----|-----|------|

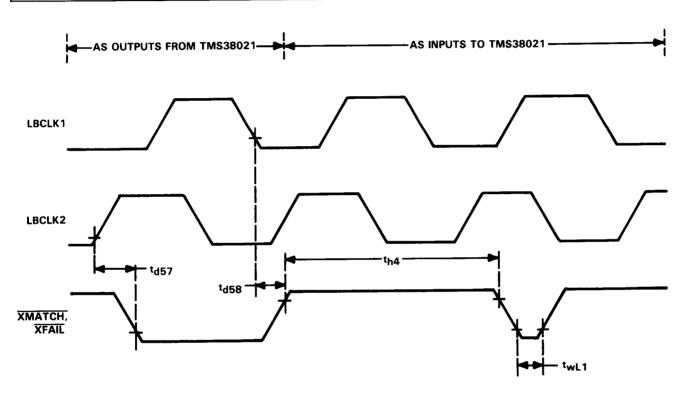

| th4   | Hold time, XMATCH, XFAIL inactive-high after driven as outputs by TMS38021 |     |     | 6Q  | ns   |

| twl 1 | Pulse duration low, XMATCH, XFAIL                                          | 50  |     |     | ns   |

# switching characteristics over recommended supply voltage range and free-air temperature range

|                  | PARAMETER                                                                    | MIN | TYP | MAX | UNIT |

|------------------|------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>d57</sub> | Delay time, LBCLK2 no longer low to XMATCH, XFAIL low when driven as outputs |     |     | 47  | ns   |

| td58             | Delay time, LBCLK1 low to XMATCH, XFAIL no longer valid.                     | 20  |     |     | ns   |

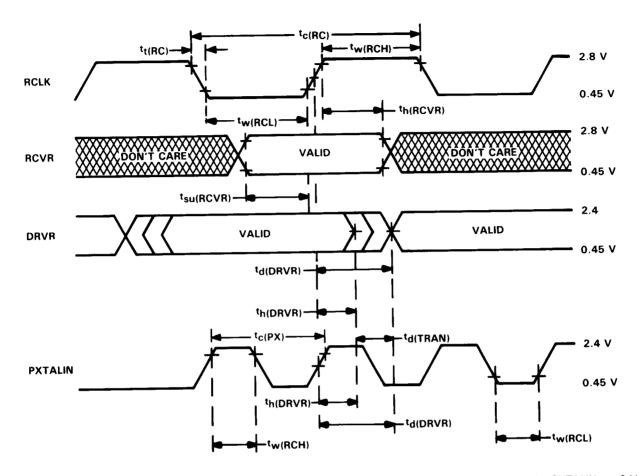

### RING INTERFACE TIMING PARAMETERS

# timing requirements over recommended supply voltage range and operating free-air temperature range

|                        |                                                          | MIN     | MAX     | UNIT |

|------------------------|----------------------------------------------------------|---------|---------|------|

| t <sub>c</sub> (RC)    | RCLK cycle time (Note 14)                                | 124.875 | 125.125 |      |

| t <sub>C</sub> (PX)    | PXTALIN cycle time                                       | 124.875 | 125.125 | 1    |

| tw(RCL)                | Pulse duration, RCLK and PXTALIN low (Notes 15, 16, 17)  | 46      |         | 1    |

| tw(RCH)                | Pulse duration, RCLK and PXTALIN high (Notes 15, 16, 17) | 35      |         | ns   |

| t <sub>su</sub> (RCVR) | Setup time, RCVR valid before RCLK no longer low         | 20      |         | 1    |

| th(RCVR)               | Hold time, RCVR valid after RCLK high                    | 20      |         |      |

| tt(RC)                 | Transition time, RCLK and PXTALIN                        |         | 16      |      |

NOTES: 14. The nominal value for  $t_{c(RC)}$  is 125 ns  $\pm$  0.1%.

- 15. The nominal value for  $t_{\mathbf{W}(RCL)}$  and  $t_{\mathbf{W}(RCH)}$  is 62.5 ns.

- 16. RCVR and RCLK are driven to a high level of 2.8 V and a low level of 0.45 V during parametric tests. Timing parameters are measured from a high level of 2.6 V and a low level of 0.6 V except where shown otherwise.

- 17. PXTALIN is driven to a high level of 2.4 V and a low level of 0.45 V during parametric tests. Timing parameters are measured from a high level of 2 V and a low level of 0.8 V.

# switching characteristics over recommended supply voltage range and operating free-air temperature range

|                      | PARAMETER                                                                          | MIN | MAX | UNIT |

|----------------------|------------------------------------------------------------------------------------|-----|-----|------|

| th(DRVR)             | Hold time, DRVR after RCLK or PXTALIN to 1.5 V level (Note 18)                     | 12  |     |      |

| <sup>t</sup> d(DRVR) | Delay time, RCLK or PXTALIN at 1.5 V level to DRVR at 1.5 V (Note 18)              |     | 40  | ns   |

| td(TRAN)             | Delay time, data transition on DRVR (t <sub>d(DRVR)</sub> - t <sub>h(DRVR)</sub> ) |     | 5   |      |

NOTE: 18. Timing parameters of DRVR are measured from a 1.5 V level on RCLK or PXTALIN to a 1.5 V level on DRVR.

# ring interface timing

NOTE 19: The timing reference points for RCVR and RCLK are 2.6 V and 0.6 V. The timing reference points for PXTALIN are 2 V and 0.8 V. The intermediate reference point for RCLK and DRVR is 1.5 V.